概述

在芯片的资料上,有两个非常特殊的寄存器配置位,分别是 CPOL (Clock POlarity)和 CPHA (Clock PHAse)。

CPOL配置SPI总线的极性

CPHA配置SPI总线的相位

极性和相位,这么专业的名词,非常难理解。我们不妨从时序图入手,了解极性和相位的效果。

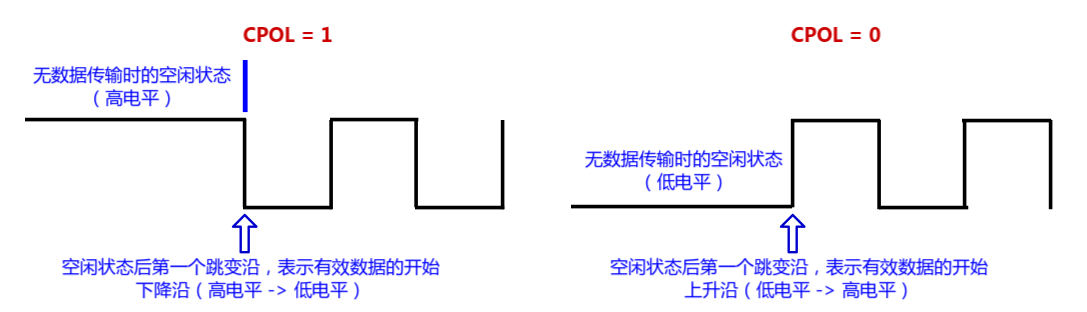

SPI总线的极性

极性,会直接影响SPI总线空闲时的时钟信号是高电平还是低电平。

CPOL = 1:表示空闲时是高电平

CPOL = 0:表示空闲时是低电平

由于数据传输往往是从跳变沿开始的,也就表示开始传输数据的时候,是下降沿还是上升沿。

如下图:

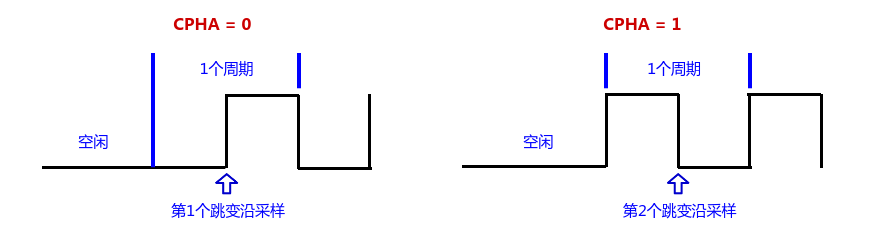

SPI总线的相位

一个时钟周期会有2个跳变沿。而相位,直接决定SPI总线从那个跳变沿开始采样数据。

CPHA = 0:表示从第一个跳变沿开始采样

CPHA = 1:表示从第二个跳变沿开始采样

不多说,直接上图:

至于跳变沿究竟是上升沿还是下降沿,这取决于 CPOL。记住, CPHA 只决定是哪个跳变沿采样。

4种模式

CPOL 和 CPHA 的不同组合,形成了SPI总线的不同模式。

| mode | CPOL | CPHA |

|---|---|---|

| mode 0 | 0 | 0 |

| mode 1 | 0 | 1 |

| mode 2 | 1 | 0 |

| mode 3 | 1 | 1 |

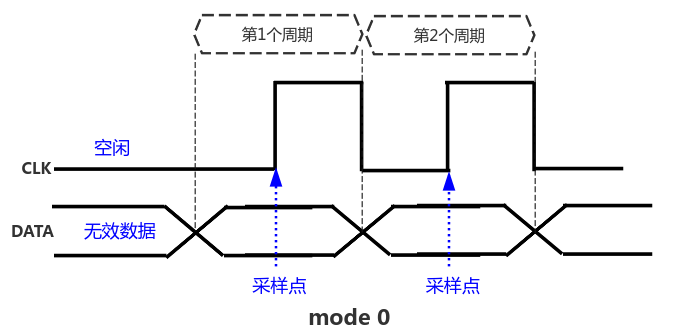

模式0 (CPOL=0; CPHA=0)

特性:

CPOL = 0:空闲时是低电平,第1个跳变沿是上升沿,第2个跳变沿是下降沿

CPHA = 0:数据在第1个跳变沿(上升沿)采样

效果图:

模式1 (CPOL=0; CPHA=1)

特性:

CPOL = 0:空闲时是低电平,第1个跳变沿是上升沿,第2个跳变沿是下降沿

CPHA = 1:数据在第2个跳变沿(下降沿)采样

效果图:

模式2 (CPOL=1; CPHA=0)

特性:

CPOL = 1:空闲时是高电平,第1个跳变沿是下降沿,第2个跳变沿是上升沿

CPHA = 0:数据在第1个跳变沿(下降沿)采样

效果图:

模式3 (CPOL=1; CPHA=1)

特性:

CPOL = 1:空闲时是高电平,第1个跳变沿是下降沿,第2个跳变沿是上升沿

CPHA = 1:数据在第2个跳变沿(上升沿)采样

效果图: