参考网址

https://github.com/espressif/esp-iot-solution/tree/master/examples/eth2wifi

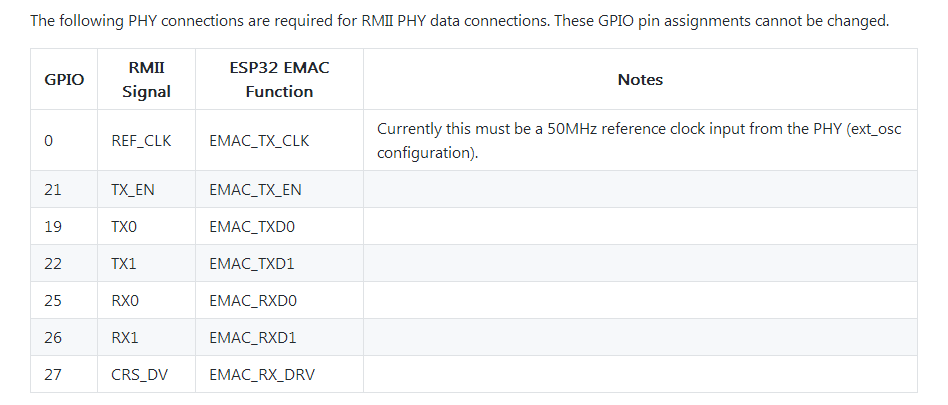

RMII PHY Wiring(RMII接口物理层连接):

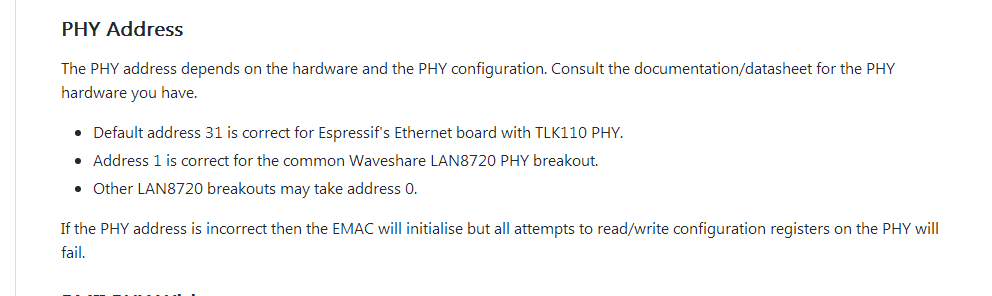

物理层地址:

关键点:

Because GPIO0 is a strapping pin for entering UART flashing mode on reset, care must be taken when also using this pin as EMAC_TX_CLK. If the clock output from the PHY is oscillating during reset, the ESP32 may randomly enter UART flashing mode. One solution is to use an additional GPIO as a "power pin", which either powers the PHY on/off or enables/disables the PHY's own oscillator. This prevents the clock signal from being active during a system reset. For this configuration to work, GPIO0 also needs a pullup resistor and the "power pin" GPIO will need a pullup/pulldown resistor - as appropriate in order to keep the PHY clock disabled when the ESP32 is in reset. See the example source code to see how the "power pin" GPIO can be managed in software. The example defaults to using GPIO 17 for this function, but it can be overriden. On Espressif's Ethernet development board, GPIO 17 is the power pin used to enable/disable the PHY oscillator.

翻译: 要实现这个功能要外接50Mhz的晶振作为参考时钟,连接的是GPIO0,但是这个脚也是用作配置flash下载模式的,所以再在ESP32中引脚中选出一个引脚用于打开和关闭外部的晶振(本例子采用的是GPIO17)。(这里就使用有源晶振 )(STM32使用的是无源晶振+匹配电容)