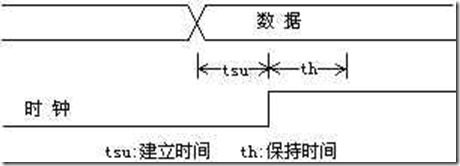

建立时间(setup time)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;

保持时间(hold time)是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器。

如下图所示:

有一点需要说明,某器件中触发器的建立时间和保持时间的下限,是由器件的半导体工艺决定的;建立时间保持时间的上限,则与传输延时等因素有关。

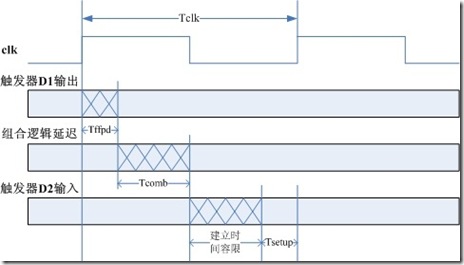

(1)建立时间的上限

如下图所示:

图中,Tffpd即Tco,Tcomb即Tdelay,而且没有考虑时钟延时Tpd。假如把上述因素都考虑进去,由上图可知,建立时间容限+Tffpd(max)+Tcomb(max)+Tsetup-Tpd=Tclk,

根据建立时间容限≥0,也就是Tclk+Tpd-Tffpd(max)-Tcomb(max)-Tsetup≥0,可以得到触发器D2的Tsetup≤Tclk+Tpd-Tffpd(max)-Tcomb(max)。

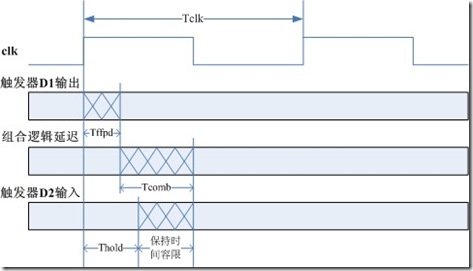

(2)保持时间的上限

如下图所示:

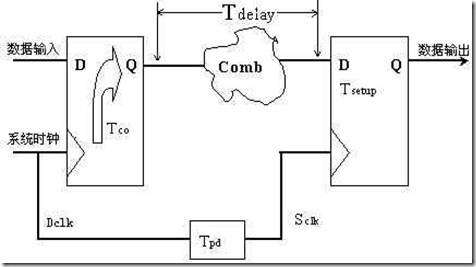

这个图乍看起来不是那么容易理解,下面稍微做一下说明。假设图1对应的电路如下:

假设从第二个触发器的D输入端引出几根线做波形测试。

在图1的第一个时钟上升沿时刻,触发器D1在满足保持时间后打出数据;与此同时,不考虑时钟延时,在同一时刻,D2若满足保持时间的要求,D2也会打出数据。

但是,D1打出的数据经过延时后来到D2的输入端时,若D2还处在满足保持时间所需的时间段内,D1打出的数据将会破坏D2本来应该保持的数据。

所以,若同时考虑时钟延迟,可得 保持时间容限+Thold+Tpd=Tffpd(min)+Tcomb(min),根据保持时间容限≥0,也就是Tffpd(min)+Tcomb(min)-Thold-Tpd≥0可以得到触

发器D2的Thold≤Tffpd(min)+Tcomb(min)-Tpd。

从以上的分析来看,D2的建立时间与保持时间与D1的建立与保持时间是没有关系的,而只和D2前面的组合逻辑和D1的数据传输延时有关,这也是一个很重要的结论。说明了延时没有叠加效应。