对于熟悉Intel FPGA的老(gong)司(cheng)机(shi)来说,外部存储器的控制早已是轻车熟路,但是对于新手,DDR3/DDR2 的IP使用也许并没有那么简单,不过没关系,骏龙的培训网站(www.fpgadesign.cn)上有免费的视频教程可以帮助大家快速的熟悉DDR3/DDR2 IP核的使用。今天我来分享下在使用DDR3/DDR2的IP时常有新手遇到的两个错误的解决办法。

1、Error (165050): The assigned location PIN B13 for DQ pin "DDR2A_DQ2" is not a legal location。

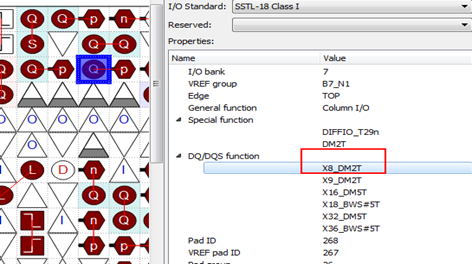

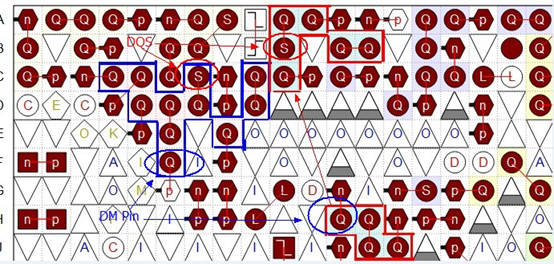

上面的错误提示是”DDR2A_DQ2”放在了一个非法的地方,也就是放错了地方。对于DDR3/DDR2 IP的DQ,DQS,DM信号在FPGA上对应的pin不是想当然的随便放置,他们有固定的位置,一般要遵循下面的几个规则:DQ信号必须连接到FPGA的引脚名带有DQS的pin(如图一);DM信号必须连接到FPGA的引脚名带DM的pin(如图二);DQS、DM、DQ必须在同一个Mode中,且DQS、DM的高地位要和DQ的高地位对应,如DQS[0],DM[0]对应DQ[7:0], DQS[1],DM[1]对应DQ[15:8]。在一个Mode中会有一个DQS pin,一个DM pin和多个DQ pin(如图三)。

图一 FPGA中引脚名带有DQS的pin

图二 FPGA中引脚名带有DM的pin

图三 Mode(图中有红线和蓝线分别标出了一个完整的Mod)

提示:查看同一个Mode的方法为:在Pin Planner的菜单栏选择ViewàshowàShow DQ/DQS pinà In x8/x9 Mode。

只要按照上面的规则来绑定DDR2/DDR3的pin 就可以解决Error 1.

2、Error (169224): Too many output and bidirectional pins per VCCIO and ground pair in I/O bank 8 when the VREF pin D12 (VREFGROUP_B8_N0) is used on device EP4CGX30CF23C7 -- no more than 9 output/bidirectional pins within 12 consecutive pads are allowed when the voltage reference pins are driving in, but there are potentially 10 pins driving out。

上面的错误提示是: 但使用VREF pin作为输入时,每12个连续的Pads不能有超过9个输出或双端口。这是因为DDR2采用的是SSTL-18的电平标准,需要将输入和VREF电压进行比较之后输出才被认为是实际输入(保证数据准备,抑制噪声),所以FPGA中DDR2所在的Bank中的VREF pin 需要接1.8V的电压。而在TOP 和Bottom Bank的VREF pin被使用时,每12个连续的Pads最多只支持9个输出,在Right和Left Bank每14个连续的Pads最多只支持9个输出。

但是对于一些IO数目比较紧张的项目,想把DDR2的地址线或控制线放在数据线周围的pin上,但是Fitter的时候 Quartus 会报出上面的错误,这该怎么办呢?只要在Quartus II 中按照下面的步骤使用Output Enable Group选项,将DDR2的CLK ,DQS,DM,DQ信号设置到到同一个Group中,就可以解决上面的错误了。使用Output Enable Group选项可以指导Fitter当作一个输出使能组来查看指定的Nodes,以免违反使用VREF时的最大连续输出Pads数目的规定。

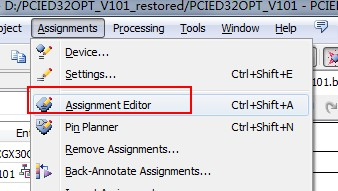

在菜单栏中选择AssignmentsàAssignment Editor,打开Assignment Editor窗口,在TO列最下面<<new>>处依次填入DDR2 IP 的所有CLK ,DQS,DM,DQ信号,并在Assignment Name处选择Output Enable Group, 在Value处都填入一个相同的值(如图五中的111222),然后在最左边你可以看到Status处都打上了绿色的对号,这样设置就完成了,保存,重新编译,Fitter就可以通过了。

图四

图五

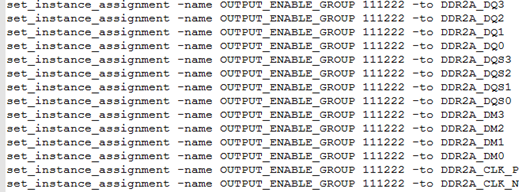

上面的操作完成之后,如果你打开工程目录下的.qsf文件,你可以找到图六中的约束语句,就是刚才你设置的约束条件。当然,你也可以直接的打开.qsf文件,参照图六中的语句直接设置CLK ,DQS,DM,DQ的约束条件,并保存,也可以达到相同的效果。

图六

Error 2 就这样被解决了!