在Quartus中做设计,如果使用了差分信号的,如DDR的IP中的mem_ck与mem_ck_n,mem_dqs与mem_dqs_n,将其引入输出端口时,对其命名有一定的规则,否则就会出现错误。

如下所示,例化是错误的。

DDR3_32BIT emif_32bit ( ...... .mem_ck (mem_ck_1), // mem.mem_ck .mem_ck_n (mem_ck_n_1), // .mem_ck_n .mem_dqs (mem_dqs_1), // .mem_dqs .mem_dqs_n (mem_dqs_n_1), // .mem_dqs_n ........... );

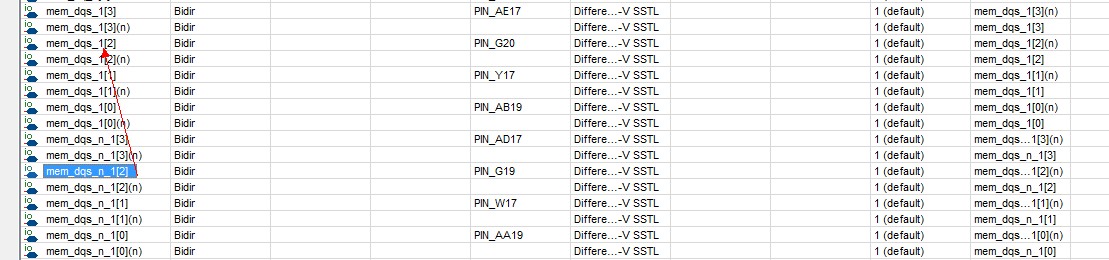

这样例化之后在编译之后,在pin planner会出现下面的管脚:

可以看出,出现了一些带XXX(n)的信号,原来的差分信号也被拆开了。这不是我们想要的,还会导致布线不会过。

正确的例化方法:

如果使用下面的例化方法,就不会出现上面的错误。

如: DDR3_32BIT emif_32bit (

......

.mem_ck (mem_ck_1), // mem.mem_ck

.mem_ck_n (mem_ck_1_n), // .mem_ck_n

.mem_dqs (mem_dqs_1), // .mem_dqs

.mem_dqs_n (mem_dqs_1_n), // .mem_dqs_n

...........

);

编译之后的情况为:

可以看出没有多余的信号出现。

原因是,Quartus ii默认信号 A和 A_n信号为差分信号。这样在编译的时候就会将其变为差分信号了。