I2S(Inter-IC Sound)是飞利浦公司针对数字音频设备(如CD播放器、数码音效处理器、数字电视音响系统)之间的音频数据传输而制定的一种总线标准。它采用了沿独立的导线传输时钟与数据信号的设计,通过将数据和时钟信号分离,避免了因时差诱发的失真,为用户节省了购买抵抗音频抖动的专业设备的费用。

I2S有3个主要信号:

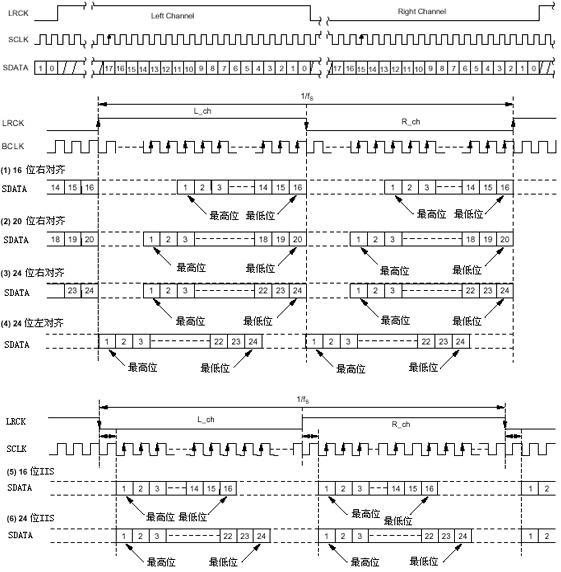

1.串行时钟SCK,也叫位时钟(BCLK),即对应数字音频的每一位数据,SCLK都有1个脉冲。SCLK的频率=2×采样频率×采样位数

2.字段(声道)选择WS,又称为LRCK,用于切换左右声道的数据。LRCK为“1”表示正在传输的是左声道的数据,为“0”则表示正在传输的是右声道的数据。LRCK的频率等于采样频率。LRCK一个时钟周期采一个样点,BCLK为64fs,即一时钟周期64位数据。

3.串行数据SD(SDATA),就是用二进制补码表示的音频数据。在飞利浦公司的I2S标准中,既规定了硬件接口规范,也规定了数字音频数据的格式。有时为了使设备间能够更好地同步,还需要另外传输一个信号MCLK,称为主时钟,也叫系统时钟(Sys Clock),是采样频率的256倍或384倍。

对于系统而言,产生SCK和WS的信号端就是主设备,用MASTER表示.

I2S格式的信号无论有多少位有效数据,数据的最高位总是出现在LRCK变化(也就是一帧开始)后的第2个SCLK脉冲处。这就使得接收端与发送端的有效位数可以不同。如果接收端能处理的有效位数少于发送端,可以放弃数据帧中多余的低位数据;如果接收端能处理的有效位数多于发送端,可以自行补足剩余的位。这种同步机制使得数字音频设备的互连更加方便,而且不会造成数据错位。

随着技术的发展,在统一的 I2S接口下,出现了多种不同的数据格式。根据SDATA数据相对于LRCK和SCLK的位置不同,分为左对齐(较少使用)、I2S格式(即飞利浦规定的格式)和右对齐(也叫日本格式、普通格式)。

支持32/64 bit的I2S接口,可以传输32bit一下的数据。

对于支持32 bit来说, BCLK = 2*44.1HZ*32=2.8224MHZ.注意CD的采样位数是16位的,传输CD数据时,I2S会自动补零,这对实际的16位采样不产生任何影响,但是对于你用32bit的I2S信号传送超过32位采样率的音频信号,就会有损失。