1、基本原理

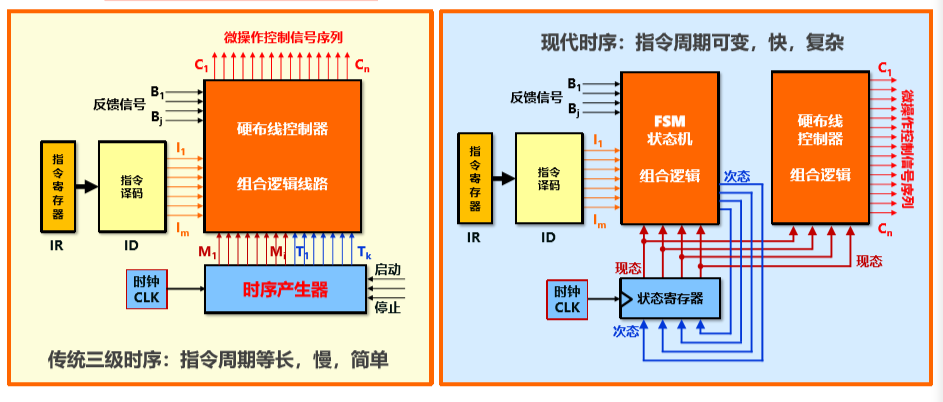

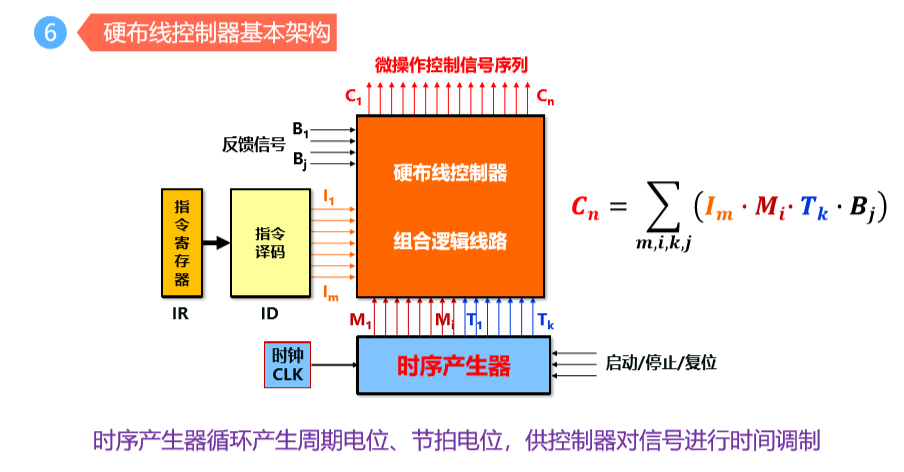

控制器的核心功能是完成指令的自动执行,而指令的自动执行有赖于各功能部件之间的数据通路的建立,而数据通路的建立,有赖于控制器生成控制信号的序列,所以,从宏观上看,控制器可以看作为一个能够产生固定的时序控制信号的逻辑电路。

这个逻辑电路的输入是指令译码信号,每一条指令都会产生一个译码输出,另一个输入是时钟信号,还有就是指令执行时的一些反馈信号,

输出就是各功能部件所需要的微操作控制信号序列,

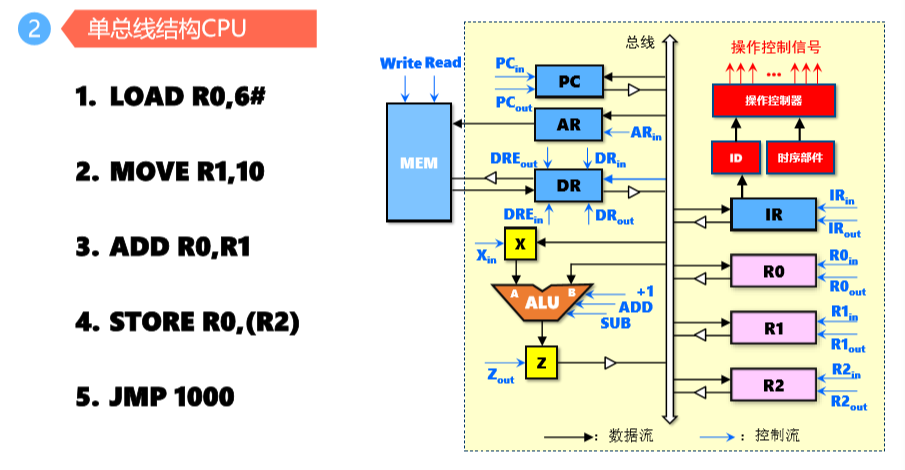

2、单总线结构CPU

3、单总线结构CPU指令周期

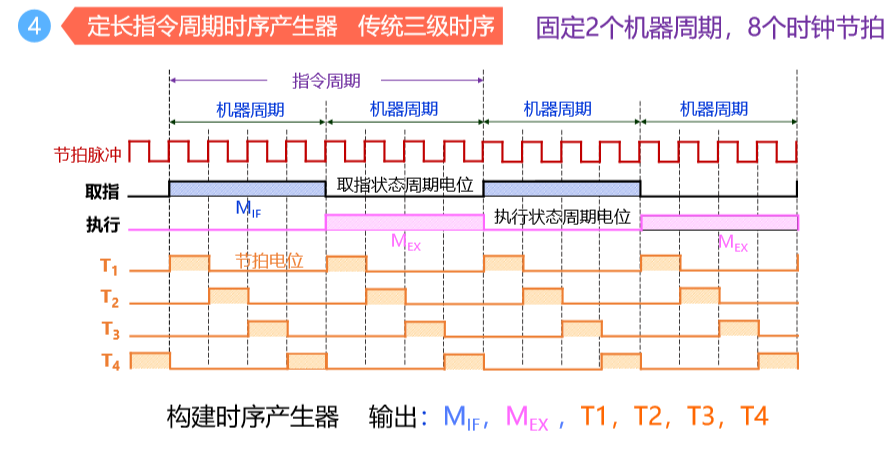

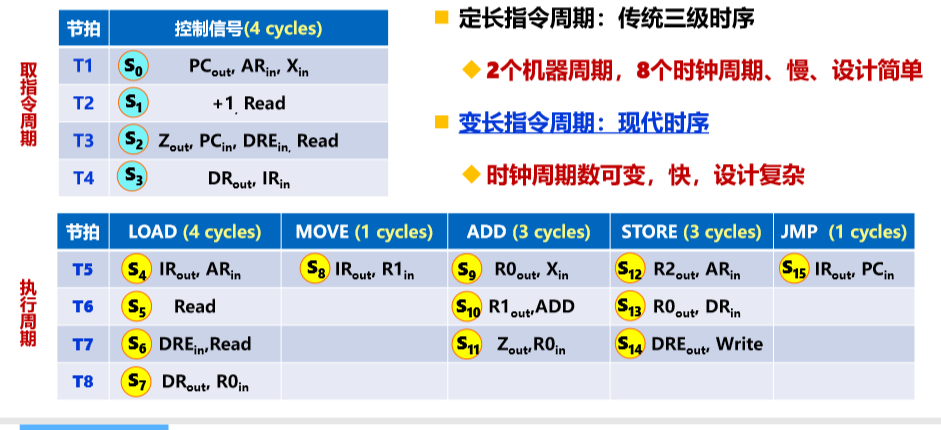

在设计硬布线控制器的时候有两种思路,第一种是所有的指令执行可能是定长的指令周期,在这种方法里,我们应该取所有指令里面最慢的那条指令进行同步,在这里因为load指令所需要的时间最长,所以我们用load指令的8个时钟周期进行同步,它需要两个机器周期分别完成取指令和执行指令(这里假设一个机器周期为4个时钟周期)

第二种方法就是用边长指令周期的方法,更加灵活。

首先来看定长指令周期的设计过程:

要设计定长指令周期,我们需要首先构建它的时序产生器,也就是生成传统的三级时序的这样一个时序产生器,由三级时序产生器里面非常重要的一个基础的时钟,就是节拍脉冲,由节拍脉冲生成具体的状态周期电位,状态周期电位包括取指令周期单位和执行指令周期单位,这个电位信号标识对应当前指令处于哪一个周期,我们还要有节拍电位,

三级时序指的就是,节拍脉冲、状态周期电位、节拍电位。

5、时序产生器状态机

6、硬布线控制器基本架构

7、单总线cpu控制信号生成

8、固定指令周期硬布线控制器设计过程

1、设计三级时序产生器:所有指令固定机器周期数,节拍数

2、列出所有机器指令的指令周期流程图,明确每个节拍的控制信号,

3、找出产生同一微操作控制信号的条件

4、写处各微操作控制信号的布尔表达式

5、化简各表达式

6、利用组合逻辑电路实现。

变长指令周期的硬布线控制器设计

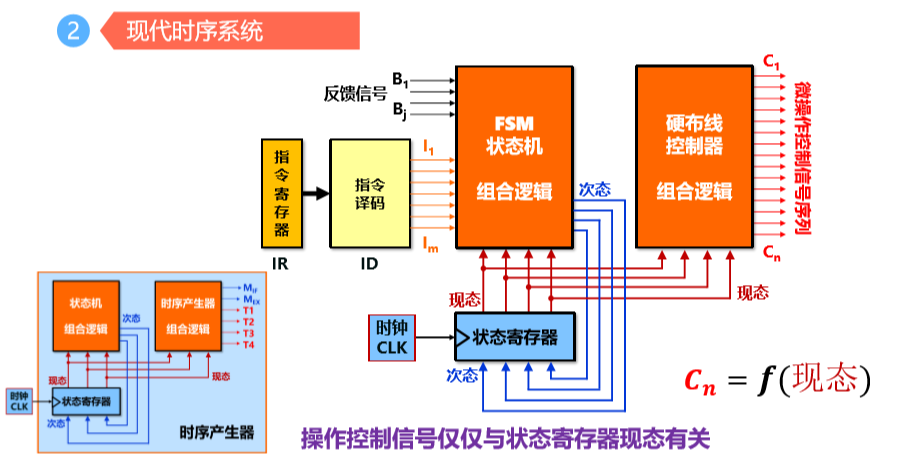

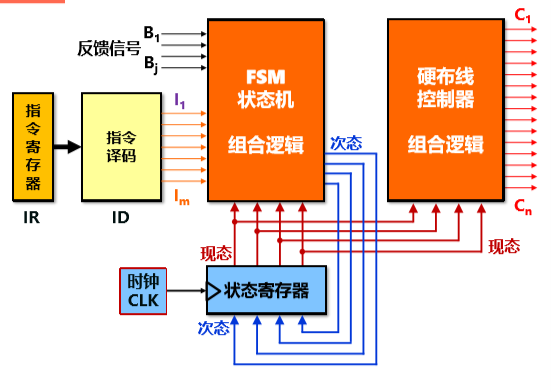

在指令执行过程中,状态的切换除了与时钟有关系以外,还跟指令的译码信号有关系,我们将所有指令在执行的不同阶段,都用一个状态唯一的标识,比如上表中,将指令分节拍表示成了16个状态来表示,我们用一个四位的状态机来表示指令执行的不同的状态,这样的话,指令执行过程中,所有的信号只与对应的状态有关,所以有了状态机以后,对应的最终的控制信号,只与状态机的现态有关。

2、现代时序系统

3、指令执行状态转换图

4、有限状态真值表

5、可变周期硬布线控制器设计步骤

1、列出所有机器指令的指令周期流程图,明确每个节拍的控制信号

2、绘制指令执行状态转换图

3、根据状态转换图构建状态机真值表,实现有限状态机组合逻辑

4、实现控制器组合逻辑电路

6、传统时序与现代时序对比