FPGA原语之一位全加器

1、实验原理

一位全加器,三个输入,两个输出。进位输出Cout=AB+BC+CA,本位输出S=A异或B异或C。实验中采用三个与门、一个三输入或门(另外一个是两个或门,功能一致)、一个三输入异或门实现该简单功能。

2、实验操作

实验设计还是比较简单的,直接看代码即可:

module test2( input clk, input rt_n, input [3:0] key_c, output [3:0] key_r, output [11:0] led ); wire k1,k2,k3,k4; assign k1=key_c[0]; assign k2=key_c[1]; assign k3=key_c[2]; assign k4=key_c[3]; assign key_r=4'b0; xor xor1(led[0],k1,k2,k3); and and1(led[11],k1,k2); and and2(led[10],k2,k3); and and3(led[9],k3,k1); or or1(led[8],led[11],led[10]); or or2(led[2],led[8],led[9]); or or3(led[3],led[9],led[10],led[11]); endmodule

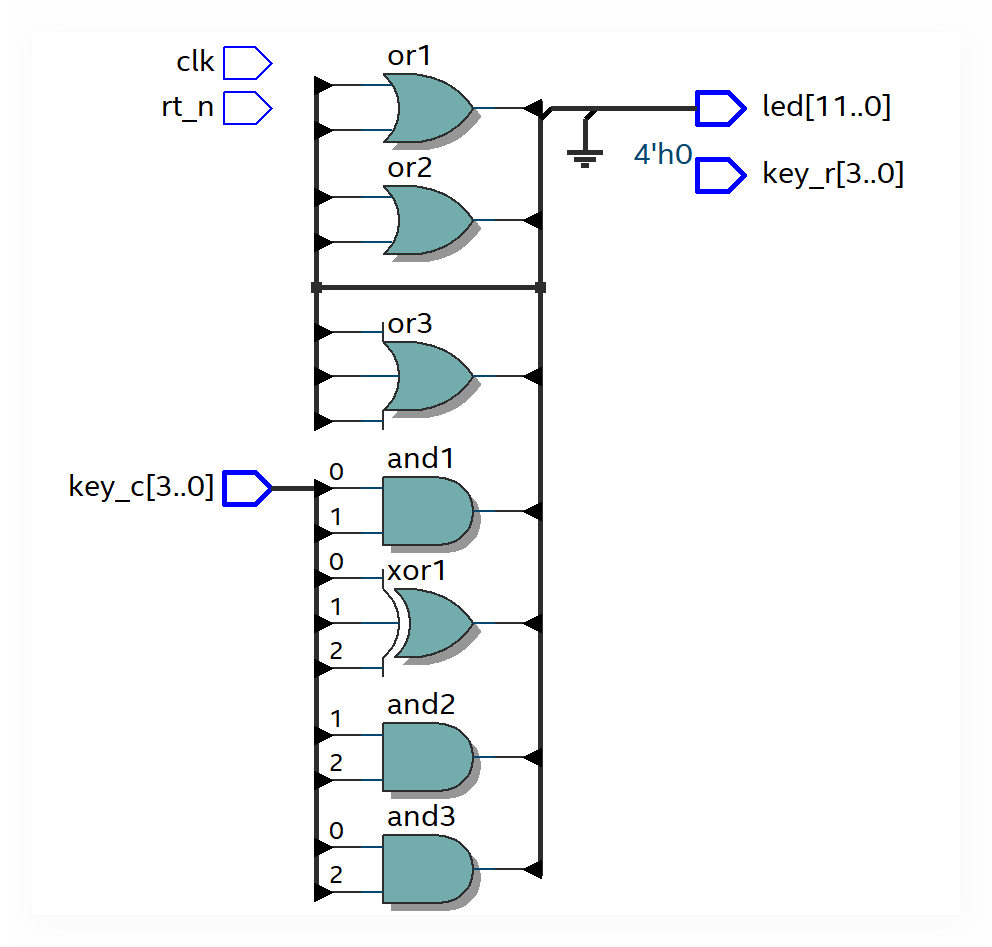

就是直接调用,输出结果直接显示在led上,也就没有区分led,下次可能需要注意一下。生成的RTL视图看不出具体的电路结构,只能看到调用的器件和总线。

3、实验结果

RTL视图

器件的数量和连线基本正确。板级验证就是按相应的输入即可得到具体的输出。这里就不展示了。后面可能验证的就是更加复杂的数字电路。可以将FPGA作为一个可以反复使用的数字电路实验平台。