https://www.cnblogs.com/shangdawei/p/4752476.html

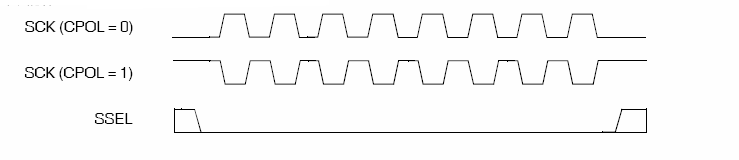

CPOL极性

先说什么是SCLK时钟的空闲时刻,其就是当SCLK在发送8个bit比特数据之前和之后的状态,于此对应的,SCLK在发送数据的时候,就是正常的工作的时候,有效active的时刻了。

其英文精简解释为:Clock Polarity = IDLE state of SCK。

SPI的CPOL,表示当SCLK空闲idle的时候,其电平的值是低电平0还是高电平1:

CPOL=0,时钟空闲idle时候的电平是低电平,所以当SCLK有效的时候,就是高电平,就是所谓的active-high;

CPOL=1,时钟空闲idle时候的电平是高电平,所以当SCLK有效的时候,就是低电平,就是所谓的active-low;

从上图中可以看出,(CPOL=0)的SCK 波形,它有(传输)8 个脉冲,而在脉冲传输前和完成后都保持在【低电平状态】。

此时的状态就是时钟的空闲状态或无效状态,因为此时没有脉冲,也就不会有数据传输。

同理得出,(CPOL=)1 的图,时钟的空闲状态或无效状态时SCK 是保持【高电平的】。

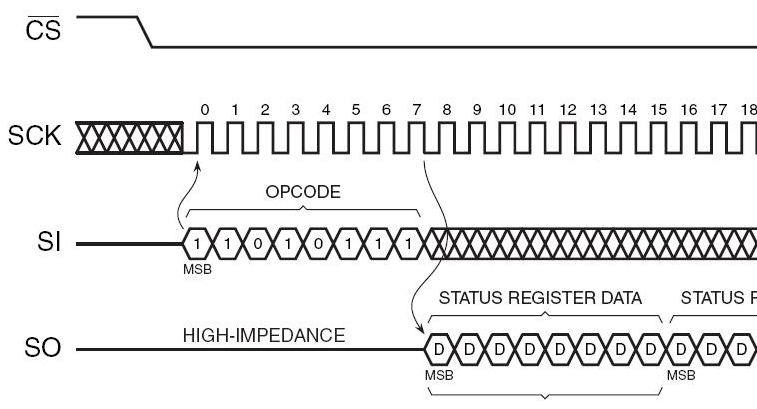

CPHA相位

首先说明一点,capture strobe = latch = read = sample,都是表示数据采样,数据有效的时刻。相位,对应着数据采样是在第几个边沿(edge),是第一个边沿还是第二个边沿,

0对应着第一个边沿,1对应着第二个边沿。对于:

CPHA=0,表示第一个边沿:

对于CPOL=0,idle时候的是低电平,第一个边沿就是从低变到高,所以是上升沿;

对于CPOL=1,idle时候的是高电平,第一个边沿就是从高变到低,所以是下降沿;

对于CPOL=0,idle时候的是低电平,第一个边沿就是从低变到高,所以是上升沿;

对于CPOL=1,idle时候的是高电平,第一个边沿就是从高变到低,所以是下降沿;

CPHA=1,表示第二个边沿:

对于CPOL=0,idle时候的是低电平,第二个边沿就是从高变到低,所以是下降沿;

对于CPOL=1,idle时候的是高电平,第一个边沿就是从低变到高,所以是上升沿;

我们看上面的图,发现数据 SI 是对应 SCK 的第一个时钟沿,

再仔细看,数据是在SCK的第一个时钟边沿保持稳定【数据被采样捕获】,

在下一个边沿改变【SCK 的下降沿数据改变】因此我们得出结论:

该系列FLASH 是【数据在第一个时钟沿被采样捕获】

或【数据在SPCK 起始边沿捕获,在SPCK 下一个边沿改变】