UART的结构大家并不陌生,用HDL语言写一个UART收发器也并不难。本文中作者给出一个可以应用到实际工程中的UART收发器,并且是经过验证的。

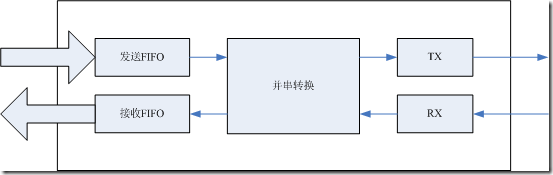

UART的结构如上图所示。其核心在于两个FIFO的运用。其实收和发两个部分是独立的,完全可以分开单独使用,作者为了方便起见,将两者放在了一起。

原理也比较简单,以发送为例。FIFO是8位的,只要上层模块不停地往发送FIFO里填数据,发送器就会自动从FIFO里读数据,并将数据转换成串行的向外发送。

更具体一点,就是检测到FIFO的不为空的时候,就去读数据,一直读到FIFO为空。上层的模块在FIFO满的时候,就不要写数据了,以避免数据溢出而丢失。所以,在不同的FPGA芯片上实现该UART的时候,可以根据需要自己选择适合的FIFO长度。

接收的时候也类似,这里就不多说。

源代码:

http://myfpga.googlecode.com/files/fifo_uart.rar

说明,fifo_to_uart.v是UART的顶层文件,top.v是测试程序。如果要用到具体的FPGA上,需要自己添加一个FIFO,最好是FPGA自带的FIFO核,直接例化。

另外,此UART的发送部分是可用的,接收部分不可用,需要读者自行修改,但不影响发送部分和整体的使用。