Vivado中ILA的使用

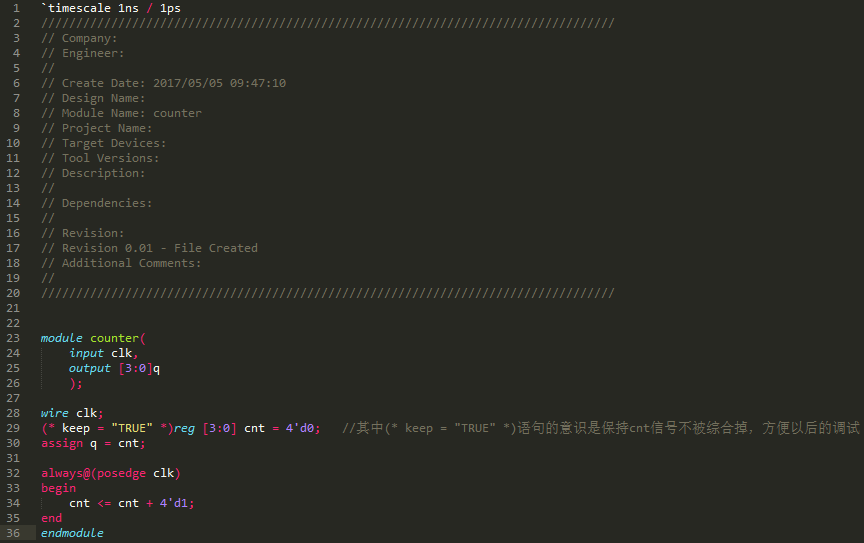

1.编写RTL代码

其中需要说明的是(* keep = "TRUE" *)语句的意识是保持cnt信号不被综合掉,方便以后的调试,是否可以理解为引出这个寄存器信号。

其中需要说明的是(* keep = "TRUE" *)语句的意识是保持cnt信号不被综合掉,方便以后的调试,是否可以理解为引出这个寄存器信号。

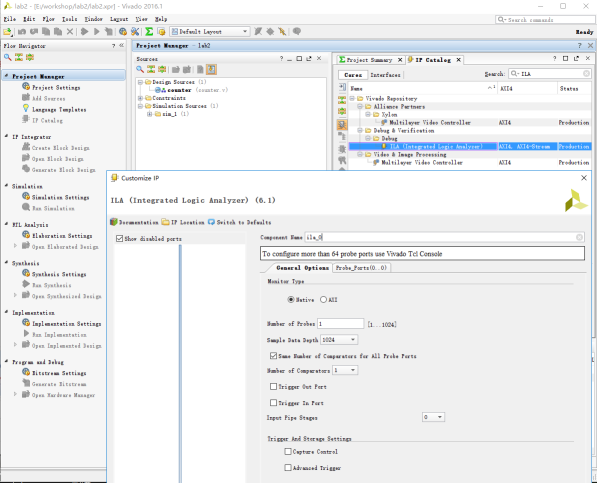

2.加入ILA核

3.配置ILA核

需要配置的参数主要有三个:1.Component Name,组件的名字,2.Number of Probes 需要抓取的信号的个数,3.Sample Data Depth 抓取的信号的深度。

第二页:

配置所抓取的信号的宽度,此实验的cnt是4bit。

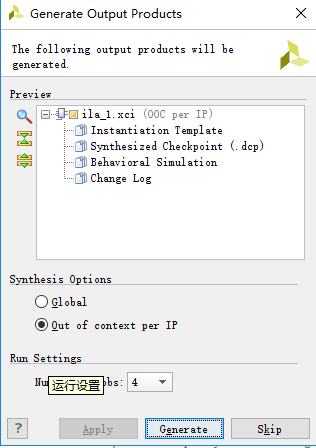

IP核配置完成,生成即可:

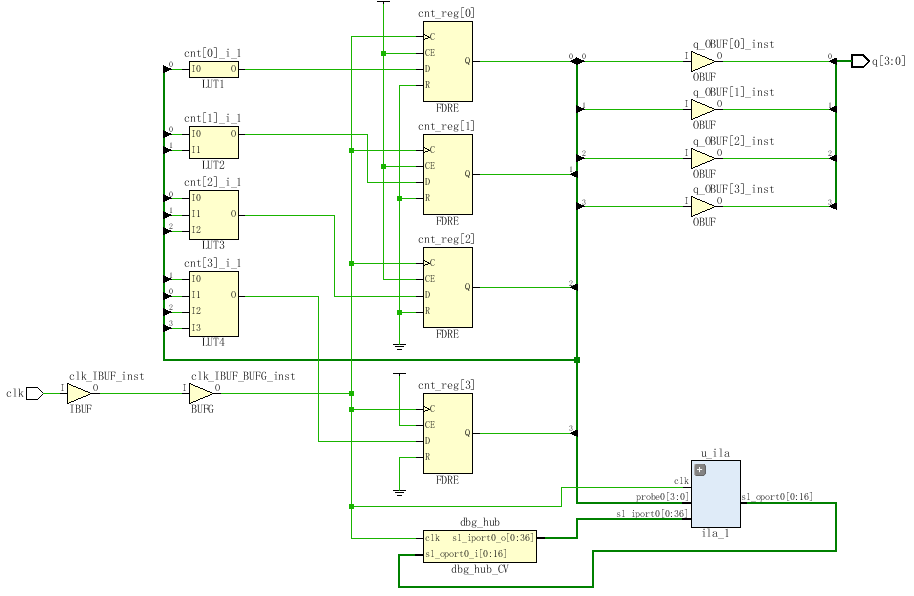

4.在RTL中添加ILA核

此时需要注意的是ILA核的clk信号需要连接到需要观察信号的相应时钟域,在一个RTL设计中是可以添加多个ILA核的,方便观察不同时钟域的信号。

5.综合

综合所得结果为:

由于没有进行引脚约束,没办法生成bit文件。

5.调试

最后就是将bit文件下载到FPGA中,然后在软件上查看波形。