一、Class及常用规则的创建

设计>>类>>有包括Net Classes、Component Classes、Layer Classes、Pad Classes、 Differential Pair Classes

>>选中Net,下面全选后右键>>Change NetColor>>选好颜色后,线就变了。

二、PCB扇孔处理

对于扇孔应该提前不好,以免后面走完线,没有地方再打孔。

BGA的自动扇孔,自动布线>>扇出>>器件>>勾掉无网格焊盘扇出。

第三个选项“扇出完成后包含逃逸路线”是可以扇孔后。

点击确定后,选择CPU发现扇出的孔很少,所以要设置VIA的规则,过孔设置为16-8mil。

然后设置电源的走线规则,普通的使用5.5mil,class PWR使用10mil、12mil、60mil。

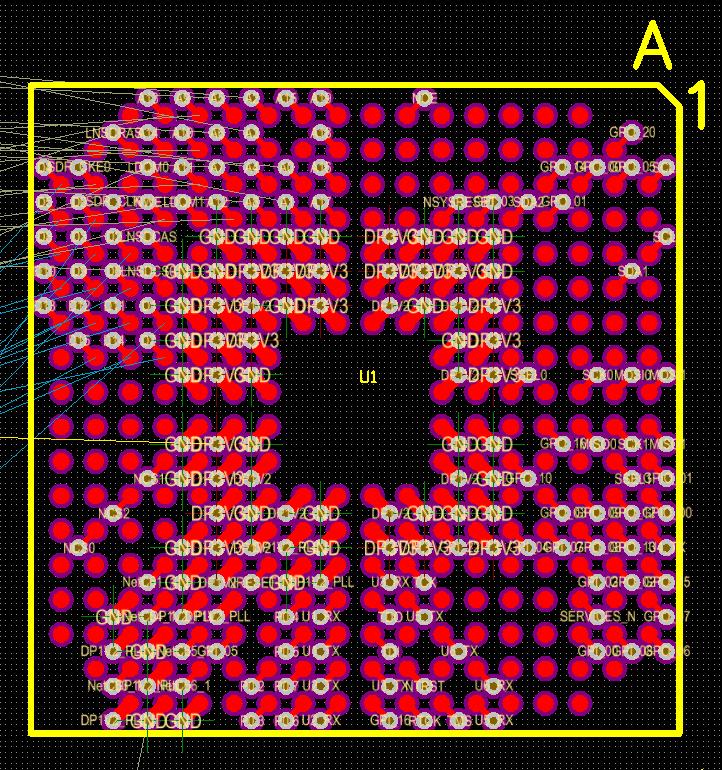

效果图

效果图

输入输出的主干道电流可能达到1A~3A,一般走线20mil可以承载1A电流。如果有3A的话,要走到60mil。

一般来说0.5mm的过孔可以承载1A的电流

供电和GND需要铺铜,GND可以fill补充连接。

然后晶振的走线用π型走线

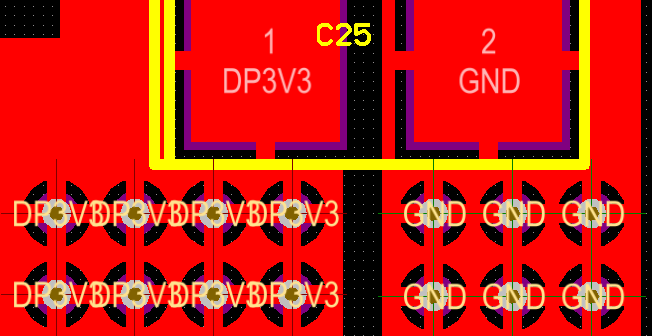

然后放BGA的去耦电容,GND引脚可以两两和并(如果空间不够的话)

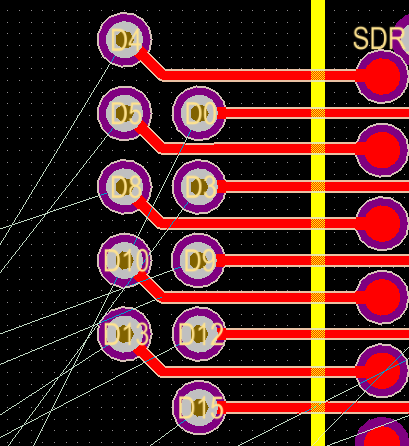

三、SDRAM的布线

BGA表层走线比较麻烦,所以考虑从底层走线。因为SDRAM有三排的孔,所以基本上是引不出来的。

所以要把前两排的孔,往外面多拉一些距离。

然后引出来的线,用shift+R的形式可以忽略DRC走线。布线的思路:先从BGA中把线拉出来,然后在外面设置线的顺序(换线)

对于冲突的线,优先删除冲突多的那根线。然后调整孔位,来使得交叉的线能走顺。

把线连出来后,从下往上的依次理顺这些线(有可能会花点时间)

四、Flash的布线和排针布线

因为是核心板,所以排针的位置可以修改,在底板的时候对应就好了。

优先把线引出来,电容就先移开。晶振阻碍了布线的话,可以从电容下面走,尽量不从晶振线下走。

最后剩下遇到这种情况,对排针双击>>元件属性>>锁定 去掉。

然后剪切,粘贴,网络就自动改好了。然后把电源的网络再改好,非电源都用GND。

然后如何把修改后的网络,同步到原理图呢?在PCB栏中选择Components,选择interface(原理图中模块)

下面有器件,选好J1之后,右键显示焊盘,其他可以关掉。然后吧引脚全选中后拷贝。桌面新建excel粘贴。然后不是把网络都复制过来了吗,打开原理图可以改了2333

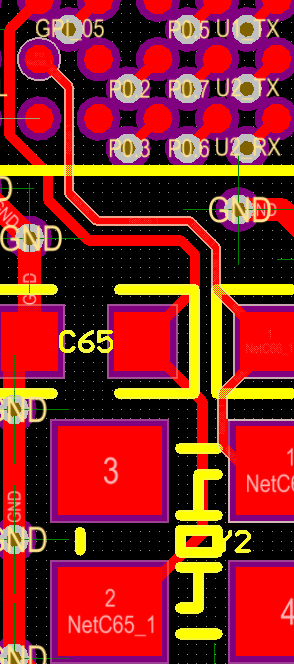

五、走线联通性处理及电源分割

优先是信号,然后是电源,最后是地的顺序处理。基本都连好后,选中PWR03层。

然后选择走线10mil,把供电DP1V2框起来,选择对应的网络。同理DP1V2_PLL和3V3