原创声明:

本原创教程由芯驿电子科技(上海)有限公司(ALINX)创作,版权归本公司所有,如需转载,需授权并注明出处。

适用于板卡型号:

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

vivado工程目录为“ps_hello/vivado”

vitis工程目录为“ps_net/vitis”

软件工程师工作内容

以下为软件工程师负责内容。

开发板有两路千兆以太网,通过RGMII接口连接,本实验演示如何使用Vitis自带的LWIP模板进行PS端千兆以太网TCP通信。

LWIP虽然是轻量级协议栈,但如果从来没有使用过,使用起来会有一定的困难,建议先熟悉LWIP的相关知识。

1. Vitis程序开发

1.1 LWIP库修改

由于自带的LWIP库只能识别部分phy芯片,如果开发板所用的phy芯片不在默认支持范围内,要修改库文件。也可以直接使用修改过的库替换原有的库。

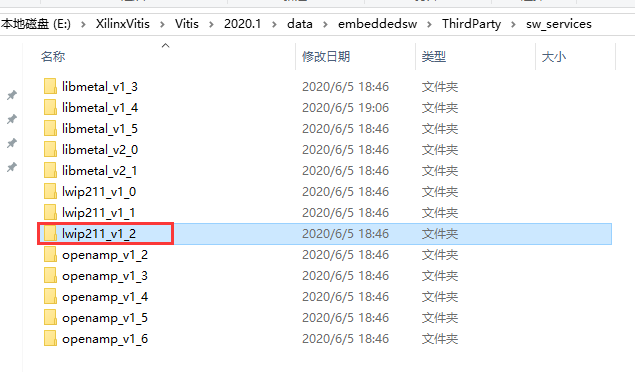

1) 找到库文件目录“X:xxxVitis2020.1dataembeddedswThirdPartysw_services”

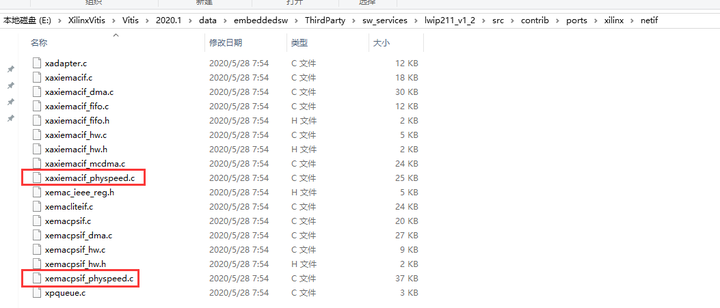

2)找到要修改的文件目录“lwip211_v1_2srccontribportsxilinx etif”中文件“xaxiemacif_physpeed.c”和“xemacpsif_physpeed.c”要修改。

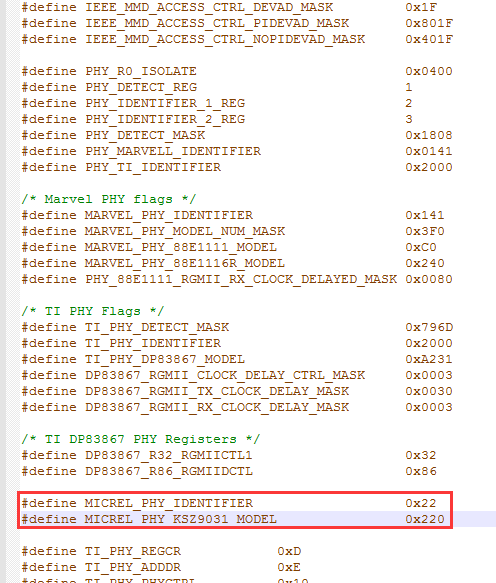

3)修改PL端的“xaxiemacif_physpeed.c”文件,添加相关宏定义

4)添加phy速度获取函数

unsignedint get_phy_speed_ksz9031(XAxiEthernet *xaxiemacp, u32 phy_addr)

{

u16 control;

u16 status;

u16 partner_capabilities;

xil_printf("Start PHY autonegotiation

");

XAxiEthernet_PhyWrite(xaxiemacp,phy_addr, IEEE_PAGE_ADDRESS_REGISTER,2);

XAxiEthernet_PhyRead(xaxiemacp, phy_addr, IEEE_CONTROL_REG_MAC,&control);

//control |= IEEE_RGMII_TXRX_CLOCK_DELAYED_MASK;

control &=~(0x10);

XAxiEthernet_PhyWrite(xaxiemacp, phy_addr, IEEE_CONTROL_REG_MAC, control);

XAxiEthernet_PhyWrite(xaxiemacp, phy_addr, IEEE_PAGE_ADDRESS_REGISTER,0);

XAxiEthernet_PhyRead(xaxiemacp, phy_addr, IEEE_AUTONEGO_ADVERTISE_REG,&control);

control |= IEEE_ASYMMETRIC_PAUSE_MASK;

control |= IEEE_PAUSE_MASK;

control |= ADVERTISE_100;

control |= ADVERTISE_10;

XAxiEthernet_PhyWrite(xaxiemacp, phy_addr, IEEE_AUTONEGO_ADVERTISE_REG, control);

XAxiEthernet_PhyRead(xaxiemacp, phy_addr, IEEE_1000_ADVERTISE_REG_OFFSET,

&control);

control |= ADVERTISE_1000;

XAxiEthernet_PhyWrite(xaxiemacp, phy_addr, IEEE_1000_ADVERTISE_REG_OFFSET,

control);

XAxiEthernet_PhyWrite(xaxiemacp, phy_addr, IEEE_PAGE_ADDRESS_REGISTER,0);

XAxiEthernet_PhyRead(xaxiemacp, phy_addr, IEEE_COPPER_SPECIFIC_CONTROL_REG,

&control);

control |=(7<<12); /* max number of gigabit attempts */

control |=(1<<11); /* enable downshift */

XAxiEthernet_PhyWrite(xaxiemacp, phy_addr, IEEE_COPPER_SPECIFIC_CONTROL_REG,

control);

XAxiEthernet_PhyRead(xaxiemacp, phy_addr, IEEE_CONTROL_REG_OFFSET,&control);

control |= IEEE_CTRL_AUTONEGOTIATE_ENABLE;

control |= IEEE_STAT_AUTONEGOTIATE_RESTART;

XAxiEthernet_PhyWrite(xaxiemacp, phy_addr, IEEE_CONTROL_REG_OFFSET, control);

XAxiEthernet_PhyRead(xaxiemacp, phy_addr, IEEE_CONTROL_REG_OFFSET,&control);

control |= IEEE_CTRL_RESET_MASK;

XAxiEthernet_PhyWrite(xaxiemacp, phy_addr, IEEE_CONTROL_REG_OFFSET, control);

while(1){

XAxiEthernet_PhyRead(