在高速数字设计领域,信号完整性(SI,signal integrity)概念已经被提出来很多年了。而对可编程逻辑器件的设计工程师来说,往往对这个概念没有引起足够的重视。有的人甚至认为,做数字逻辑电路的设计跟这些知识没有什么直接关系,那就非常危险了。

任何危险,只要注意他,就可以设法避免他。

但事实上,设计工程师在设计过程中没有给SI足够的重视,造成设计不稳定,导致功能无法实现,需要重新设计PCB的案例非常多。这里,介绍一些SI的概念,希望读者能真正了解SI,对其引起足够的重视,这样才能尽可能地避免PCB上SI问题所带来的麻烦。

所谓信号完整性,就是要使信号具有良好的物理特性(高低电平的阈值以及跳变沿的特性),防止其产生信号畸变,导致接收端无法识别。

在实际的系统中,经常听到许许多多关于信号完整性的问题,如反射(reflection),振铃(ringing),开关噪声(switching noise),地弹(ground bounce),衰减(attenuation),串扰(cross talk),容性负载(capacitive load)等。听起来头绪非常多,让人防不胜防,但是仔细分析这些现象的起因,就可以很容易的把他们归纳为4类,即单一网络的信号质量、电源和地噪声、不同信号线之间的串扰、系统的电磁干扰(EMI)。

传输线效应

一个信号传输系统对输入信号的响应情况,取决于传输线长度与电流信号的快慢。

在传统的低速电路设计中,由于其传输的时间与信号的电压变化时间相比很小,PCB走线可以看作是一个完美的电气连接点。像中学物理课本中描述的一样,可以认为电信号的速度无穷大,瞬间可以传遍整个导体,只要由一根铜线相连,就可以认为在所有的点看到的信号变化一致。

但是在高速系统中,这种理想的互连线就成为工程师不断追求但永远也达不到的目标。在一个信号的传输过程中,如果信号的边沿时间足够快,短与6倍的信号传导延时,那么在信号的传输过程中,传输媒介就会表现出传输线特性。

信号在媒介上传输就像波浪在水中传送一样,会产生波动和反射等现象。

这里需要提醒的一个容易忽略的问题,任何从信号源输出到走线上的电流,都会返回到源端,因此,信号不仅仅是在信号线上传输,同时也是在参考平面(回路)上传输,在信号路径和回路上的电流大小相等,方向相反。

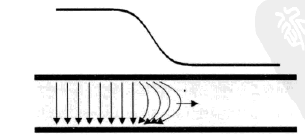

信号在走线上传导的同时,信号线和参考平面之间的电场也在逐步建立。下图所示,一个从0到1的信号跳变在传输,信号的跳变沿传输到哪里,哪里的电场就开始建立,信号传输的快与慢实际上取决于电场建立的速度。

在信号的传输过程中,在信号到达的地方,信号线和参考平面之间由于电场的建立,就会产生一个瞬间的电流,如果传输线是各向同性的,那么只要信号在传输,就会时钟存在一个电流I,如果信号的输出电平为V,则在信号传输过程中,传输线就会等效成一个电阻,大小为V/I,把这个电阻值称为传输线的特征阻抗,Z0,要格外注意的是,这个特征阻抗是对交流信号而言的,对直流信号,传输线的电阻不是Z0,而是远远小于这个值。

传输线特征阻抗的值与信号线和回路的特性都密切相关。

信号在传输过程中,如果传输路径上的特征阻抗发生变化,信号就会在阻抗不连续的节点产生发射。

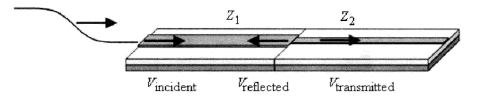

传输线的宽度变化,导致两段走线的阻抗不一样,在连接点处就存在阻抗不连续的问题,会使得入射信号在此产生反射现象。

如上图,VI表示入射波的电压,VR表示反射波的电压,VT表示沿着传输线继续传送的信号电压幅度,Z1和Z2是两段不同的走线的特征阻抗。VR和VI的关系满足:

其中p为反射系数。从反射系数的定义可以分析出,如果Z2大于Z1,VR是正值,反之,VR为负值。设想一种极端情况,如果Z2无穷大,,即Z1传输线后面是完全开路的,这样的话,p近似等于1,也就是说入射信号被完全反射回来。

在实际系统中,一般来说,工程师总是尽量想办法减少信号在传输过程中的反射问题,因为信号在传输线上来回反射对其并不是一件好事。

在实际系统中,也有利用反射机制的实例。例如,PCI总线与其他的许多总线不同,它在总线的终端没有匹配电阻,而是利用反射的机制实现其需要的时序。

在PCB设计过程中,造成传输线阻抗不连续的原因很多,如下:

-

线宽改变

-

走线与参考平面间距改变

-

信号换层,过孔

-

回路中存在缺口

-

连接器

-

走线分支,分叉,短线桩

-

走线末端

导致阻抗不连续的原因很多,不胜枚举,在设计PCB时,必须注意保持传输线由始至终阻抗尽量连续,不要出现较大的改变,通常所说的“阻抗控制”就是这个意思。

另外,在信号的终端,合理利用终端电阻吸收信号,防止其反射,也是PCB设计中一项非常重要的工作。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间