DAC框图

- VDDA:模拟电源输入

- VSSAL:模拟电源接地输入

- Vref+:正模拟参考电压输入

——————————————- DORx:输入数字寄存器

- DAC_OUT:模拟输出通道

- DAC_OUT1 ->PA4

- DAC_OUT2 ->PA5

DAC概述

- 12位数字输入,电压输出

- 2种模式

- 12位模式:此时数据可以设置成左对齐或右对齐

- 8位模式

- 2个DAC

- 每个DAC转换器对应一个通道

- 可以独立转换

- 也可以同时进行转换,并同步地更新2个通道的输出

寄存器

| 简称 | 全称 |

|---|---|

| DAC_CR | DAC control register |

| DAC_SWTRIGER | DAC software trigger register |

| DAC_DHR12R1 | DAC channel1 12-bit right-aligned data holding register |

| DAC_DHRx | DAC channelx data holding register |

过程

- 软件将数据加载到DAC_DHRx寄存器

- 写入的数据将移位并存储到相应的 DHRx(数据保 持寄存器 x,即内部非存储器映射寄存器)

- 根据是否选择硬件触发,DHRx 寄存器将被自动加载,或者通过软件或外部事件触发加载到

- DORx 寄存器的数据在 t SETTLING 时间后给模拟输出电压

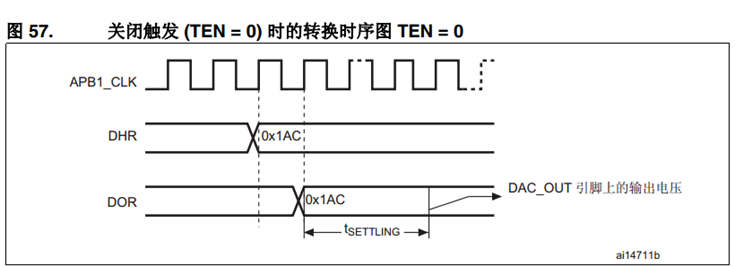

时序:

- 如果未选择硬件触发:

- (DAC_CR 寄存器中的 TENx 位复位)

- 经过一个 APB1 时钟周期后, DAC_DHRx寄存器中存储的数据将自动转移到 DAC_DORx 寄存器。

- 如果选择硬件触发

- (置位 DAC_CR 寄存器中的 TENx位)且触发条件到来

- 将在三个 APB1 时钟 周期后进行转移。

- 当 DAC_DORx 加载了 DAC_DHRx内容时,模拟输出电压将在一段时间 t SETTLING 后可用,具体时间取决于电源电压和模拟输出负载。

数据保持寄存器

对于 DAC 单通道 x,有三种可能的方式:

- 8 位右对齐:软件必须将数据加载到 DAC_DHR8Rx [7:0] 位(存储到 DHRx[11:4] 位)。

- 12 位左对齐:软件必须将数据加载到 DAC_DHR12Lx [15:4] 位(存储到 DHRx[11:0] 位)。

- 12 位右对齐:软件必须将数据加载到 DAC_DHR12Rx [11:0] 位(存储到 DHRx[11:0] 位)。

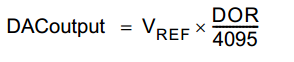

DAC 输出电压

经过线性转换后,数字输入会转换为 0 到 VREF+ 之间的输出电压。

各 DAC 通道引脚的模拟输出电压通过以下公式确定: