先以一位全加器为例:Xi、Yi代表两个加数,Cin是地位进位信号,Cout是向高位的进位信号。列表有:

| Xi | Yi | Cin | Sum | Cout |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

由左边表格可知:

Sum=X’Y'Cin+X'YCin'+XY'Cin'+XYCin=X'(Y⊕Cin)+X(Y⊙Cin)=X'(Y⊕Cin)+X(Y⊕Cin)'=X⊕Y⊕Cin

Cout=X’YCin+XYCin'+XY'Cin+XYCin=XY+(X⊕Y)Cin

如果取:P=X⊕Y ; G=XY

那么:Sum=P⊕Cin Cout=PCin+G

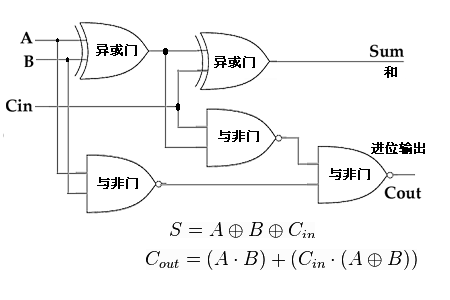

图中对Cout的公式进行了,即Cout'=(AB)'(PCin)'=(AB)'((A⊕B)Cin)'

下面是全加器的门级Verilog语言描述:

module Fadd(x,y,Cin,Cout,Sum); input x,y,Cin; output Cout,Sum; wire a,b,c; xor xor1(a,x,y); xor2(Sum,a,Cin); and and1(b,x,y); and2(c,Cin,a); or or1(Cout,b,c); endmodule

全加器的行为描述:

1 module add(x,y,Cin,Sum,Cout); 2 input x,y,Cin; 3 output Sum,Cin; 4 assign Sum=x^y^Cin; 5 assign Cout=x&y+(x^y)&Cin; 6 endmodule

module add_N(x,y,Cin,Cout,Sum); input x,y,Cin; output Sum,Cout; assign {Cout,Sum}=x+y+Cin; endmodule

利用行为级描述的Verilog全加器可以很简单的扩展成4位或者16位等全加器:

module add_4(x,y,Cin,Cout,Sum); input [3:0]x,y; input Cin; output [3:0]Sum; output Cout; assign {Cout,Sum}=x+y+Cin; endmodule

module add_N(x,y,Cin,Cout,Sum); input [N-1:0]x,y; input Cin; output [N-1:0]Sum; output Cout; assign {Cout,Sum}=x+y+Cin; endmodule