并行语句概述

概念和定义

相对于传统的软件描述语言,并行语句结构是最具VHDL特色的:并行运行。

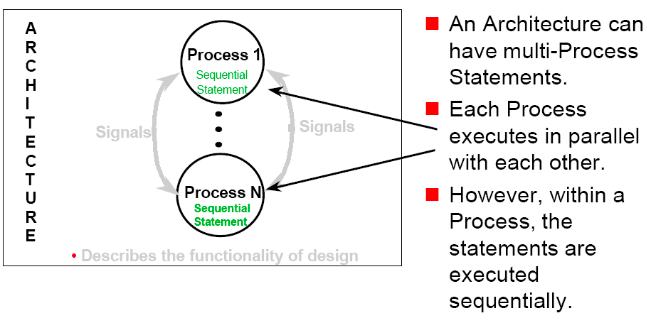

物理意义:硬件连接关系 每一并行语句内部的语句运行方式可以有两种不同的方式,即并行执行方式(如块语句)和顺序执行方式(如进程语句)。

因此,VHDL并行语句勾画出了一幅充分表达硬件电路的真实的运行图景

种类

格式

并行语句在结构体中的使用格式如下: ARCHITECTURE 结构体名 OF 实体名 IS 说明语句; BEGIN 并行语句; END ARCHITECTURE 结构体名;

并行语句介绍

1、并行信号赋值语句

格式

<signal_name> <= <expression>;

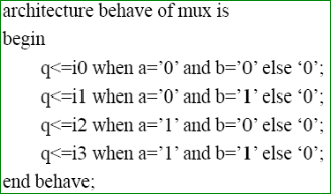

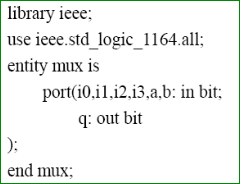

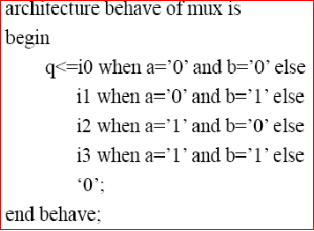

2、条件信号赋值语句

多驱动源问题

驱动源实际上就是对信号赋值的表达式.

在结构中,信号只能被赋值一次。

等价于

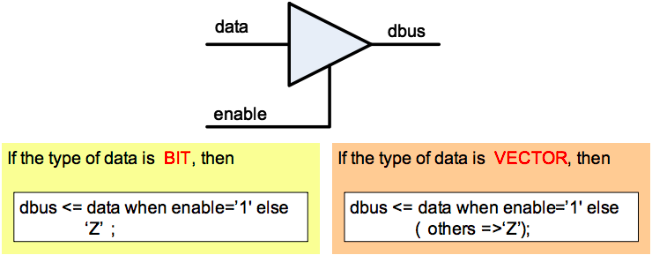

小提示:在赋值时,存在有bit 和 vector之分。

当条件信号赋值语句的else时,

3、选择信号赋值语句

注意考虑和不考虑所有的条件生成硬件可能不同

WHEN OTHERS 语句代表了没有被具体说明的其他条件。

With和When的区别

在with语句中的每一个选项必须是唯一的 和When语句相比,

在with语句中,选项由with表达式指定,而在when语句中,选项可以是分立的表达式。

When语句具有优先级,而with语句没有优先级(因为每个选项之间是互斥的)

Tips:

VHDL(with) == C++(Switch)

VHDL(when) == C++(if)

VHDL(when …… else ) == C++(if …… else if …… else )

4、进程语句(状态机)

进程(PROCESS)语句提供了一种用算法(顺序语句)描述硬件行为的方法。

进程实际上是用顺序语句描述的一种进行过程,也就是说进程用于描述顺序事件。

PROCESS语句结构包含了一个代表着设计实体中部分逻辑行为的、独立的顺序语句描述的进程。

一个结构体中可以有多个并行运行的进程结构,而每一个进程的内部结构却是由一系列顺序语句来构成的。

进程定义的语法格式

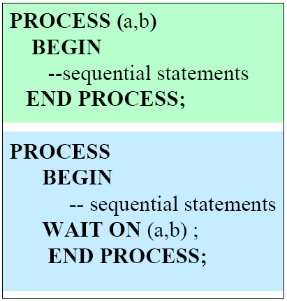

[进程标号:] process [(敏感信号表)] [is] [进程说明部分] begin 顺序描述语句 end process [进程标号];

进程两种状态:

1、执行

2、挂起

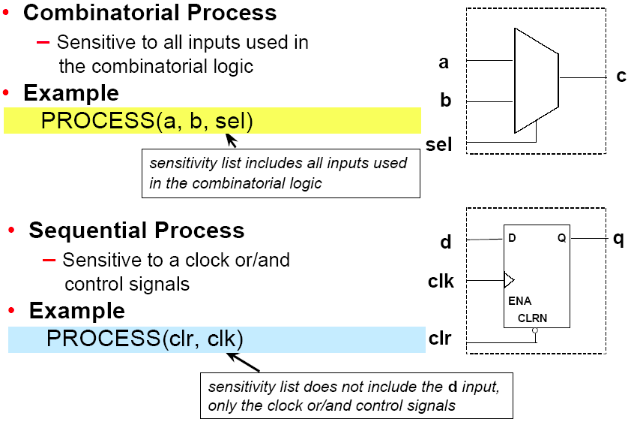

组合逻辑电路 和 时钟逻辑电路

进程语句的执行

敏感表与wait语句

敏感表和WAIT语句等效,但WAIT语句更多样化

一个进程不可既有敏感表,又有WAIT语句,但要有一种

☆ 逻辑综合对WAIT有严格的限制(只有wait until语句可以综合)

进程内部执行时间(process 到end process)

行为仿真角度:一个VHDL模拟器最小分辨时间δ

综合和硬件运行角度:执行时间为0

WAIT UNTIL 语法:

wait until condition;

condition条件满足时才会执行 可综合

architecture arc2 of process_wait is begin process begin wait until clk'event and clk = '1'; q<=d; end process; end architecture;

WAIT ON 语法:

wait on sensitivity list;

sensitivity list信号敏感表里任意一个发生变化才会执行

不太可能综合(特别是时序电路,实际电路不可能接受上升沿和下降沿触发)

WAIT FOR 语法:

wait for time;

只做仿真,不可综合,用于产生延时

5、块语句

块(BLOCK)语句是一种将结构体中的并行描述语句进行组合的方法,

它的主要目的是改善并行语句及其结构的可读性,或是利用BLOCK的保护表达式关闭某些信号。

格式

块标号:BLOCK [(块保护表达式)] [IS] 接口说明; 类属说明; BEGIN 并行语句; END BLOCK [块标号];

6、元件例化语句

元件例化就是将预先设计好的设计实体定义为一个元件,

然后利用特定的语句将此元件与当前的设计实体中的指定端口相连接,从而为当前设计实体引入一个新的低一级的设计层次。

元件例化语句由两部分组成,前一部分是将一个现成的设计实体定义为一个元件的语句,第二部分则是此元件与当前设计实体中的连接说明。

COMPONENT语句指定了本结构体中所调用的是哪一个现成的逻辑描述模块。它既可以出现在结构体中,也可以出现在程序包中。

COMPONENT语句的书写格式为:

COMPONENT 元件名 [IS] [GENERIC(类属表)说明;] [PORT (端口名表)说明;] END COMPONENT 元件名;

元件例化语句

如果在描述一个元件A时,要引用(用“例化”(Instantiations)一词表示这种引用)子元件B、C和D,可以采用元件例化语句引用一个子元件。

元件例化语句的格式为:

例化标号名:元件名PORT MAP(<关联表>);

元件名是COMPONENT语句中说明的名字。元件说明中的端口称为局部端口。

在元件例化语句时,端口的关联表必须将每个局部端口与实际连接的信号联系起来。

Tips:

元件例化语句,好比英语作文中的句型或者是短语搭配,实际端口不一样。通过实例化操作,能把对应的 sb,sth,be 对上号。

7、生成语句

生成语句作用:复制

根据某些条件设置好某一元件或设计单位,可以用生成语句复制一组完全相同的并行元件或设计单元电路

[标号:] for 循环变量 in 取值范围 generate [声明部分] begin 并行语句; end generate [标号];

取值范围: 表达式 to 表达式 或者 表达式 downto 表达式

8、并行过程调用语句

并行过程调用语句作为并行语句直接出现在结构体中

调用语句可以为:

过程(Procedure)或函数(Function)

调用的语法格式:

过程名/函数名(关联参数表)

函数和过程统称子程序

函数语法格式:

FUNCTION function_name (input_parameters) RETURN data_type IS [声明部分]; BEGIN 顺序语句; RETURN 声明名; END [FUNCTION] [function_name];

函数一般定义在包中(声明及实现)

过程语法格式:

PROCEDURE procedure_name (mode_parameters) IS [声明部分] BEGIN 顺序语句; END [PROCEDURE ] [procedure_name];

过程一般定义在包中(声明及实现)

函数和过程的区别

函数参数只能使用IN,过程中参数为IN、INOUT、OUT三种

函数只有一个返回值,过程可以通过参数返回多个返回值