Makefile文件相当于是一种脚本编程语言,目的是实现自动化编译。编写makefile文件的过程中可以使用变量、控制结构和函数等一般编程语言的特性。

Makefile文件的组成内容、makefile文件的书写,makefile文件使用实例。

Makefile文件包含:makefile文件一般命名为makefile或者Makefile,make工具能直接识别执行。如果指定makefile文件的话可以用命令$make –f <文件名>来执行,makefile文件中也可以用include关键字包含其他的makefile文件,文件名可以使用包含路径的文件名或者文件名通配符,比如:

include /home/admin/*.make

该语句中将/home/admin/文件夹中所有扩展名为.make的文件包含进来。

Makefile文件的书写

1.基本规则

基本规则有两种格式,

targets:prerequisites

command

targets:prerequisites ;command

command

“targets”表示目标,“prerequisites”是依赖的文件,“command”是指命令,这一段代码合起来的意思就是,通过command命令,使用prerequisites文件,生成targets目标。为了便于理解,下面举例说明:

main.o: main.c defs.h

gcc –c main.c

上边这一段代码如果我们用shell中命令的话就是$gcc –c main.c defs.h –o main最后生成main.o文件。在这里一定要注意的是,命令也就是“command”前边要使用Tab而不是空格。

2.隐式规则

上边的规则理解之后对于隐式规则的理解会简单很多,隐式规则就是make工具具有的自我推导的功能。比如make工具会自动使用 gcc –c 命令将一个main.c文件编译成main.o。这样的话上边生成main.o就可以这样写main.o:defs.h 。

3.伪目标

伪目标像是C语言中的一个标号,只执行命令,不产生任何文件。伪目标不是真正的文件,所以make工具无法生成其依赖关系,并且决定该目标是否需要执行。使用一个特殊的符号标记伪目标 .PHONY ,比如

.PHONY : clean

表示不管clean这个文件是否存在,都将其声明为一个伪目标。要运行clean这个目标的时候,只有在启动make工具是制定运行该目标才行。下面代码为运行clean伪目标。

$make clean

最后举例说明一下:

all : main.o kbd.o command.o .PHONY : all main.o : main.c defs.h gcc -c main.c kbd.o : kbd.c defs.h command.h gcc -c kdb.c command.o : command.c defs.h command.h buffer.h gcc -c command.c

上面的all就是一个伪目标,这个makefile文件中all这个伪目标依赖于其他的目标,也就是说伪目标也可以依赖于实际的目标。

4.使用通配符

make工具支持3中通配符“*”、“?”、“[...]”,具体的用法就是普通的通配符的用法。

5.使用命令

在makefile中可以执行shell中的命令,因此许多工作可以交给shell去完成。

显示命令:将“@”字符加在命令行前边,命令行在执行的时候不会显示出来,比如 @echo compling...... 在make执行之后不会显示出echo compling......。另外一种方法是make工具在执行的时候可以通过命令 make -n 或者 make --just-print 只显示命令不运行,或使用命令 make -s 、 make --silent 禁止显示所有命令。

命令出错: make -i 或者 make --ignore-errors 来忽略错误。

6.使用变量

makefile文件中可以使用变量,这里的变量不是数值而是字符串,相当于C语言中宏定义,在makefile文件的执行过程中会原样的展开在所使用的的地方。变量名可以包含字符、数字、下环线,并且大小写敏感。

makefile文件中变量的使用主要目的为是为了方便移植,下边举例说明:

CC = gcc FLAGS = -c objects = main.o kbd.o command.o edit : $(objects) $(CC) -o edit $(objects) main.o : main.c defs.h $(CC) $(FLAGS) main.c kbd.o : kbd.c defs.h command.h $(CC) $(FLAGS) kbd.c command.o : command.c defs.h command.h $(CC) $(FLAGS) command.c clean: rm $(objects) .PHONY: clean

makefile文件中变量声明的时候要赋值,引用的时候格式是“$()”

变量的使用中最容易出现问题的是变量中的变量,makefile文件中文定义变量值得时候有4种办法:

(1)使用 “=” 操作符

“=” 左侧是变量,右侧是变量的值。右侧的值可以定义在文件中任何一个地方,也就是说右侧的值不一定是定义好的值,也可以是后边定义的值。下边举例说明:

foo = $(bar) bar = $(ugh) ugh = Huh? all : echo $(foo) #输出变量foo

执行该makefile文件的结果是:

$make -s all

Huh?

输出的结果是

$(foo)的值,根据定义$(foo)是$(bar)的值,$(bar)的值是$(ugh)的值,$(ugh)的值是Huh?。由此可知,makefile文件中变量是可以使用后边的变量定义的,这种定义方式在递归定义的时候会存在潜在的危险。

(2)使用 “:=” 操作符

使用 “:=” 操作符定义变量可以避免递归定义的危险,使用其进行变量定义的时候,前面变量不能使用后边的变量,只能使用前面已经定义好的变量。

(3)使用 “?=”操作符

该操作符的含义就是,如果变量之前没有被定义过,那么变量的值就被定义了,如果变量的值之前已经定义了,那么该赋值语句什么也不做。举例说明:

a :=hello b ?=world a ?=HELLO all: echo $(a) # 输出变量a echo $(b) #输出变量b .PHONY : all

执行结果:

$make -s all

hello

world

从结果中可以看出来a之前被定义了,因此不改变,b之前没有被定义,所以被定义为world。

(4) 使用 “+=”符号

该符号是追加变量的值,比如

CC= gcc

FLAGS = -c #使用-c选项 FLAGS += -O2 #编译选项,使用O2优化

上边的变量最后使用的时候 $(CC) $(FLAGS) 就相当于 gcc -c -O2 。

Makefile文件实例

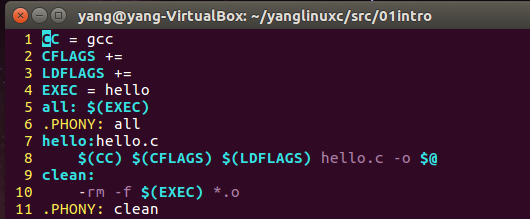

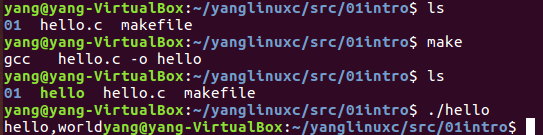

最后实现一个makefile文件是实例,这是hello程序的makefile文件以及执行:

用make执行结果:

总结:makefile文件的学习抓住三个方面就行了,目的、规则、使用方法。makefile文件的目的就是为了实现自动化管理代码的编译,可以说是一个工具,是一个根据自己需求可以定制的工具。使用好makefile文件要了解好规则,了解好使用办法就够了。第一遍看这个makefile文件的时候觉得挺高大上的而感觉,那时候是跟着书走的,书上讲到什么,就自己实现什么,觉得还挺神奇。但是,那个时候没有真正了解makefile文件的目的和便捷性在哪。经过老师的反复强调,我自己又重新看着一部分,再回过头来看的时候有点顿悟了,突然间就都理解了,理解之后才会觉得这个东西没有想象中的难,开始尝试去写,去实践,去熟练。工具主要还是为了方便使用,工具的学习没有什么技巧就是多练习,熟能生巧。