BF533的SPORT接口

1.特性

bf533有两个SPORT口(synchronous serial Port),即同步串行接口。完全独立的接收和发送通道,且每个通道都具有缓冲,最高速度可达SCLK/2。最大支持32bit字长,可进行硬件u-law和A-law压缩。结构框图如下:

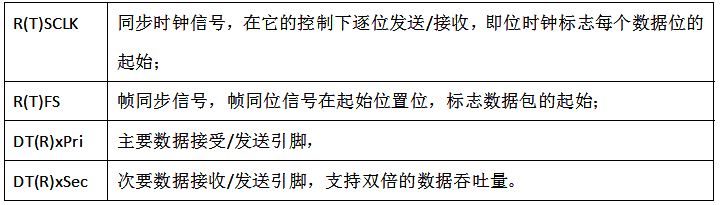

2.接口信号说明

3.串行时钟T/RCLK

由SPORTx_TCLKDIV和SPORTx_RCLKDIV两个16位寄存器决定分频的值,假设系统时钟为SCLK,则串行时钟的计算公式为:

![]()

例如,SCLK=133MHz,RCLKDIV = 4时,得到的RCLK freq = 133/(2*(4+1))=13.3MHz。

4.帧同步信号T/RFS

帧同步信号的分频是由SPORTx_TFSDIV和SPORTx_RFSDIV寄存器的值决定的,计算公式如下:

![]()

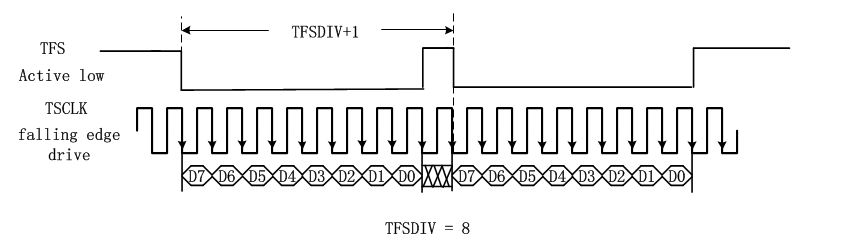

注意到,帧同步信号的频率是对串行时钟频率的分频,而不是对系统时钟SCLK的分频,因此,在相邻的两个帧同步信号之间,有(T/RFSDIV+1)个串行位时钟,看下图的说明:

图 1 :

因此,我通常并不计算T/RFS信号的频率,而是把它理解为Number of transmit clock cycles counted before generatingTFS pulse,该值就等于T/RFSDIV+1.图中所示TFSDIV = 8,8+1 = 9 > 8因此两个字节的数据之间有一个bit的无关位。

5. 工作模式

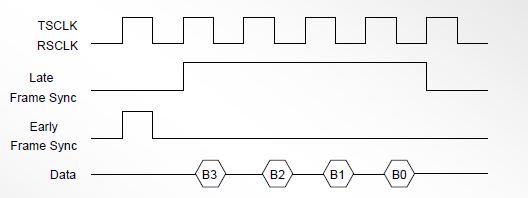

1)提前帧同步和延迟帧同步

提前同步模式,帧同步信号比数据早一个串行时钟周期。

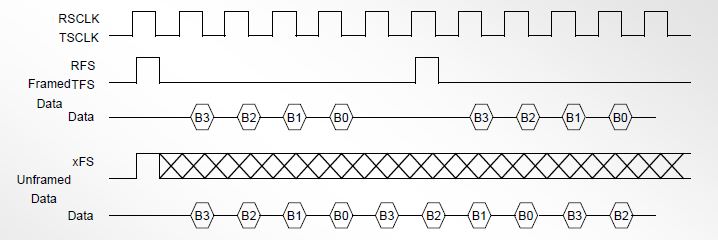

2)有帧模式和无帧模式

有帧模式:对于每一个字,都需要一个帧信号;

无帧模式:在第一个字传送后,忽视帧信号,但是帧信号是一直按照我们的设置继续产生的,只不过被忽视了;

5.程序实例与讲解:

1)发送端设置:

void Init_Sport1_TX(int TCLKDIV) { //SPORTx_TCLK frequency = (SCLK frequency)/(2 x (SPORTx_TCLKDIV + 1)) *pSPORT1_TCLKDIV = TCLKDIV; //the number of cycles between frame sync pulses *pSPORT1_TFSDIV = 8; // driving data with rising edge,late frame sync,active low //sync require, inter FS used, internal tclk used *pSPORT1_TCR1 = LATFS|LTFS|TFSR|ITFS| ITCLK; // 8 bit word length *pSPORT1_TCR2 = 7; // 发送使能 *pSPORT1_TCR1 = (*pSPORT1_TCR1 | TSPEN); }

按照该程序设置,可以得到图1所示的波形。

2)接收端设置:

一般情况下,接收端的设置和发送端一致,只不过接收端一般使用发送端的帧同步信号FS和位时钟SCLK所以配置为external FS和external SCLK

void Init_Sport1_RX(int RCLKDIV) { //SPORTx_RCLK frequency = (SCLK frequency)/(2 x (SPORTx_RCLKDIV + 1)) *pSPORT1_RCLKDIV = RCLKDIV; //the number of cycles between frame sync pulses *pSPORT1_RFSDIV = 8; // sync require, external FS used, external rclk used *pSPORT1_RCR1 = LARFS|LRFS|RFSR; // 8 bit word length *pSPORT1_RCR2 = 7; *pSPORT1_RCR1 = (*pSPORT1_RCR1 | RSPEN);//使能SPORT1接收 }

3)发送数据:

*pSPORT1_TX16 =d; while((*pSPORT1_STAT&0x0040)!=0x0040); /*等待上一次发送完成 */

4)接收数据:

while(!(*pSPORT1_STAT & RXNE));//查看SPI传输状态是否有数据需要接收 i = *pSPORT1_RX16; //读取数据