第四章 处理器体系结构

第一节 Y86指令集体系结构

一、程序员可见的状态

1.含义:

每条指令都会读取或修改处理器状态的某些部分

2.“程序员”:

可以是用汇编代码写程序的人,也可以是产生机器级代码的编译器。

3.具体的处理器状态:类似于IA32

- 有8个程序寄存器,%eax,%ecx,%edx,%ebx,%esi,%edi,%esp,%ebp

- 处理器的每个程序寄存器存储一个字

- 寄存器%esp被入栈、出栈、调用和返回指令作为栈指针。在其他情况下,寄存器没有固定的含义或固定值。

- 有三个一位的条件码:ZF,SF,OF,它们保存最近的算术或洛基指令所造成英雄的有关信息。

- 程序计数器PC存放当前正在执行指令的地址。

4.存储器

Y86程序用虚拟地址来引用存储器位置,硬件和操作系统软件联合起来将虚拟地址翻译成实际或物理地址

5.状态码stat

它表明程序执行的总体状态,会指示是正常运行还是出现了某种异常。

二、Y86指令

Y86指令集基本上是IA32指令集的一个子集,只包括四字节整数操作,寻址方式比较少,操作也较少。

汇编码表示和字节编码参见课本232页。

1.movl指令

IA32的movl指令分为四种:

irmovl,rrmovl,mrmovl,rmmovl前面的两个字母是在显式的指定源操作数和目的操作数的格式,第一位是源操作数,第二位是目的操作数。

(1)源操作数

可以是:

i-立即数

r-寄存器

m-存储器(2)目的操作数

可以是:

r-寄存器

m-存储器※这里的存储器引用方式是简单的基址和偏移量形式,寻址方式不支持第二变址寄存器和任何寄存器值的伸缩

※两个操作数不能都是来自存储器,也不允许将立即数传送到存储器

2.四个整数操作指令

addl 加

subl 减

andl 与

xorl 异或并且它们只对寄存器数据进行操作(区别于IA32,后者还允许对存储器数据进行这些操作)。

这些指令会设置三个条件码:

ZF-零

SF-符号

OF-溢出3.七个跳转指令——分支控制

jmp 直接跳转

jle(SF^OF)|ZF 有符号数≤

jl SF^OF 有符号<

je ZF 相等/零

jne ~ZF 不相等/非零

jge ~(SF^OF) 有符号≥

jg ~(SF^OF)&~ZF 有符号>4.六个条件传送指令

cmovle

cmovl

cmove

cmovne

cmovge

cmovg这些指令的格式与寄存器-寄存器传送指令rrmovl一样,但是只有当条件码满足所需要的约束时,才会更新目的寄存器的值。

5.call和ret

call指令将返回地址入栈,然后跳到目的地址,ret指令从这样的过程调用中返回。

6.pushl和popl

实现入栈和出栈

7.halt指令

halt指令停止指令的执行,执行此指令会导致处理器停止,并将状态码设置为HLT。

类比IA32:hlt指令与之类似,但是IA32的应用程序不允许使用这条指令,因为它会导致整个系统暂停运行。

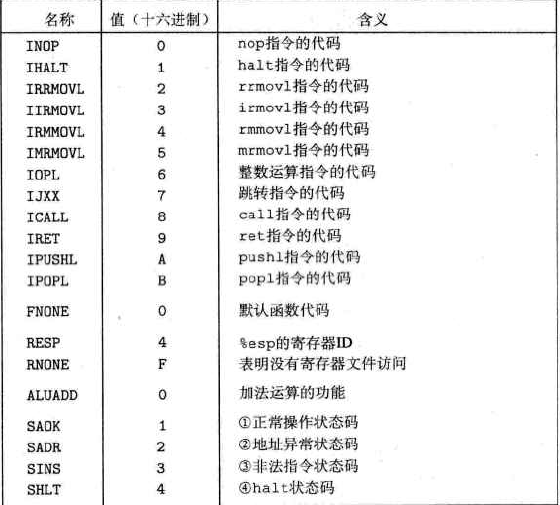

三、指令的字节级编码

每条指令需要1-6个字节不等,每条指令的第一个字节表明指令的类型。

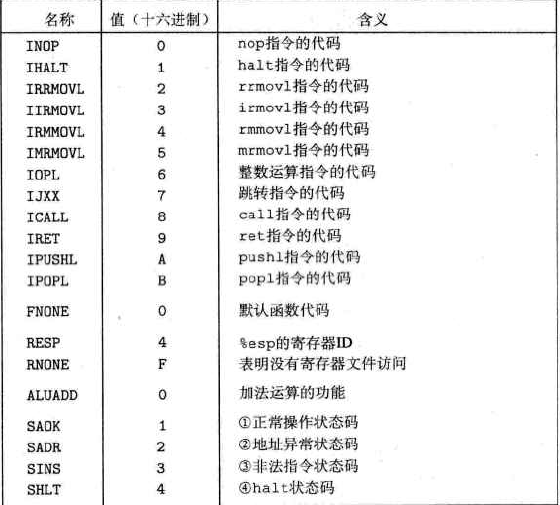

1.第一个字节

这个字节分为两个部分,每个部分4位:

- 高四位:代码部分,值域为0~0xB

- 第四位:功能部分,功能值只有在一组相关指令共用一个代码时才有用。

比如:课本第233页,Y86指令集的功能码:

整数操作里代码部分均为6,功能部分区分addl,subl,andl,xorl

分支指令里代码部分均为7

传送指令里代码部分均为2

这里要注意rrmovl归到了传送指令里,前面说过它们有相同的指令代码

8个程序寄存器中每个都有相应的0~7的寄存器标识符,程序寄存器存在CPU中的一个寄存器文件中,这个寄存器文件就是一个小的、以寄存器id作为地址的随机访问存储器。

当需要指明不应访问任何寄存器时,用ID值0xF表示

2.有的需要额外的字节

(1)附加的寄存器指示符字节

指定一个或两个寄存器,例如rA或者rB。

- 没有寄存器操作数的指令,例如分支指令和call指令,就没有寄存器指示符字节。

- 只需要一个寄存器操作数的指令(irmovl,pushl,popl)将另一个寄存器指示符设为0xF

(2)附加的4字节常数字

这个字的用处:

1.irmovl的立即数数据

2.rmmol和mrmovl的地址指示符的偏移量

3.分支指令和调用指令的目的地址注意事项

1.分支指令和调用指令的目的地址是一个绝对地址

2.所有整数采用小端法编码※指令集的重要性质:

字节编码必须有唯一的解释

习题4.1的解答技巧:这道题只需要按照指令编码各个位上的值去对应即可,比如第一行,irmovl的指令是30f,目的操作数是%ebx,查表得3,源操作数是立即数15,转为16进制数为00 00 00 0f,小端法表示为0f 00 00 00,组合在一起即为30f30f000000。

习题4.2的解答技巧:这道题要注意划分数字为不同的指令。

四、Y86异常

1.状态码Stat的可能取值

Stat描述程序执行的总体状态

1. AOK 正常操作

2. HLT 处理器执行halt指令

3. ADR 遇到非法地址

4. INS 遇到非法指令2.出现异常时?

Y86——处理器停止运行指令。

更完整?调用一个异常处理程序

五、Y86程序

具体范例参见课本第238-239页

Y86和IA32代码对比来看,本质上两者相同,但是:

1.Y86和IA32的区别

1.Y86有时需要两条指令来完成IA32一条指令就能完成的事

2.Y86没有伸缩寻址模式2.注意的一些:

(1)命令指明应该将代码或数据放在什么位置,以及该如何对齐

(2)以“.”开头的是汇编器命令

(3)创建Y86代码的唯一工具是汇编器,所以程序员必须执行本来通常交给编译器、链接器和运行时系统来完成的任务。

六、一些Y86指令的详情

特指popl和pushl,在压入/弹出栈指针%esp的时候,有两种不同的约定:

1.压入/弹出%esp的原始值

2.压入/弹出%esp-/+4后的值经过试验,发现默认压入弹出的都是原始值。

pushl在不同的x86模型之间有歧义,但是popl没有。

第二节 逻辑设计和硬件控制语言HCL

电子电路中,用1.0V左右的高电压表示逻辑1,用0.0V左右的低电压表示逻辑0.

一、逻辑门

1.逻辑门产生的输出,等于它们输入位值的某个布尔函数。

2.

AND &&

OR ||

NOT !3.逻辑门只对单个位的数进行操作,而不是整个字。

4.逻辑门总是活动的,输入变化输出很快就跟着变化。

二、组合电路和HCL布尔表达式

对应EDA学习时的组合逻辑电路

1.构建计算块(组合电路)时的限制

- 两个或多个逻辑门的输出不能连接在一起

- 必须无环

2.组合逻辑电路和c语言中逻辑表达式的区别

- 组合电路的输出会持续响应输入变化,c语言表达式只有在执行过程中被遇到才求值

- 逻辑门只对0和1操作,c语言表达式中参数可以是任意整数,0是FALSE,不是0的都是TRUE

- c的逻辑表达式可能被部分求值

三、字级的组合电路和HCL整数表达式

这里面需要注意几个零碎的知识点:

- 所有字级的信号都声明为int,不指定字的大小

-

多路复用函数用情况表达式来描述,具体格式如下:

[ select_1 : expr_1 select_2 : expr_2 …… ]从逻辑上讲,这些选择表达式是顺序求值的。

- 选择表达式为1时,表示如果前面没有情况被选中,就选择这种情况

-

不同 选择表达式之间允许不互斥

四、集合关系

判断集合关系的通用格式是:

iexpr in {iexpr1,iexpr2,...,iexprk}iexpr等都是整数表达式。

五、存储器和时钟

对应EDA学习时的时序逻辑电路

1.时序电路的两类存储器设备:

(1)时钟寄存器(简称寄存器):储存单个位或字。

(2)随机访问储存器(简称储存器):储存多个字,用地址选择该读/写哪个字。

寄存器分为“硬件寄存器”和“程序寄存器”。

2.Y86处理器

它会用时钟寄存器保存程序计数器PC,条件代码CC和程序状态Stat。

这一节学习的时候对比EDA课程中学习的Verilog语言的规则,大同小异,但是要注意迁移——把指令对应到位的操作上。

第三节 Y86的顺序实现

SEQ处理器

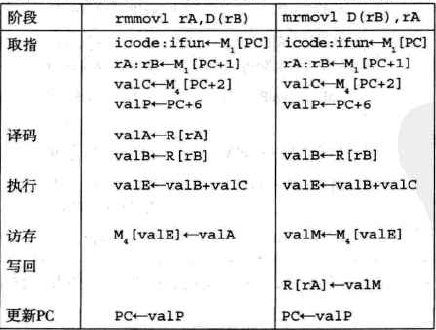

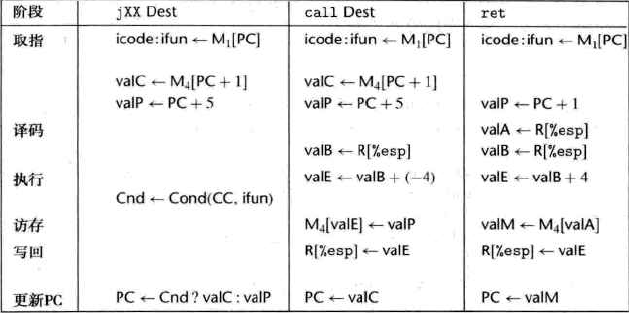

一、将处理组织成阶段

(一)六个基本阶段:

- 取指

- 译码

- 执行

- 访存

- 写回

- 更新PC

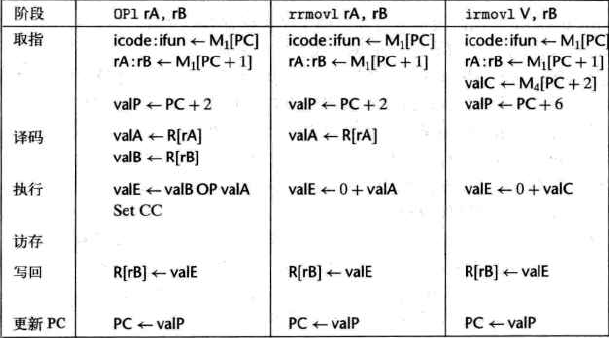

具体每一阶段执行的内容见书250页,根据每一步计算的题目在253页习题4.11,做这个题的时候最要紧是注意每个字符代表的含义是什么,才能进行正确的计算。这个题不难,就是有点麻烦,多看多理解。

(二)具体框架分为四类:

1.针对OPl(整数和逻辑运算),rrmovl(寄存器-寄存器传送)和irmovl(立即数-寄存器传送)2.针对rmmovl和mrmovl3.针对pushl和popl4.针对跳转,call和ret

二、SEQ硬件结构

1.SEQ抽象视图的画法:

- 程序计数器放在寄存器中,位于左下角PC。

- 信息随着线流动,方向是先向上再向右

- 反馈先祖在右边向下

- 所有硬件单元的处理都在一个时钟周期内完成。

- 浅灰色方块表示硬件单元

- 控制逻辑块是用灰色圆角矩形表示的

- 线路的名字在白色椭圆中说明

- 宽度为字长或更窄的数据连接用细线

- 单个位的连接用虚线

2.硬件单元是与各个处理阶段相关联的

有六个基本阶段,见上。具体关联参见258页图。

三、SEQ的时序

SEQ的实现包括组合逻辑和两种存储器设备:

1.时钟寄存器——程序计数器和条件码寄存器

2.随机访问存储器——寄存器文件、指令存储器和数据存储器对于上面提到的五个硬件单元,可以分成两类:

1.组合逻辑——指令存储器

2.时序——剩下四个剩下四个中:

条件码寄存器——只在执行整数运算指令时装载

数据存储器——只在执行rmmovl、pushl或call时写入

寄存器文件——两个写端口允许每个时钟周期更新两个程序寄存器。特殊寄存器?0xF表示此端口不应执行写操作。※Y86指令集下的组织原则:

- 处理器从来不需要为了完成一条指令的执行而去读由该指令更新了的状态。

总结就是,用时钟来控制状态元素的更新,值通过组合逻辑传播。

四、SEQ阶段的实现

在控制逻辑中必须被显式引用的常数:

- nop指令:PC+1,别的只经过不改变

-

halt指令:使处理器状态变为HLT,导致停止运行

1.取指阶段

以PC为第一个字节,读6个字节。

-

两个逻辑块(从第一个字节中分出,各四位)

icode-指令代码 ifun-指令功能 -

三个一位的信号(根据icode值计算)

instr_valid-发现不合法的指令 need_regids-包含寄存器指示符字节吗 need_valC-包括常数字吗后五个字节是寄存器指示符字节和常数字的组合编码。

2.译码和写回阶段

都需要访问寄存器文件,根据四个端口的情况,判断应该读哪个寄存器产生信号valA、valB

3.执行阶段

(1)包括算术/逻辑单元ALU,输出的是valE。

ALU常被用作加法器

(2)包括条件码寄存器

零,符号,溢出,产生信号set_cc

4.访存阶段

- 读或者写程序数据。

两个数据块产生存储器地址和存储器输入证据的值,两个产生控制信号表明应该是读还是写。

- 根据icode,imem_error,instr_valid,dmem_error,从指令执行的结果计算状态码Stat。

5.更新PC阶段

会产生程序计数器的新值。参考资料

课本。

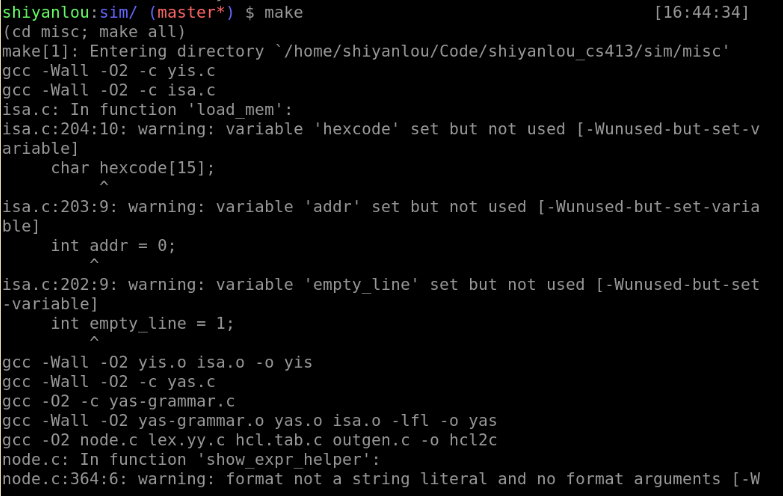

实验

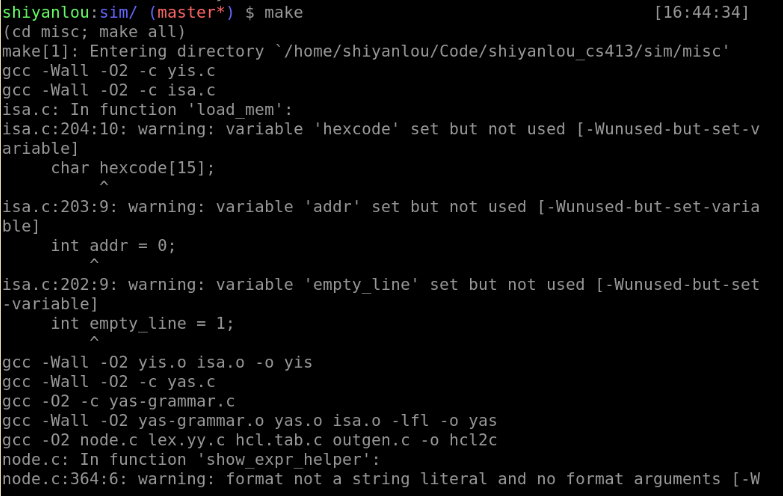

运行make指令后

查看目录下内容,可以看到只有.ys文件

用make all命令编译后

编译后查看目录下内容,可以看到已经有编译后的.yo文件,用vim进入后可以查看

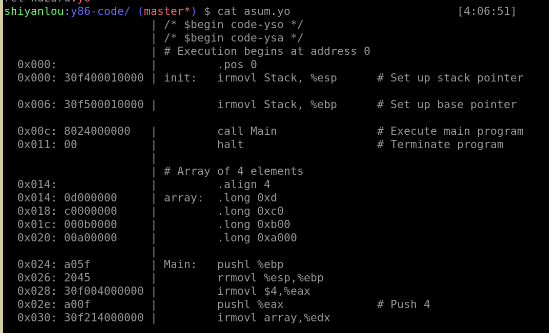

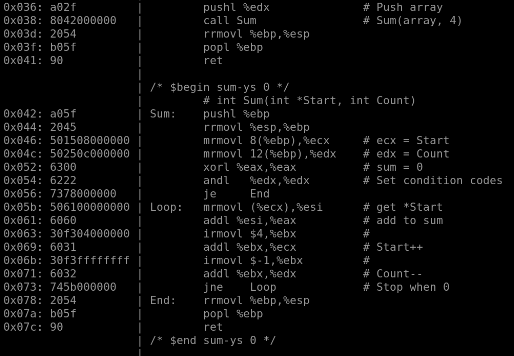

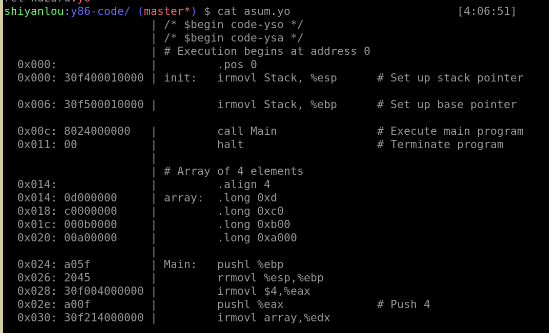

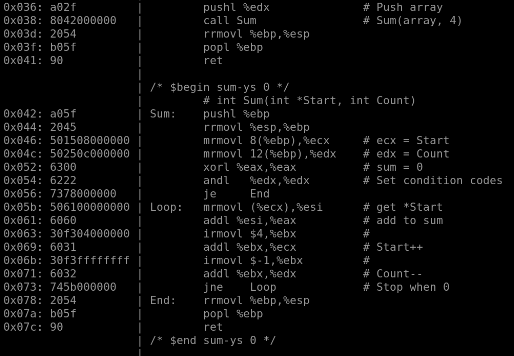

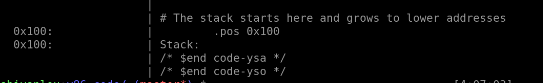

课本第239页图4-7上的代码,在系统中叫做asum.yo,把它的内容打印在屏幕上:

可以看出来和课本240页的结果是一致的。

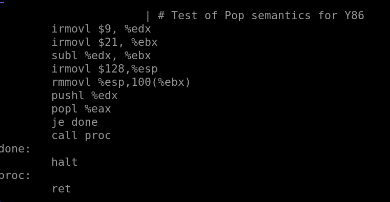

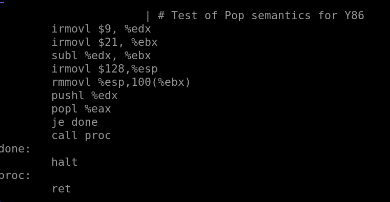

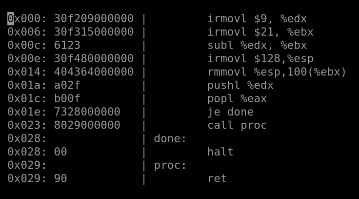

课本第251页图4-17,我先用建立了一个417.ys进入后,输入:

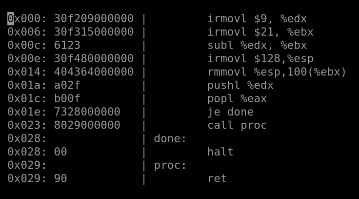

然后用make 417.yo编译,编译后用vim进入417.yo

第四章 处理器体系结构

第一节 Y86指令集体系结构

一、程序员可见的状态

1.含义:

每条指令都会读取或修改处理器状态的某些部分

2.“程序员”:

可以是用汇编代码写程序的人,也可以是产生机器级代码的编译器。

3.具体的处理器状态:类似于IA32

- 有8个程序寄存器,%eax,%ecx,%edx,%ebx,%esi,%edi,%esp,%ebp

- 处理器的每个程序寄存器存储一个字

- 寄存器%esp被入栈、出栈、调用和返回指令作为栈指针。在其他情况下,寄存器没有固定的含义或固定值。

- 有三个一位的条件码:ZF,SF,OF,它们保存最近的算术或洛基指令所造成英雄的有关信息。

- 程序计数器PC存放当前正在执行指令的地址。

4.存储器

Y86程序用虚拟地址来引用存储器位置,硬件和操作系统软件联合起来将虚拟地址翻译成实际或物理地址

5.状态码stat

它表明程序执行的总体状态,会指示是正常运行还是出现了某种异常。

二、Y86指令

Y86指令集基本上是IA32指令集的一个子集,只包括四字节整数操作,寻址方式比较少,操作也较少。

汇编码表示和字节编码参见课本232页。

1.movl指令

IA32的movl指令分为四种:

irmovl,rrmovl,mrmovl,rmmovl前面的两个字母是在显式的指定源操作数和目的操作数的格式,第一位是源操作数,第二位是目的操作数。

(1)源操作数

可以是:

i-立即数

r-寄存器

m-存储器(2)目的操作数

可以是:

r-寄存器

m-存储器※这里的存储器引用方式是简单的基址和偏移量形式,寻址方式不支持第二变址寄存器和任何寄存器值的伸缩

※两个操作数不能都是来自存储器,也不允许将立即数传送到存储器

2.四个整数操作指令

addl 加

subl 减

andl 与

xorl 异或并且它们只对寄存器数据进行操作(区别于IA32,后者还允许对存储器数据进行这些操作)。

这些指令会设置三个条件码:

ZF-零

SF-符号

OF-溢出3.七个跳转指令——分支控制

jmp 直接跳转

jle(SF^OF)|ZF 有符号数≤

jl SF^OF 有符号<

je ZF 相等/零

jne ~ZF 不相等/非零

jge ~(SF^OF) 有符号≥

jg ~(SF^OF)&~ZF 有符号>4.六个条件传送指令

cmovle

cmovl

cmove

cmovne

cmovge

cmovg这些指令的格式与寄存器-寄存器传送指令rrmovl一样,但是只有当条件码满足所需要的约束时,才会更新目的寄存器的值。

5.call和ret

call指令将返回地址入栈,然后跳到目的地址,ret指令从这样的过程调用中返回。

6.pushl和popl

实现入栈和出栈

7.halt指令

halt指令停止指令的执行,执行此指令会导致处理器停止,并将状态码设置为HLT。

类比IA32:hlt指令与之类似,但是IA32的应用程序不允许使用这条指令,因为它会导致整个系统暂停运行。

三、指令的字节级编码

每条指令需要1-6个字节不等,每条指令的第一个字节表明指令的类型。

1.第一个字节

这个字节分为两个部分,每个部分4位:

- 高四位:代码部分,值域为0~0xB

- 第四位:功能部分,功能值只有在一组相关指令共用一个代码时才有用。

比如:课本第233页,Y86指令集的功能码:

整数操作里代码部分均为6,功能部分区分addl,subl,andl,xorl

分支指令里代码部分均为7

传送指令里代码部分均为2

这里要注意rrmovl归到了传送指令里,前面说过它们有相同的指令代码

8个程序寄存器中每个都有相应的0~7的寄存器标识符,程序寄存器存在CPU中的一个寄存器文件中,这个寄存器文件就是一个小的、以寄存器id作为地址的随机访问存储器。

当需要指明不应访问任何寄存器时,用ID值0xF表示

2.有的需要额外的字节

(1)附加的寄存器指示符字节

指定一个或两个寄存器,例如rA或者rB。

- 没有寄存器操作数的指令,例如分支指令和call指令,就没有寄存器指示符字节。

- 只需要一个寄存器操作数的指令(irmovl,pushl,popl)将另一个寄存器指示符设为0xF

(2)附加的4字节常数字

这个字的用处:

1.irmovl的立即数数据

2.rmmol和mrmovl的地址指示符的偏移量

3.分支指令和调用指令的目的地址注意事项

1.分支指令和调用指令的目的地址是一个绝对地址

2.所有整数采用小端法编码※指令集的重要性质:

字节编码必须有唯一的解释

习题4.1的解答技巧:这道题只需要按照指令编码各个位上的值去对应即可,比如第一行,irmovl的指令是30f,目的操作数是%ebx,查表得3,源操作数是立即数15,转为16进制数为00 00 00 0f,小端法表示为0f 00 00 00,组合在一起即为30f30f000000。

习题4.2的解答技巧:这道题要注意划分数字为不同的指令。

四、Y86异常

1.状态码Stat的可能取值

Stat描述程序执行的总体状态

1. AOK 正常操作

2. HLT 处理器执行halt指令

3. ADR 遇到非法地址

4. INS 遇到非法指令2.出现异常时?

Y86——处理器停止运行指令。

更完整?调用一个异常处理程序

五、Y86程序

具体范例参见课本第238-239页

Y86和IA32代码对比来看,本质上两者相同,但是:

1.Y86和IA32的区别

1.Y86有时需要两条指令来完成IA32一条指令就能完成的事

2.Y86没有伸缩寻址模式2.注意的一些:

(1)命令指明应该将代码或数据放在什么位置,以及该如何对齐

(2)以“.”开头的是汇编器命令

(3)创建Y86代码的唯一工具是汇编器,所以程序员必须执行本来通常交给编译器、链接器和运行时系统来完成的任务。

六、一些Y86指令的详情

特指popl和pushl,在压入/弹出栈指针%esp的时候,有两种不同的约定:

1.压入/弹出%esp的原始值

2.压入/弹出%esp-/+4后的值经过试验,发现默认压入弹出的都是原始值。

pushl在不同的x86模型之间有歧义,但是popl没有。

第二节 逻辑设计和硬件控制语言HCL

电子电路中,用1.0V左右的高电压表示逻辑1,用0.0V左右的低电压表示逻辑0.

一、逻辑门

1.逻辑门产生的输出,等于它们输入位值的某个布尔函数。

2.

AND &&

OR ||

NOT !3.逻辑门只对单个位的数进行操作,而不是整个字。

4.逻辑门总是活动的,输入变化输出很快就跟着变化。

二、组合电路和HCL布尔表达式

对应EDA学习时的组合逻辑电路

1.构建计算块(组合电路)时的限制

- 两个或多个逻辑门的输出不能连接在一起

- 必须无环

2.组合逻辑电路和c语言中逻辑表达式的区别

- 组合电路的输出会持续响应输入变化,c语言表达式只有在执行过程中被遇到才求值

- 逻辑门只对0和1操作,c语言表达式中参数可以是任意整数,0是FALSE,不是0的都是TRUE

- c的逻辑表达式可能被部分求值

三、字级的组合电路和HCL整数表达式

这里面需要注意几个零碎的知识点:

- 所有字级的信号都声明为int,不指定字的大小

-

多路复用函数用情况表达式来描述,具体格式如下:

[ select_1 : expr_1 select_2 : expr_2 …… ]从逻辑上讲,这些选择表达式是顺序求值的。

- 选择表达式为1时,表示如果前面没有情况被选中,就选择这种情况

-

不同 选择表达式之间允许不互斥

四、集合关系

判断集合关系的通用格式是:

iexpr in {iexpr1,iexpr2,...,iexprk}iexpr等都是整数表达式。

五、存储器和时钟

对应EDA学习时的时序逻辑电路

1.时序电路的两类存储器设备:

(1)时钟寄存器(简称寄存器):储存单个位或字。

(2)随机访问储存器(简称储存器):储存多个字,用地址选择该读/写哪个字。

寄存器分为“硬件寄存器”和“程序寄存器”。

2.Y86处理器

它会用时钟寄存器保存程序计数器PC,条件代码CC和程序状态Stat。

这一节学习的时候对比EDA课程中学习的Verilog语言的规则,大同小异,但是要注意迁移——把指令对应到位的操作上。

第三节 Y86的顺序实现

SEQ处理器

一、将处理组织成阶段

(一)六个基本阶段:

- 取指

- 译码

- 执行

- 访存

- 写回

- 更新PC

具体每一阶段执行的内容见书250页,根据每一步计算的题目在253页习题4.11,做这个题的时候最要紧是注意每个字符代表的含义是什么,才能进行正确的计算。这个题不难,就是有点麻烦,多看多理解。

(二)具体框架分为四类:

1.针对OPl(整数和逻辑运算),rrmovl(寄存器-寄存器传送)和irmovl(立即数-寄存器传送)

2.针对rmmovl和mrmovl

3.针对pushl和popl

4.针对跳转,call和ret

这四种按照框架往里套即可。

二、SEQ硬件结构

1.SEQ抽象视图的画法:

- 程序计数器放在寄存器中,位于左下角PC。

- 信息随着线流动,方向是先向上再向右

- 反馈先祖在右边向下

- 所有硬件单元的处理都在一个时钟周期内完成。

- 浅灰色方块表示硬件单元

- 控制逻辑块是用灰色圆角矩形表示的

- 线路的名字在白色椭圆中说明

- 宽度为字长或更窄的数据连接用细线

- 单个位的连接用虚线

2.硬件单元是与各个处理阶段相关联的

有六个基本阶段,见上。具体关联参见258页图。

三、SEQ的时序

SEQ的实现包括组合逻辑和两种存储器设备:

1.时钟寄存器——程序计数器和条件码寄存器

2.随机访问存储器——寄存器文件、指令存储器和数据存储器对于上面提到的五个硬件单元,可以分成两类:

1.组合逻辑——指令存储器

2.时序——剩下四个剩下四个中:

条件码寄存器——只在执行整数运算指令时装载

数据存储器——只在执行rmmovl、pushl或call时写入

寄存器文件——两个写端口允许每个时钟周期更新两个程序寄存器。特殊寄存器?0xF表示此端口不应执行写操作。※Y86指令集下的组织原则:

- 处理器从来不需要为了完成一条指令的执行而去读由该指令更新了的状态。

总结就是,用时钟来控制状态元素的更新,值通过组合逻辑传播。

四、SEQ阶段的实现

在控制逻辑中必须被显式引用的常数:

- nop指令:PC+1,别的只经过不改变

-

halt指令:使处理器状态变为HLT,导致停止运行

1.取指阶段

以PC为第一个字节,读6个字节。

-

两个逻辑块(从第一个字节中分出,各四位)

icode-指令代码 ifun-指令功能 -

三个一位的信号(根据icode值计算)

instr_valid-发现不合法的指令 need_regids-包含寄存器指示符字节吗 need_valC-包括常数字吗后五个字节是寄存器指示符字节和常数字的组合编码。

2.译码和写回阶段

都需要访问寄存器文件,根据四个端口的情况,判断应该读哪个寄存器产生信号valA、valB

3.执行阶段

(1)包括算术/逻辑单元ALU,输出的是valE。

ALU常被用作加法器

(2)包括条件码寄存器

零,符号,溢出,产生信号set_cc

4.访存阶段

- 读或者写程序数据。

两个数据块产生存储器地址和存储器输入证据的值,两个产生控制信号表明应该是读还是写。

- 根据icode,imem_error,instr_valid,dmem_error,从指令执行的结果计算状态码Stat。

5.更新PC阶段

会产生程序计数器的新值。

学习总结

这一章的内容总体学起来比较陌生,看起来很吃力,只能对着课本磕磕绊绊的去做,迁移出来的能力还不够,但是中间关于逻辑门计算的部分由于上学期有Verilog语言的底子,学习的时候可以用作类比,举一反三,从而这一部分的理解相对比较容易。

参考资料

课本。

实验

运行make指令后

查看目录下内容,可以看到只有.ys文件

用make all命令编译后

编译后查看目录下内容,可以看到已经有编译后的.yo文件,用vim进入后可以查看

课本第239页图4-7上的代码,在系统中叫做asum.yo,把它的内容打印在屏幕上:

可以看出来和课本240页的结果是一致的。

课本第251页图4-17,我先用建立了一个417.ys进入后,输入:

然后用make 417.yo编译,编译后用vim进入417.yo

参考资料,我看了闫嘉欣的她总结的比我有条理多了。