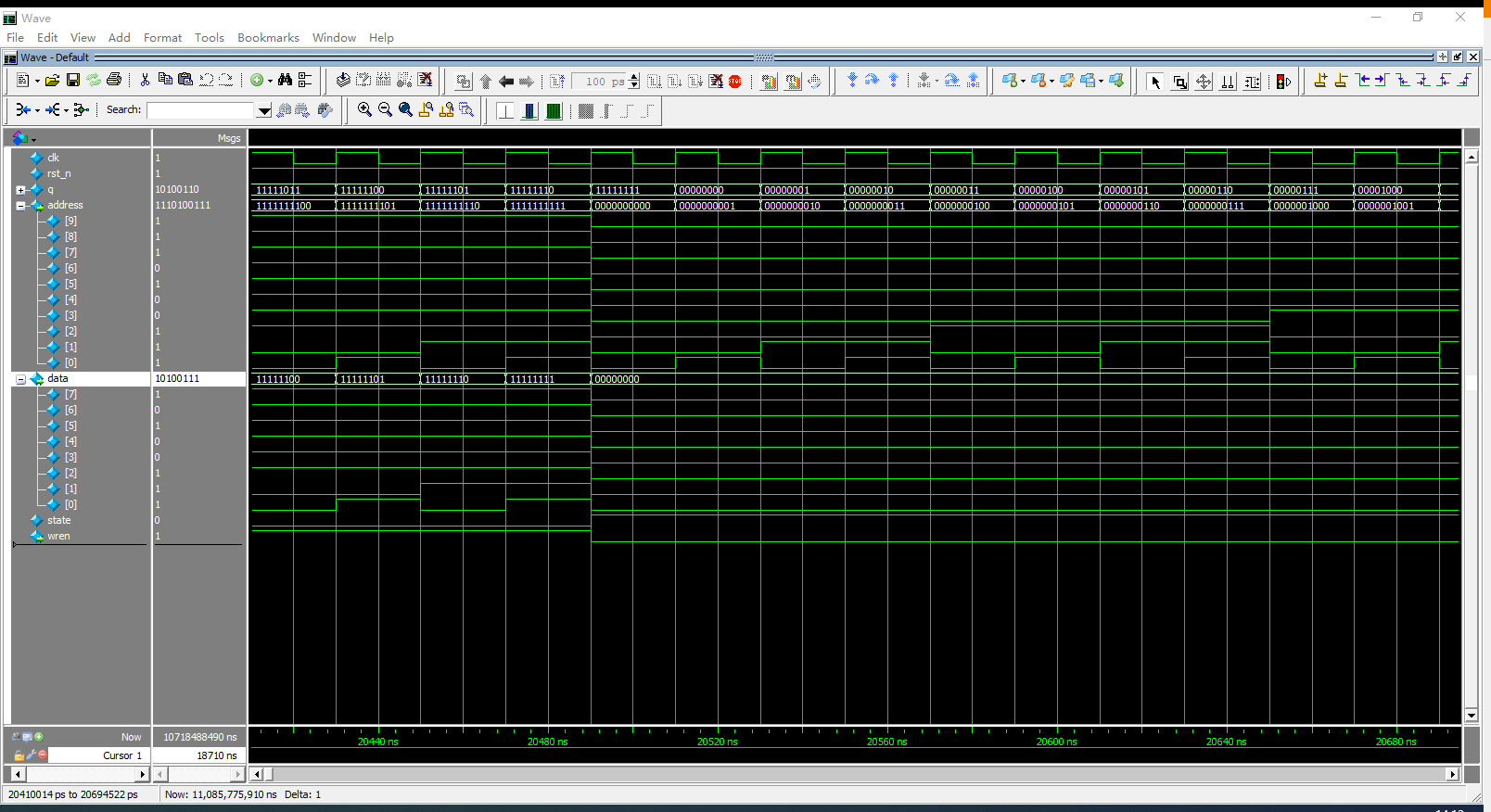

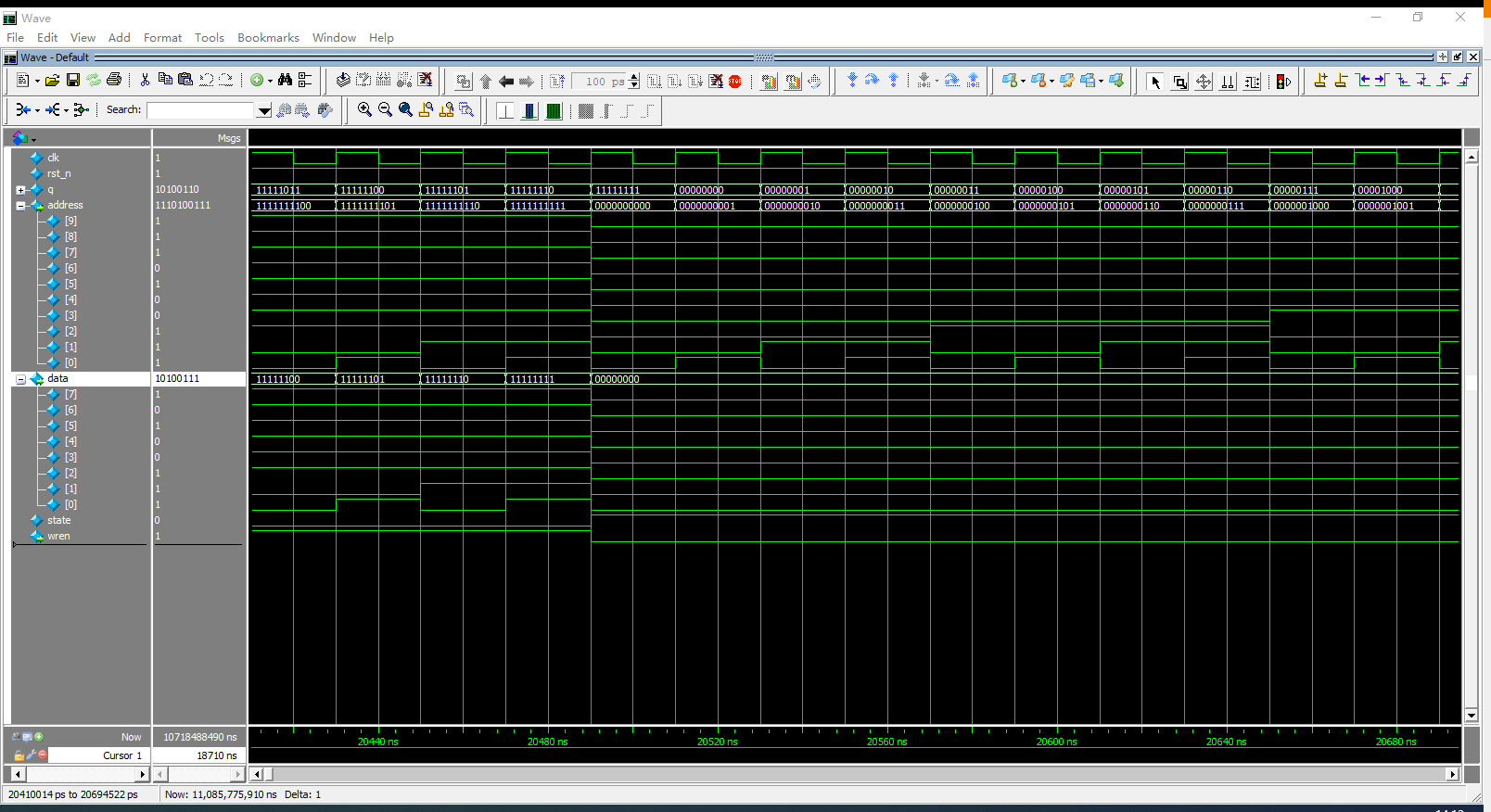

有人问在仿真RAM IP控制的工程代码时发现,wren为1,即写有效时,单口RAM 数据输出端口也有数据,不清楚是什么原因?

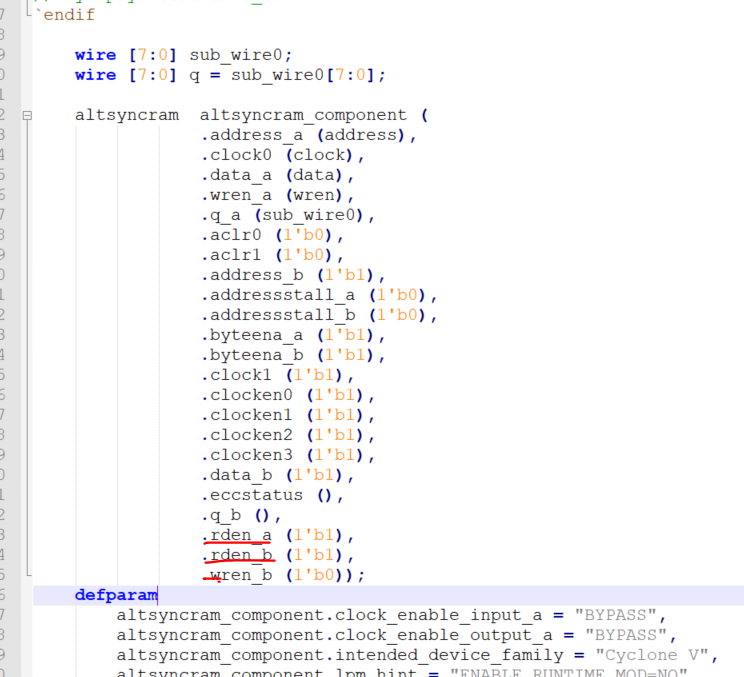

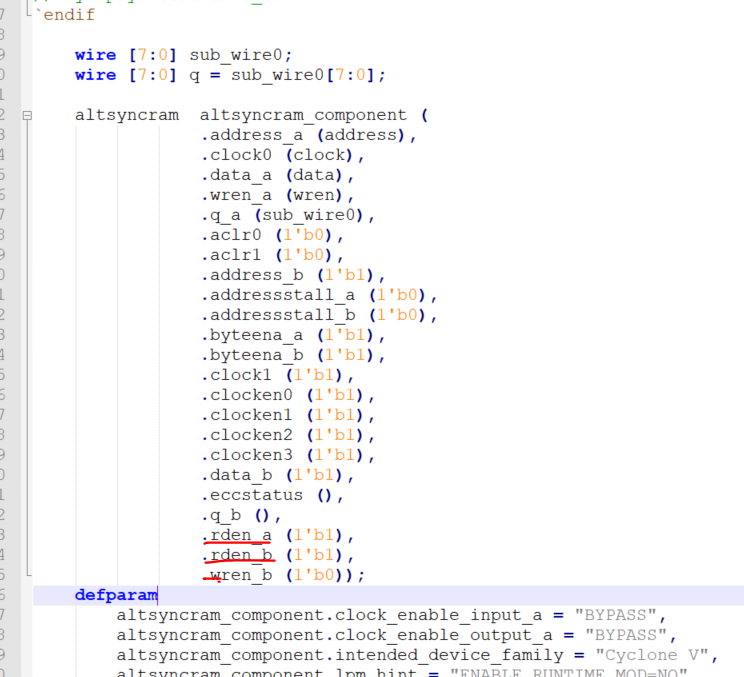

其实打开RAM 的IP自动生成的代码 你就会找到答案, 在代码里面读是能信号默认是1了。所以一直会有数据读出:

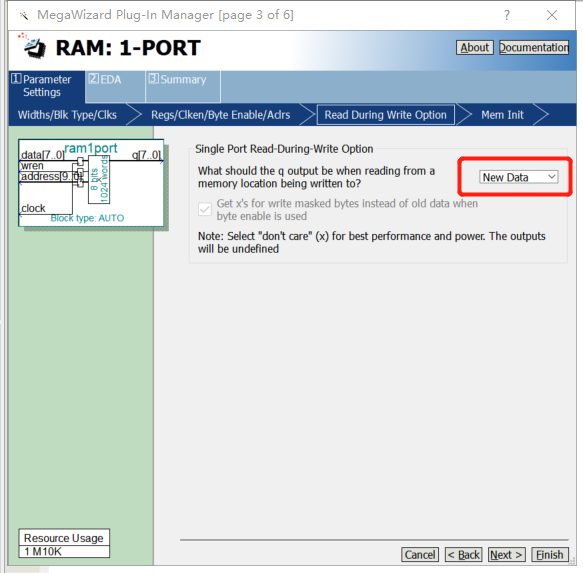

那读出的是当前写入的数据还是之前的旧数据呢?

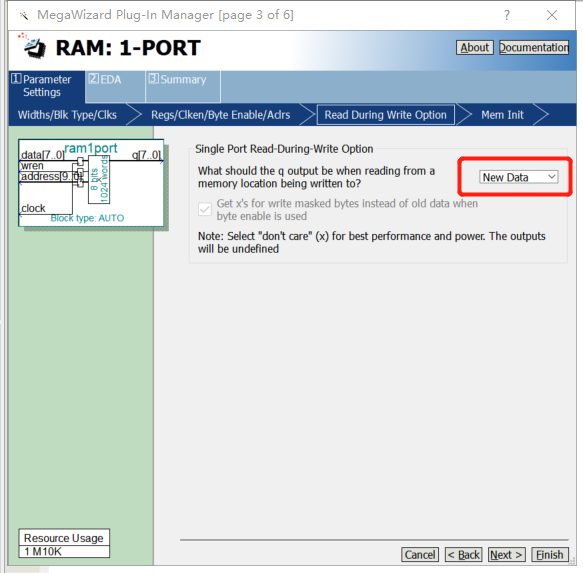

这个要看你IP 当中的设定,当初IP 参数设定有这样一个选项:

有人问在仿真RAM IP控制的工程代码时发现,wren为1,即写有效时,单口RAM 数据输出端口也有数据,不清楚是什么原因?

其实打开RAM 的IP自动生成的代码 你就会找到答案, 在代码里面读是能信号默认是1了。所以一直会有数据读出:

那读出的是当前写入的数据还是之前的旧数据呢?

这个要看你IP 当中的设定,当初IP 参数设定有这样一个选项: