之前我看了一个很简单的Verilog代码,里面用到 initial:

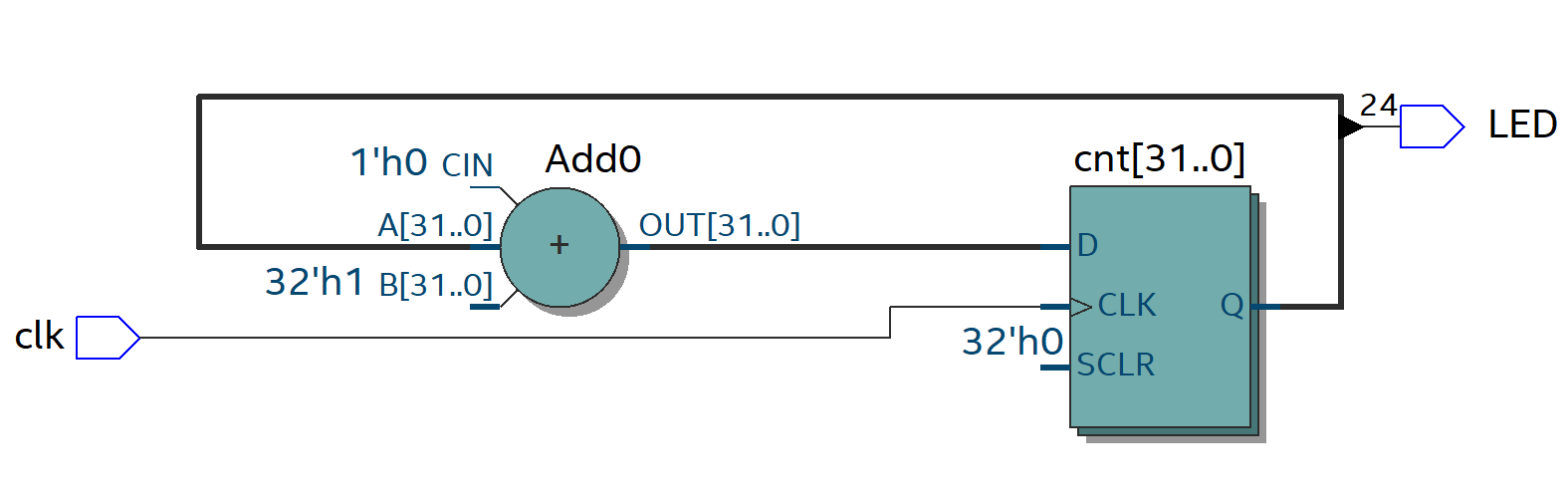

然后综合得到如下电路:

我一直误解为这些不可综合的语句是不能出现在设计里面,只能出现在仿真里面的。我以为如果出现在设计里面了也会被忽略掉 。但是我发现 initial 里面的语句实际中确实起了作用,它初始化了counter,我把代码(sof)下载到FPGA开发板进 确实是从0开始计数的。然后我咨询了公司的研发工程师,他是这样解答的:

。但是我发现 initial 里面的语句实际中确实起了作用,它初始化了counter,我把代码(sof)下载到FPGA开发板进 确实是从0开始计数的。然后我咨询了公司的研发工程师,他是这样解答的:

///////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

当然我在网络上找到了些可综合和不可综合的解释 感觉也很有参考价值:

https://wenda.so.com/q/1378362174074040

综合就是把你写的rtl代码转换成对应的实际电路。

比如你写代码assign a=b&c;

EDA综合工具就会去元件库里拿一个二输入与门出来,然后输入端分别接上b和c,输出端接上a

假如你写了很多这样的语句

assign a=b&c;

assign c=e|f;

assign e=x^y;

……

综合工具就会像搭积木一样的把你这些“逻辑”电路用一些“门”电路来搭起来。当然,工具会对必要的地方做一些优化,比如你写一个电路assing a=b&~b,这样工具就吧a恒接为0了,而不会去给你找一个与门来搭这个电路。

所以,“综合”要做的事情有:编译rtl代码,从库里选择用到的门器件,把这些器件按照“逻辑”搭建成“门”电路。

不可综合,是指找不到对应的“门”器件来实现相应的代码。比如#100之类的延时功能,简单的门器件是无法实现延时100个单元的。还有打印语句等,也是门器件无法实现的,这个应该很好理解。