(一)Verilog HDL语法

一、模块

1、定义:一个电路模块/一种逻辑功能;

2、命名规则:只能是字母,数字,"$",或者’_’,且开头必须是字母或者”_”。区分大小写

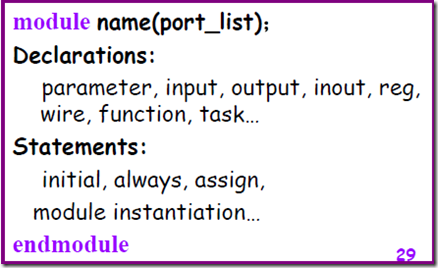

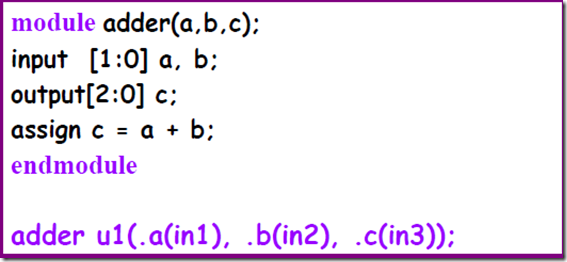

3、Module的定义以及实例化

二、数据类型及常量变量

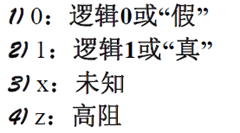

1、Verilog HDL有四种基本的值

(1)其中x和z不区分大小写;

(2)z也可以使用?表示,虽然不懂为什么不是表示未知……

2、Verilog HDL三类常量

(1)整型:

A、缺省十进制:1,-2;

下划线(_)可以用来分隔数的表达式来提高易读性

(2)实数型:

1.235 ,-545.34,3.6e4

(3)字符串型:

“fuck”,一样有转义字符

3、Verilog HDL变量最主要的数据类型:

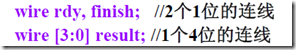

(1)线网类型:

A、 定义:

表示Verilog结构化元件间的物理连线。它的值由驱动元件的值来决定,例如连续赋值或者门的输出。如果没有驱动元件连接到线网,线网的缺省值为z。常用:wire

B、举例:

C、用处:

可用作任何方程式或元件的输入,assign语句或者元件的输出。

(2)寄存器类型:

A、定义:

表示一个抽象的数据储存单元(但不表示它就一定是综合寄存器)。寄存器的缺省值为x。常用:reg

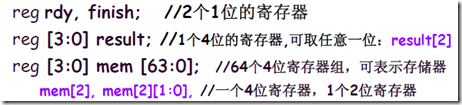

B、举例:

Attention:

(1)在always语句和initial语句中的赋值对象只能是reg类型,reg类型信号也只能在always语句和initial语句中被赋值,

(2)所以,always、initial块外的赋值对象和连线用wire型信号,always、initial块内的赋值对象用reg型

三、运算符与运算表达式

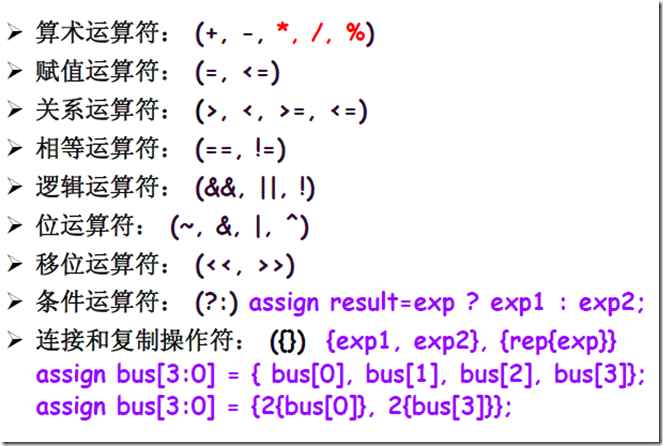

1、运算符

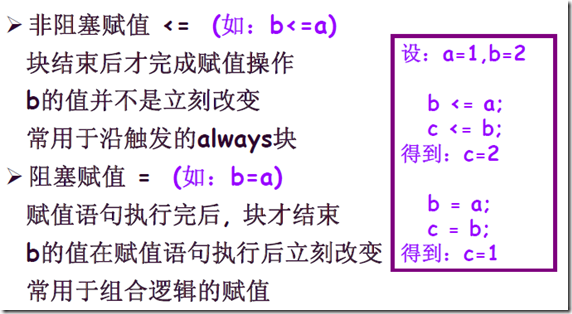

“<=”:非阻塞语句,即这句话执行时,下一句语句也执行。

“==”:阻塞语句

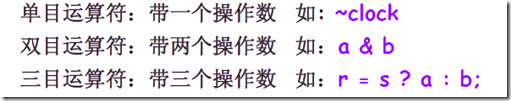

2、表达式=操作数+运算符

(1)分类:

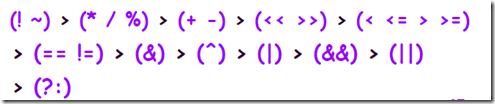

(2)优先级:

四、块语句:

1、定义:

两条或者多条语句的组合,主要有两种。

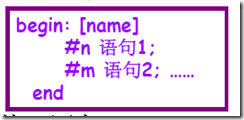

2、begin_end语句:顺序块

(1)块内的语句顺序执行

(2)每条语句的延时为相对前一句

(3)最后一句执行完,才能跳出该块

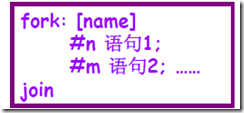

3、fork_join语句:并行块

(1)块内语句同时执行

(2)每条语句的延时为相对于进入块仿真的时间

(较为少用)

五、条件语句与循环语句

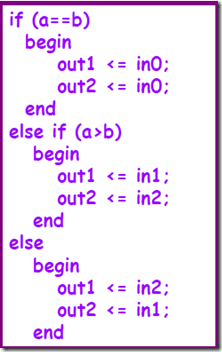

1、if else语句(需要在always块中使用)

if(表达式) 语句;

else if(表达式) 语句;

else 语句; (多个语句需放在begin end间)

2、case语句:多分支语句(需要在always块中使用)

case(表达式) 分支:语句…… default:语句; endcase

3、forever连续执行,常用于产生时钟信号

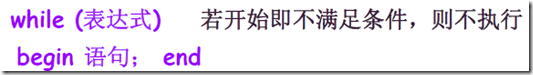

4、while执行语句

5、repeat

连续执行语句n次

repeat(表达式),在此表达式通常为常量表达式,表示重复次数。

begin语句;end

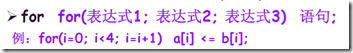

6、for

六、结构说明语句

1、initial

(1)仿真开始时对各变量的初始化

(2)生成激励波形作为电路的测试信号

(3)只执行一次

(4)程序模块中可有多个,并行执行

2、always

(1)格式:

(2)作用:

若触发条件满足,则被执行,满足一次执行一次,可由多个always块,并行执行,在always块中赋值的对象只能是reg语句。

3、function

(1)作用:返回一个用于表达式的值

(2)格式:

(3)规则:

A、不能包含时间控制语句

B、不能启动任务

C、至少有一个输入

D、必须存在给予函数名同名变量赋值语句

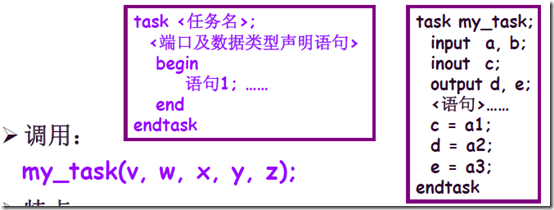

4、task

(1)作用:支持多种目的,可计算多个计算结果。

(2)格式:

(3)特点:

A、可定义自己的仿真时间单位

B、可定义自己的仿真时间单位,可启动其他的task和function。