20145325张梓靖 《信息安全系统设计基础》第6周学习总结

教材学习内容总结

- 8ISA一个处理器支持的指令和指令的字节级编码称为它的指令集体系结构ISA。

虽然每个厂商制造的处理器性能和复杂性不断提高,但是不同型号在ISA级别上都保持着兼容。因此,ISA在编译器编写者和处理器设计人员之间提供了一个概念抽象层。

这个概念抽象层即ISA模型:CPU允许的指令集编码,且顺序地执行指令,也就是先取出一条指令,等到她执行完毕,再开始下一条。然而,现代处理器的实际工作方式可能跟ISA隐含的计算模型大相径庭。通过同时处理多条指令的不同部分,处理器可以获得较高的性能。但其必须对外表现出符合ISA模型的执行结果。

在计算机科学中,用巧妙的方法在提高性能的同时,又保持一个更简单、更抽象模型的功能,这种思想是众所周知的(抽象)。 - CPU硬件简介大多数现代电路设计都是用信号线上的高电压和低电压来表示不同的位值。

要实现一个数字系统需要三个主要的组成部分:

①计算对位进行操作的函数的组合逻辑(ALU)

②存储位的存储器元素(寄存器)

③控制存储器元素更新的时钟信号 - 逻辑门是数字电路的基本计算元素,它们产生的输出,等于它们输入位值的某个布尔函数。

将很多逻辑门组合成一个网,就能构建计算块,称为组合电路。 - 算术/逻辑单元(ALU)是一种很重要的组合电路,这个电路有三个输入:两个数据输入及一个控制输入。根据控制输入的设置,电路会对数据输入执行不同的算术或逻辑操作。

- 存储器和时钟时钟是一个周期性信号,决定了什么时候要把新值加载到设备中。大多数时候,寄存器都保持在稳定状态(用x表示),产生的输出等于它的当前状态。信号沿着寄存器前面的组合逻辑传播,这时,产生了一个新的寄存器输入(用y表示),但只要时钟是低电位的,寄存器的输出就仍然保持不变。当时钟变成高电位的时候,输入信号才加载到寄存器中,成为下一个状态y,直至下一个时钟的上升沿。

寄存器是作为电路不同部分中的组合逻辑之间的屏障。每当每个时钟到达上升沿时,值才会从寄存器的输入传送到输出。 - 指令编码每条指令需要1——6个字节不等,这取决于需要哪些字段。每条指令的第一个字节表明指令的类型:高4位是代码部分(例:6为整数类操作指令),低4位是功能部分(例:1为整数类中的减法指令) 61合起来即为sub指令。

- 处理一条指令的序列取指,译码,执行,访存,写回,更新PC

- SEQ的时序组合逻辑不需要任何时序或控制——只要输入变化了,值就通过逻辑门网络传播。;要控制处理器中活动的时序,只需要寄存器和存储器的时钟控制。

- 流水线流水线化的一个重要特性就是增加了系统的吞吐量,也就是单位时间内服务的顾客总数,不过它也会轻微地增加延迟,也就是服务一个用户所需要的时间。流水线化是允许多条指令在CPU中,每条指令在CPU中的时间是一样的,哪怕一个周期就能执行完了,也得等剩下的阶段结束,使后面的指令被延迟了。

虽然流水线化,所有指令在CPU中待的时间都一样(且都按最耗时指令算的),但它们的时间是重叠的。假设一条指令在CPU中待6ms,那么12ms能处理7条指令,而非流水线,虽然一条指令最多执行6ms,但它们的时间是相加的,12ms可能只执行3条。12=6+2+4)

教材学习中的问题和解决过程

问题 对于Y86指令集中的nop,具体作用到底是什么,只需对PC加1是什么含义,为什么说“标号为'icode'和‘ifun’的控制逻辑块计算指令和功能码,等于从存储器读出的值,或者当指令地址不合法时(由信号imem error指明),这些值对应于nop指令”?

解决过程 nop作用:这是一个占位指令,他不做任何事,后续为了实现流水线,它有一定的作用。

如书中P280~P282的例子,使用nop指令是为了产生延迟,使得接下来正真需要执行的指令在执行之时,就能使用本条指令所要用到的前面指令带来的更新结果,避免造成数据冒险,使得流水线能得到正确的结果。

课后练习题(实验楼)

使用Y86模拟器,在YIS环境下对汇编文件进行汇编的结果

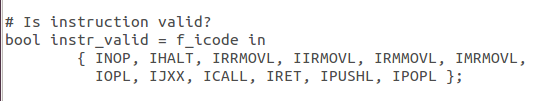

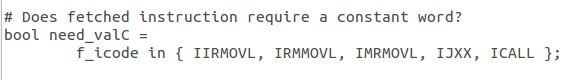

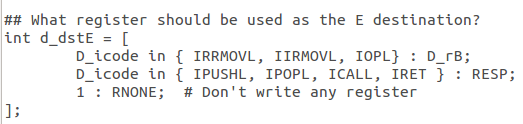

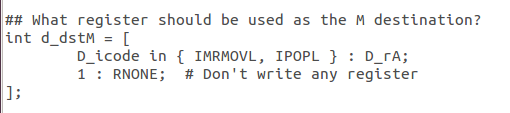

进行验证的HCL代码

本周代码托管

学习进度条

| 代码行数(新增/累积) | 博客量(新增/累积) | 学习时间(新增/累积) | 重要成长 | |

|---|---|---|---|---|

| 目标 | 3500行 | 25篇 | 300小时 | |

| 第一周 | 70/70 | 2/2 | 22/22 | |

| 第二周 | 150/220 | 1/3 | 23/45 | |

| 第三周 | 160/380 | 1/4 | 25/70 | |

| 第五周 | 250/630 | 1/5 | 30/100 | |

| 第六周 | 25/655 | 1/6 | 27/127 |