教材学习内容总结

第四章 处理器体系结构

本章内容是处理器体系结构,重点掌握ISA,并能举一反三;本章带着大家设计并实现了一个结合CISC和RISC思想的处理器Y86,一个类IA32体系的处理器;ISA在编译器编写者和处理器设计者之间提供了一个抽象。

本章重点是4.1-4.3,流水线部分4.4-4.5供学有余力的同学自学

练习题:4.1 4.2 4.5 4.6 4.8 4.10 4.11 4.12 4.16 4.17 4.19 4.21 4.24

-

ISA:一个处理器支持的指令和指令的字节级编码称为它的指令集体系结构ISA.

-

Y86

-

是一个指令体系结构(ISA)寄存器、存储器、条件码、PC、程序状态。书中给出了一个示例程序,来说明X86和Y86的区别,这里就不详细分析这些汇编指令了,这种事情在第三章已经做的很多了,其实两者是非常相似的,毕竟Y86就是根据X86的结构简化而得。区别就在于,有的时候Y86需要两条指令来达到X86一条指令就可以达成的目的。

-

比如对于X86指令中的 addl $4,%ecx 这样的指令,由于Y86当中的addl指令中不包含立即数,所以Y86需要先将立即数存入寄存器,即使用irmovl指令,然后再使用addl来处理加法运算。

-

总的来说,Y86就是一个X86的缩减版,它的目的是以简单的结构实现一个处理器,帮助我们了解处理器的设计和实现。

-

Y86异常

对于Y86来说,程序猿可见的状态中就有stat状态码,它标识了程序执行的状态。Y86需要有能力根据stat去做一些处理。不过为了简单起见,这里除了正常执行之外,都将停止指令的执行。真实当中,会有专门的异常处理程序。

Y86指令

-

Y86指令集基本上是IA32指令集的一个子集,只包括四字节整数操作,寻址方式比较少,操作也较少。

-

halt: 停止指令的执行(IA32中的指令hlt)。IA32中应用程序不允许使用这条指令,因为它会导致整个系统暂停运行。对于Y86而言,执行halt指令会导致处理器停 止,并将状态码设置为HLT。

-

nop:这是一个占位指令,它不做任何事情,后续为了实现流水线,它有一定的作用。

-

xxmovl:这是一系列的数据传送指令,指明源和目的地的格式。第一个字母表明源的类型,第二个字母代表目的。其中r代表寄存器,m代表存储器,i代表立即数。比如rrmovl指令,则代表将一个寄存器的值,赋给另外一个寄存器。

-

opl:操作指令,比如addl,subl,andl,xorl是四个整数操作指令,Y86中只允许对寄存器数据进行操作(IA32中还允许对存储器数据进行操作),这些指令会设置条件码ZF、SF、OF。

-

jxx:条件跳转指令。jmp,jle,jl,je,jne,jge,jg是七个跳转指令,根据分支指令的类型和条件码的设置来选择分支。

-

cmovxx:条件传送指令,后面的xx代表的是条件。特别的是,条件传送只发生在两个寄存器之间,不会将数据传送到存储器。

-

call与ret:方法的调用和返回指令。一个将返回地址入栈,并跳到目标地址。一个将返回地址入PC,并跳到返回地址。

-

push与pop:入栈和出栈操作。

指令编码

-

每条指令需要1-6个字节不等。每条指令的第一个字节表明指令的类型。这个字节分为两个部分,每部分4位:高4位是代码部分,低4位是功能部分。功能值只有在一组相关指令共用一个代码时才有用。

-

8个程序寄存器中每个都有相应0-7的寄存器标示符,Y86与IA32的寄存器编号一致。程序寄存器存在CPU中的一个寄存器文件中,这个寄存器文件就是一个小的、以寄存器ID为地址的随机访问存储器。当需要指明不应访问任何寄存器时,就用ID值0xF来表示。

-

有的指令需要一个附加的4字节常数字作为立即数数据或地址指示符偏移量或分支指令和调用指令的目的地址。所有整数采用小端法编码。

Y86异常

-

1.程序员可见的状态包括状态码Stat,它描述程序执行的总体状态。

-

2.Y86中,任何AOK以外的代码都会使处理器停止执行指令,而没有异常处理程序。

逻辑设计

这部分与以前学习过的电子电路,数字电路,HDL关联性非常大。

-

逻辑1是用高电压表示的,逻辑0使用低电压表示的。

-

逻辑门:只对单个位的数进行操作,而不是整个字。与:&& 或: || 非: !

-

组合电路:

很多逻辑门组合成一个网构建的计算块。(注意两个或多个输出不能连接在一起,并且无环。) -

HCL表达式与C语言中的表达式的区别:

HCL中输出会持续随着输入变化而变化。而C语言中只有在程序执行到的时候才进行求值。 HCL只对0和1操作。C语言中,0是FLASE,除了0以外的所有整数都是TRUE C中&&和||这两种,是优先求值,(&和|并不是)第一个值就能确定结果的话,它不会去计算第二个值。但是HCL中并没有这样的规则。 -

存储器和时钟

-

时钟寄存器:(硬件寄存器)存储单个位或字。时钟信号控制寄存器加载输入值。

-

随机访问存储器(存储器)存储字,用地址来选择该读或该写那个字。

-

-

SEQ硬件结构:

-

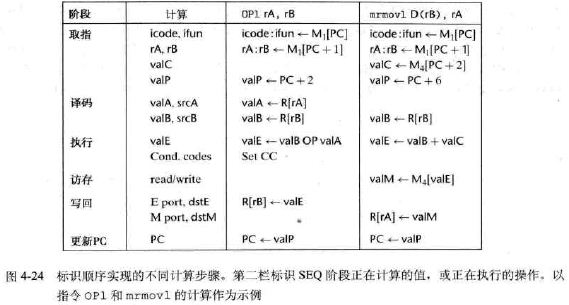

计算中不一样的地方:

-

四个寄存器的ID信号:srcA,valA的源;srcB,valB的源;dstE,写入valE的寄存器;dstM,写入valM的寄存器。

-

-

SEQ的时序:

-

需要时序控制的控制的四个硬件:程序计数器、条件码寄存器、数据寄存器、寄存器文件。

-

它们的值要等时钟信号(上升沿或者下降沿)来临时才改变。

-

-

SEQ阶段的实现

-

取指阶段

-

译码和写回阶段

-

执行阶段:执行阶段包括算术/逻辑单元(ALU)第一步每条指令的ALU计算,执行阶段还包括条件码寄存器

-

访存阶段:访存阶段的任务是读或者写程序数据,两个控制块产生存储器地址和存储器输入数据的值,另外两个块产生控制信号表明应该执行读操作还是写操作。

-

更新PC阶段:SEQ中最后一个阶段会产生程序计数器的新值,依据指令的类型和是否要选择分支,新的PC可能是valC、valM、valP

-

实验楼实验代码调试过程

-

构建YIS环境

新建了一个20145320的文件夹

输入指令wget http://labfile.oss.aliyuncs.com/courses/413/sim.tar

显示保存后输入指令tar -xvf sim.tar

后进入 sim 文件夹,输入指令sudo apt-get install tk

解析完成后输入指令sudo ln -s /usr/lib/x86_64-linux-gnu/libtk8.6.so /usr/lib/libtk.so并输入make指令

- YIS测试

-

cd y86-code进入测试代码,并对代码为asuml.ys进行汇编结果为asuml.yo

-

make all可以汇编运行所有代码结果。

-

- 查看asuml.yo

- 和课本上一样