Arria V GX开发套件:

The Arria V GX FPGA Starter Kit features a 5AGXB3 Engineering Sample (ES) device and a 1-year license for the Quartus® II design software.

http://www.altera.com/products/devkits/altera/kit-arria-v-starter.html

Arria V GX FPGA开发套件 (DK-5AGXB3N/ES)

http://www.altera.com.cn/products/devkits/altera/kit-arria-v-gx.html

问题:我安装好QuartusII 13.0,现在如何加载qdz文件

回答:tool 菜单里面最后一个选项install device

器件:5AGXFB3H6F35C6N器件

对于新做出来的ArriaV板子,出现如下问题:

1、LVDS发送模块信号不好的原因是因为阻抗匹配100殴的问题,当把输出差分对引脚约束到2(有0,1,2可选)时,可以解决这个问题,且可以观察到LVDS的摆幅升上去了,跟Dolby板子测出来的结果差不多,信号也很好。这是硬件同事调试好久才解决的,我发现自己有太多东西要学习了,自己的声威精神还不够。

2、由此可知,LVDS的接收和发送模块都需要约束,当初接收信号不好,噪声干扰严重,也是同事看英文原版文档才发现的,也是需要对输入的差分对引脚进行差分约束才可以。此外,要特别注意LVDS输入终端的差分时钟需要进行经过clk_buf进行缓冲,否则输出的视频会失真。

3、当涉及的约束太多雷同时,我们可以采用通配符*的写法,简单明了。例如:

set_instance_assignment -name PROGRAMMABLE_VOD 2 -to LVDS_TX*

set_instance_assignment -name PROGRAMMABLE_VOD 2 -to LVDS_CLKOUT*

set_instance_assignment -name INPUT_TERMINTION DIFFERENTIAL -to LVDS_RX*

set_instance_assignment -name INPUT_TERMINTION DIFFERENTIAL -to LVDS_CLKIN*

之前在ISE工具上使用过的芯片有Spartan6 XC6SLX150T-3FGG900和Spartan3A XC3S400A-5FG320

2013年1月10日 11:14:22

接下来的任务是研究Altera提供的开发套件--ArriaV GX Starter Kit

Arria V GX FPGA Development Kit

1、将开发板USB下载插入笔记本上,首先需要安装驱动,这边需要选择的驱动是usb-blaster-ii(不知道它与usb-blaster的区别是什么)

来源:小時不識月 Stupid & Hungry:http://www.cnblogs.com/yuphone/archive/2010/08/18/1802131.html

经过这个启示,我建议大家尽量安装与所用软件版本匹配的驱动。一般情况下,与当前版本匹配的USB-Blaster或Byte II Blaster的驱动在\Altera\版本号\quartus\drivers\usb-blaster文件夹内。

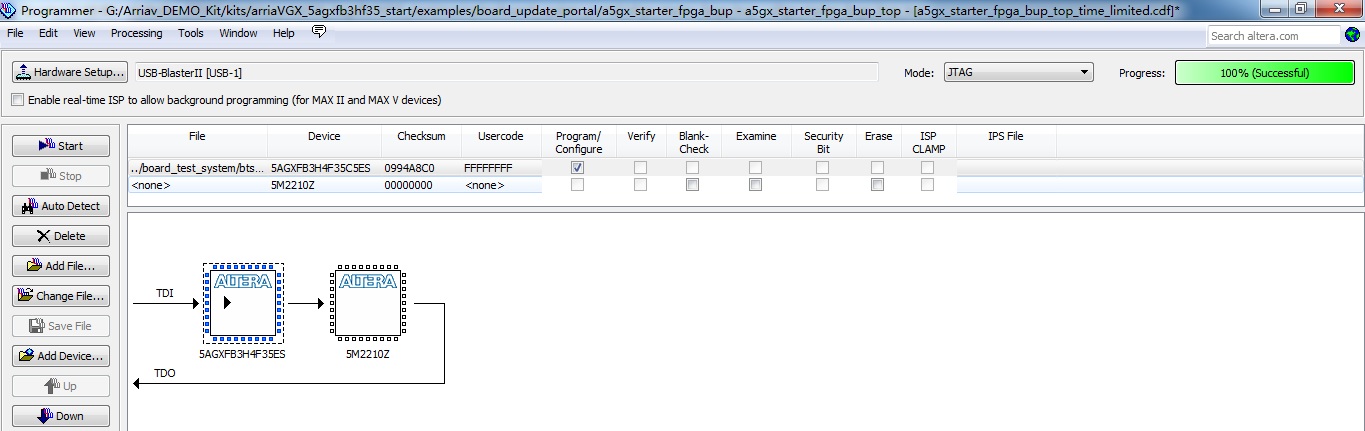

问题:usb-blaster-ii与usb-blaster的区别,我认为是下载界面有两个可编程逻辑器件(ArriaV FPGA和MAX V CPLD)如图1所示,因此USB-BlasterII可以识别到两个器件,如图2所示。

图1 FPGA的下载界面 (如果只有ArriaV,而没有MAX V,没无法下载程序到板子上。)

图2 USB-BlasterII识别到的两个器件

2、在Altera官方网上下载开发板的相关资料

All Development Kits:http://www.altera.com/products/devkits/kit-dev_platforms.jsp

我所用的开发板是Arria V Starter Kit http://www.altera.com/products/devkits/altera/kit-arria-v-starter.html

Figure 1: Arria V GX Starter Board with a 5AGXB3ES FPGA Device

XCVR:收发机装置(Transceiver Unit) ,Transceiver I/Os的速率可以高达6.5536Gbps

PB:push button

SDI:串行数字接口(Serial Digital Interface) 嵌入75欧的3G SDI transceivers

SSRAM:同步静态随机存储器(Synchronous Static Random Access Memory)

BTS:Board Test System 板测试系统

HSMC:high-speed mezzanine card (HSMC) connectors 高速夹层卡连接器

PCI:abbr. 外部控制器接口Peripheral Component Interconnect

Gigabit Ethernet 千兆比特 以太网

HDMI TX:嵌入TMDS电平移位器,速率高达2.7Gbps

- System controller: MAX® V 5M2210ZF256CN CPLD器件

- Power monitor GUI

- Single analog-to-digital converter (ADC), eight channels

- Non-isolated power rail

- Fast passive parallel (FPP) x16 mode through parallel flash loader (PFL)

- Control and status registers Port

MAX V系列的关键应用包括:来源:http://www.ednchina.com/ART_87759_18_20011_NP_9078a37a.HTM?jumpto=view_welcomead_1357807447539

· I/O扩展——进行I/O解码,以低成本有效的增强了其他标准器件的I/O功能。

· 接口桥接——以尽可能低的成本转换不兼容器件之间的总线协议和电压。

· 功耗管理——管理电路板上其他器件的上电排序,并进行监控。

· 配置和初始化——控制电路板上其他器件的配置和初始化。

模拟控制——通过脉冲调制器(PWM)实现模拟标准器件(灯光、声音或者运动)的数字控制,不需要数模转换器(DAC)。

3、PDF文档:Arria V GX Starter Kit User Guide

第5章Board Update Portal 板更新门户 (其相关更新信息可以在Altera官方网站上查找)

(1)首先验证上电后板上程序实现的功能是先是LCD第一行显示:Not Connected,当插上网线后,LCD第一行显示:Board Update Prt1,第二行显示: Connecting...。接着第一行显示网线的IP地址:172.16.145.108。在电脑的浏览器上输入这个网址可以打开Board Update Portal网页。

4、研究开发板上CPLD芯片MAX II EPM570F100C5N的作用,直接查找它的应用,有点多且杂。因此,想到它在本开发板的主要作用是下载,那Altera器件有几种下载方式呢?从这方面入手,感觉比较有用。

来源:http://yhua001.blog.163.com/blog/static/82365290201021635321421/

Usb EZBlaster下载电缆性能简介:http://kugel.spaces.eepw.com.cn/articles/article/item/25822

谈谈Altera FPGA的配置:http://lqing61857.blog.163.com/blog/static/77107610200910143130431/

不管Xilinx还是Altera,FPGA的配置模式或者方法多样,尤其是Altera器件,什么AS模式、PS模式、FPP模式、AP模式等等。一般逻辑设计者可能不会关心到硬件的设计,但是FPGA的硬件设计者对于FPGA的配置设计是一个基本要求,当然一般不可能要求每个FPGA硬件设计者对每一种配置模式都很熟悉,但是由于每个人的设计习惯、方法以及使用的器件不同从而在产品研发中设计FPGA的加载模式也不一样。

一般有五种下载模式(AS、PS和JTAG、AP)

a、JTAG下载模式:Cyclone、Cyclone II、Stratix II、Flex10K、Acex1K、Max7000和Max3000。我们可以通过JTAG口给EPCS啥写程序。

b、主动串行(AS)模式:EPCS1 和EPCS4、EPCS16。AS模式中配置芯片可以通过Jtag口将JIC文件直接烧入。

c、被动串行(PS)模式:Stratix 和Stratix GX测试时采用。d、 主动并行(AP)模式:AP模式只有CycloneIII器件支持。硬件设计连接可以参考CIII的handbook以及Configuration handbook。e、快速被动并行(FPP)模式。

最新的Altera的选项手册上在介绍配置方式的时候仅介绍了AS(串行)和基于MAXII的并行方式(加PFL)。说到PFL就是MAXII+Flash+FPGA的一种配置方法,其模式是PS或者FPP。这里有Altera的一个AN手册可以看看:Using the Parallel Flash Loader with the Quartus II Software

Program Common Flash Interface(CFI) Flash、NAND flash memory、quad Serial Peripheral Interface (SPI) flash

PFL:parallel flash loader

串行高级技术附件(Serial Advanced Technology Attachment (SATA))( 高达3.0 Gbps)

来源:小时不识月http://www.cnblogs.com/yuphone/archive/2010/05/09/1730889.html

http://www.cnblogs.com/cute/archive/2011/04/29/2032878.html

flash按照内部访问接口不同,分为两种:nor flash和nand flash。

nor flash:像访问SDRAM一样,按照数据/地址总线直接访问;Nor Flash根据外部接口可分为普通的接口即CFI接口和SPI接口。CFI接口,相对于串口的SPI来说,也被称为parallel接口,并行接口。

nand flash:只有8位/16位/32位甚至更多位宽的总线,每次访问,都要将长地址分为几部分,一点点的分布传入才能访问nand flash。Nand和Nor的使用寿命,块擦除的速度,数据存储的出错几率等,都有很大区别。http://blog.csdn.net/chow288/article/details/6324902

来源:Altera Cyclone IV系列FPGA解决方案详解 http://rf.eefocus.com/article/12-04/2075521334058014.html?sort=1111_0_0_0

对Cyclone IV器件进行详细的说明。

8-bit 或者10-bit 位物理介质附加子层(PMA) 到物理编码子层(PCS) 接口

*.qip文件是QuartusII IP File Definition