| 时间 | 作者 | 版本 | 备注 |

|---|---|---|---|

| 2018-10-09 08:38 | beautifulzzzz | v1.0 | 到3 |

| 2018-10-18 07:23 | beautifulzzzz | v2.0 | risc-v (4) |

1、简介

xlinx官网地址: https://china.xilinx.com/products/boards-and-kits/arty.html

1.1 产品描述

售价 99 美元的 Arty 评估套件可为各种嵌入式应用实现快捷跨越式启步,其中包括从基于 Linux 的计算密集型系统到轻量级微控制器等各种应用。 针对 Xilinx 业界最佳低端产品性能功耗比 **Artix®-7 35T FPGA **精心设计Arty 套件具有 Xilinx 可针对几乎任何处理器使用案例进行定制的 MicroBlaze™ 处理器。

1.2 主要性能和优势

- Artix-7 XC7A35T-L1CSG324I FPGA

- 片上模数转换器 (XADC)。

- JTAG 与 Quad-SPI Flash 可编程

- 256 MB DDR3L 支持速率为 667 MHz 的 16 位总线

- 16 MB Quad-SPI Flash

- 10/100 Mb/s Ethernet

- USB-UART Bridge

- 开关、按钮、RGB LED

- 4 个 Pmod 接口 (32 I/O)

- Arduino/ChipKit“盾”接插件 (49 I/O)

1.3 特色 Xilinx 器件

| 项目 | 个数 |

|---|---|

| 逻辑单元 | 33,280 |

| DSP Slice | 90 |

| 存储器 | 1,800 |

| GTP 6.6Gb/s 收发器 | 4 |

| I/O 引脚 | 250 |

注: 包含 Artix-7 XC7A35T-L1CSG324I FPGA

1.4 电路板特性

下图是整个开发板上资源的概览,更详细的可以参考:

注: 板子自带JTAG,用于烧写FPGA固件的,DEBUG得用外置工具

1.5 视频资源

-

介绍用开发IDE如何连接到开发板、烧写程序、及一些简单的介绍

打开vivado,将开发板用一根数据线连接到电脑上,点击设备管理找到对应的设备;在工程页面,双击XADC可以出来一个温度曲线(这个视频花很大篇幅讲了XADC);右键点击xc7a35t,选择program device可以烧写程序; -

使用 Arty Eval Kit 在 Artix-7 A35T 器件上评估 AMSXADC

了解如何快速简单地在 Artix-7 A35T Arty 评估套件上不用任何 HDL而使用简单有效的 IPI 内置设计来评估 Xilinx 模拟混合信号 (AMS) 技术。 视频还展示了一些 TCL 脚本,通过 Vivado 轻松与 XADC 交互并后置处理数据。

-

MicroBlaze WebServer Demo for the ARTY Evaluation Kit

展示了用freeRTOS工程的网络接口,做一个webserver

2、深入

START地址: https://reference.digilentinc.com/reference/programmable-logic/arty/start

2.1 两种开发方法HDL/SOC

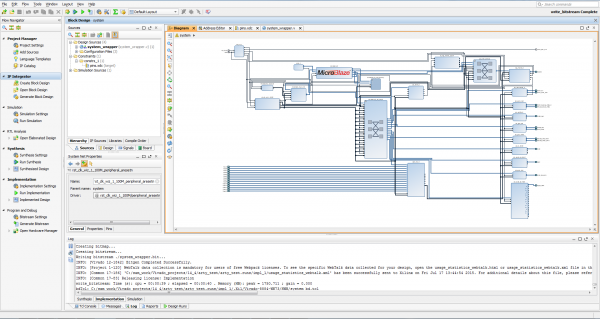

FPGA让Arty变得非常灵活。在众多的特点中,FPGAs有能力转换成定制的软件定义的片上系统(SoC)。这些“软SOC”FPGA配置使用图形化的工具ViVADO IP积分器(Vivado IPI)来设计。在这个工具中,从广泛的库中拖动预构建的外围块,并根据需要放入处理系统。这些预构建的外围设备包括定时器、UART/SPI/IIC控制器以及通常在SoC或微控制器中找到的许多其他设备。厉害的用户还会发现,他们可以用硬件定义语言(HDL),特别是Verilog或VHDL,来创建自己的外围块。对于那些对学习HDL不感兴趣的人来说,Xilinx高级合成工具可以通过用C编写自定义外围块来定义它们。

ARTY的软SOC配置由MyBLAZE处理器核心提供。MixBRAZE是32位RISC软处理器内核,专门设计用于Xilinx FPGA。Arty SoC配置中的MicroBlaze处理器通常以100MHz运行,不过可以设计您的SoC,使其能够在200MHz上运行。Arty通过提供16MB的非易失性程序内存和256MB的DDR3L RAM,支持具有要求高的内存需求的大型MicroBlaze程序。

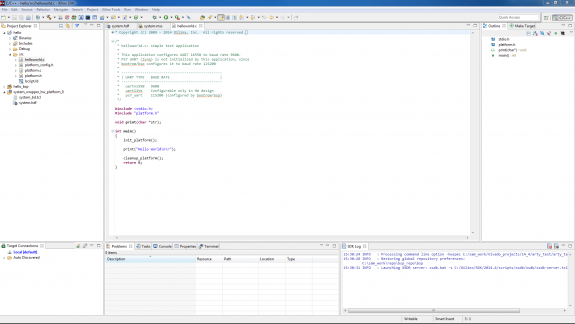

在设计好SOC配置之后,Xilinx也提供了工具用于在软核上应用程序开发。这是通过将您的SoC设计导出到Vivado IPI中并导入到Xilinx软件开发包(XSDK)中来完成的,它是一个用于设计/调试C中的MicroBlaze程序的集成开发环境(IDE)。在IPI到XSDK切换之后,XSDK被自动配置为包括用于SoC中包括的外围块的库和示例。此时,编程Arty非常类似于编程其他SoC或微控制器平台:程序用C编写,通过USB编程到板上,然后可选地在硬件中调试。软SoC配置和MicroBlaze程序也可以加载到16MB非易失性程序存储器中,以便在Arty上电后立即执行。

尽管Arty特别适合Microblaze软SoC设计,它也可以像其他FPGA开发一样在门电路级别编程。此设计流程要求您在Vivado中使用HDL描述RTL电路,并且它不使用Vivado IPI或XSDK工具。这种设计有许多优点,但与编程单板计算机非常不同,而是由熟悉FPGA设计或对设计和实现不包含处理器的数字电路感兴趣的人使用。

2.2 电路板电源供应系统

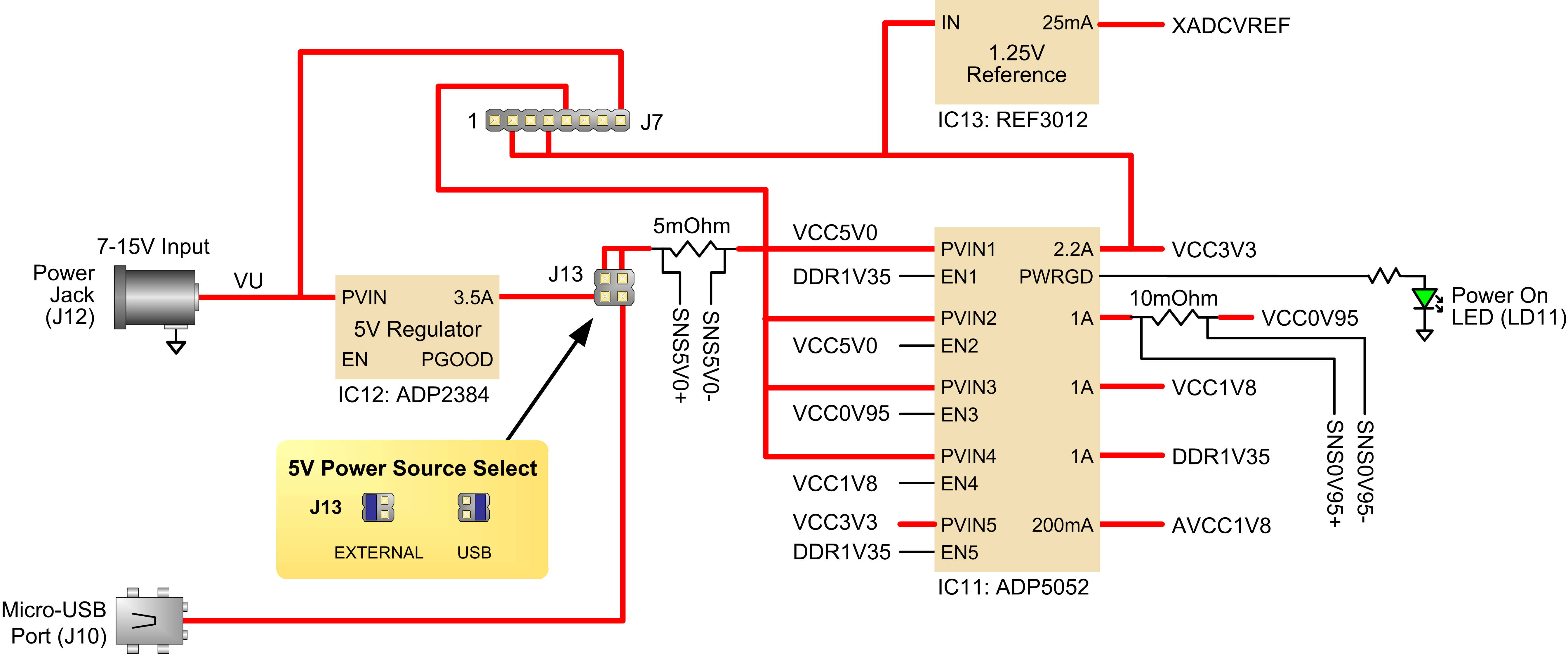

复杂电路一般都有多个芯片负构成整体电源系统,Arty板子也同样具备该系统:输入包括7~15V的DC接口和Micro-USB接口;其中DC接口后还接了一个ADP2384芯片,用于将输入电压降到5V;5V电压经过ADP5052芯片分压成多种电压,供后级系统使用;特别的ERF3012芯片用于将ADP5052电压稳定到1.25V,用于XADC的VREF:

下表是电源系统各路的去向:

| Supply | Circuits | Device | Current (max/typical) |

|---|---|---|---|

| 5V | Onboard Regulators, RGB LEDs | IC12: Analog Devices ADP2384 | 3.5A/0.375A to 2A |

| 3.3V | FPGA I/O, Clocks, Flash, PMODs, LEDs, Buttons, Switches, USB port, Ethernet | IC11: Analog Devices ADP5052 | 2.2A/NA |

| 0.95V | FPGA Core and Block RAM | IC11: Analog Devices ADP5052 | 1.0A/0.2A to 0.8A |

| 1.8V | FPGA Auxiliary | IC11: Analog Devices ADP5052 | 1.0A/NA |

| 1.35V | DDR3L and associated FPGA bank | IC11: Analog Devices ADP5052 | 1.0A/NA |

| 1.25V | XADC Analog Reference | IC13: Texas Instruments REF3012 | 25mA/NA |

3、DEMO

3.1 闪灯DEMO

Getting Started with Vivado : https://reference.digilentinc.com/vivado/getting_started/start

-

sudo 打开工程:

source /opt/Xilinx/Vivado/2018.2/settings64.sh

sudo /opt/Xilinx/Vivado/2018.2/bin/vivado

- 创建新工程,命令为blink:

注: 视频中创建blink文件的时候,clk and led 输入输出属性弄错了,真正的是:clk是output, led是input

其中包含两个重要文件,第一个是板子文件,另一个是自己创建的verilog文件。对于板子文件要和自己的开发板相匹配,此外,对于本工程需要修改下板子文件(增加clk和led):

## Clock signal

#set_property -dict { PACKAGE_PIN E3 IOSTANDARD LVCMOS33 } [get_ports { CLK100MHZ }]; #IO_L12P_T1_MRCC_35 Sch=gclk[100]

#create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports { CLK100MHZ }];

set_property -dict { PACKAGE_PIN E3 IOSTANDARD LVCMOS33 } [get_ports { clk }]; #IO_L12P_T1_MRCC_35 Sch=gclk[100]

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports { clk }];

...

## LEDs

set_property -dict { PACKAGE_PIN H5 IOSTANDARD LVCMOS33 } [get_ports { led }]; #IO_L24N_T3_35 Sch=led[4

#set_property -dict { PACKAGE_PIN H5 IOSTANDARD LVCMOS33 } [get_ports { led[0] }]; #IO_L24N_T3_35 Sch=led[4]

#set_property -dict { PACKAGE_PIN J5 IOSTANDARD LVCMOS33 } [get_ports { led[1] }]; #IO_25_35 Sch=led[5]

自己创建的.v文件为:

module blink(

input clk,

output led

);

reg [24:0] count = 0;

assign led = count[24];

always @ (posedge(clk)) count <= count + 1;

endmodule

这样blink工程实现的功能便是:周期性的控制开发板上的LED0闪烁

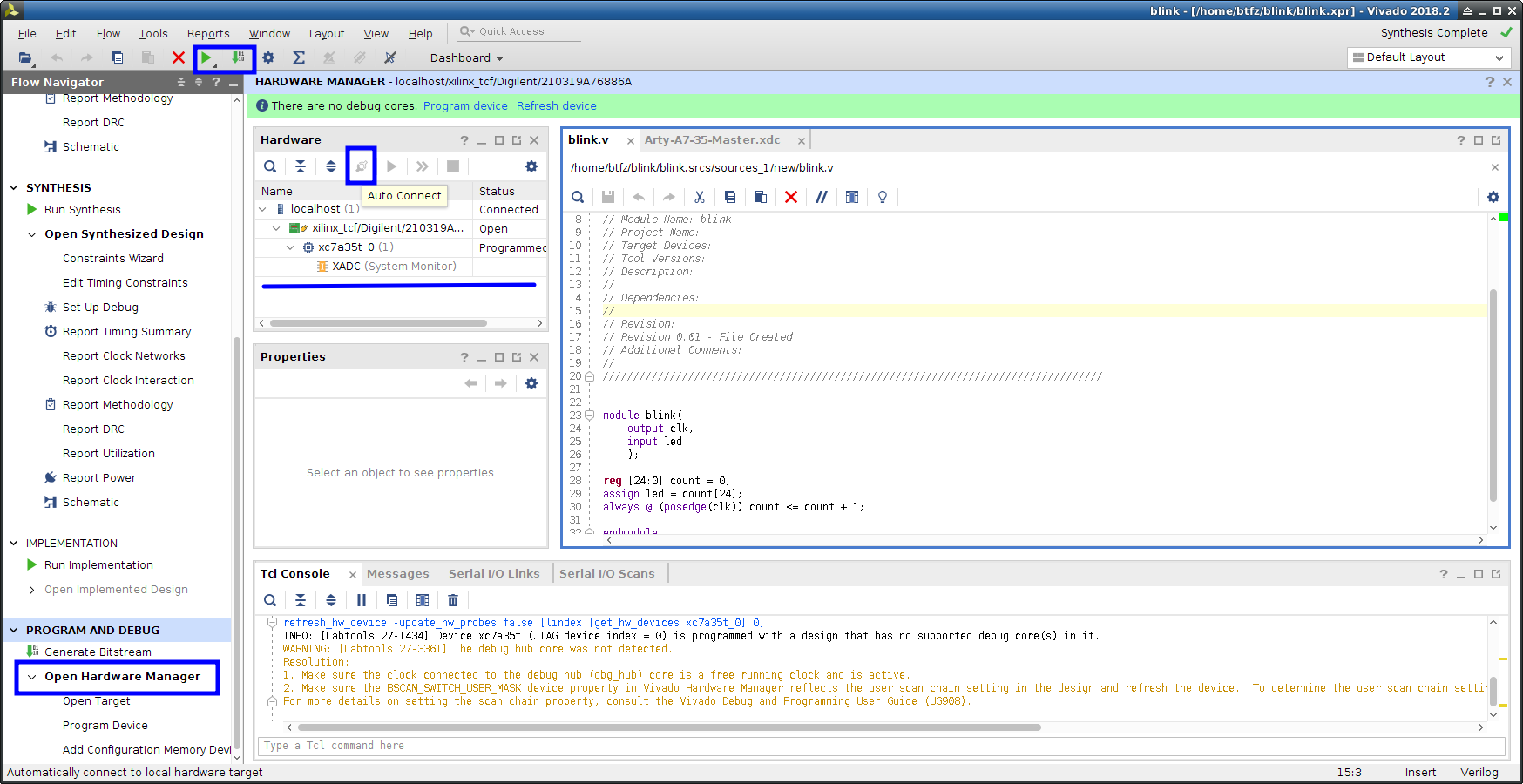

- 编译烧写:

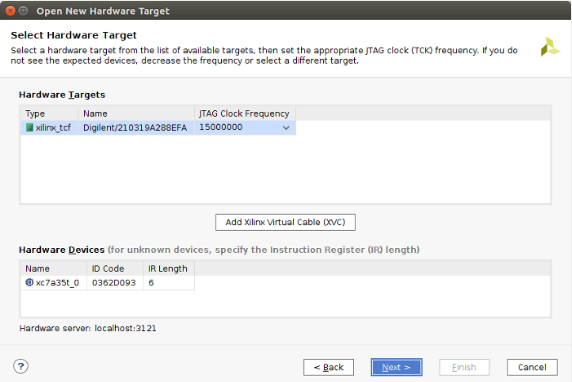

接下来便是编译+烧写,编译需要先点击三角形(RUN)进行编译,然后再点击三角形右边的(create bitstream)产生*.bit文件,如果没有错误在messages中不会有错误提醒。接着左下角的PROGRAM AND DEBUG栏目中选择Open Hardware Manager进行连接开发板(连接时选择auto连接,如果找不到开发板,则说明其他哪里有问题):

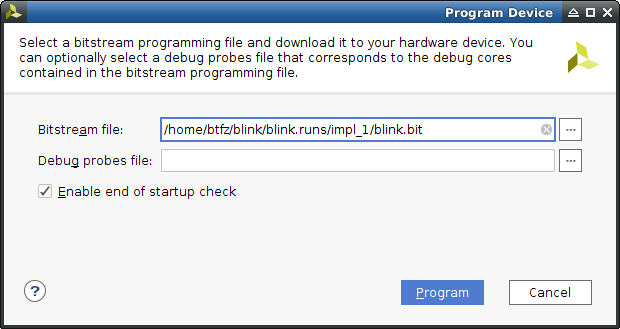

烧写的时候点击左下角PROGRAM AND DEBUG区域中的program device便可:

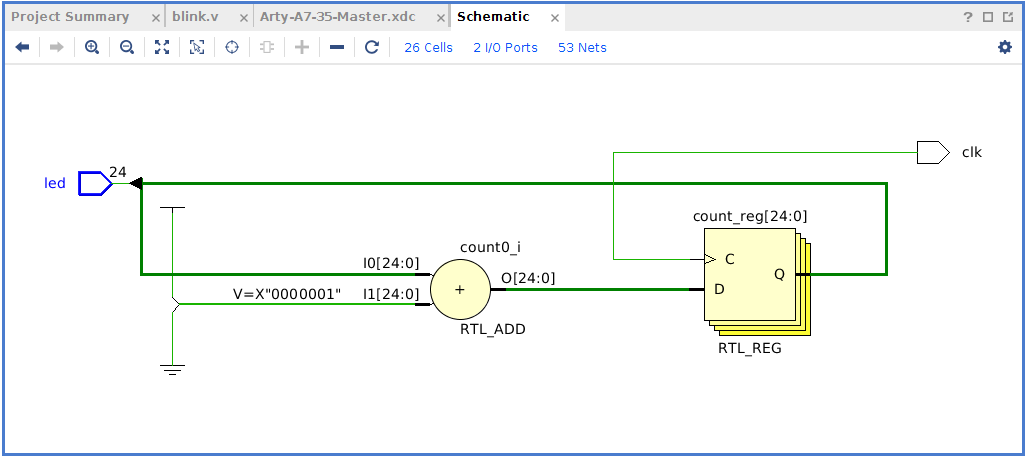

此时点击Flow Navigator中的RTL ANALYSIS的Schematic会产生我们编写代码对应的原理图:

注: 更详细的烧写方法见LINK-6,bit烧写掉电会没有,bin烧写会掉电保持

4、SiFive基于risc-v指令集的芯片验证

4.1 准备工作

- Xilinx Artix-7 35T Arty FPGA Evaluation Kit开发板

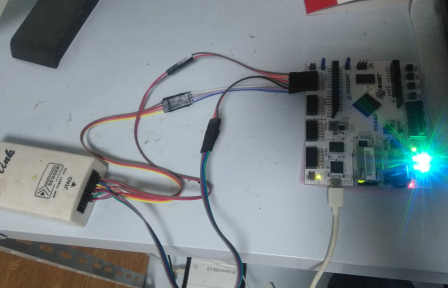

- ARM-USB-TINY-H(这里我选用JLink当作Jtag用,省了点钱)

- FPGA toolchain(下载WEB版开发工具:https://www.xilinx.com/support/download.html)

sudo chmod +x Xilinx_Vivado_SDK_Web_2018.2_0614_1954_Lin64.bin

sudo ./Xilinx_Vivado_SDK_Web_2018.2_0614_1954_Lin64.bin

下载合适的驱动:

cd /opt/Xilinx/Vivado/2018.2/data/xicom/cable_drivers/lin64/install_script/install_drivers/

sudo ./install_drivers

获取Diailent板级支持文件,拷贝到Vivado下:

git clone https://github.com/Digilent/vivado-boards.git

sudo cp -r vivado-boards/new/board_files/* /opt/Xilinx/Vivado/2018.2/data/boards/board_files/

返回到HOME目录,启动环境变量(每次新打开一个termianl去启动VIVADO的时候,都需要执行):

source /opt/Xilinx/Vivado/2018.2/settings64.sh

sudo /opt/Xilinx/Vivado/2018.2/bin/vivado

- 通过vivado UI界面给板子配置(烧写pre-build FPGA二进制程序)

预编译好的二进制FPGA文件Freedom E310 Arty FPGA Dev Kit Bitstream可以从https://dev.sifive.com/dashboard/下载(需要注册)

打开vivado -> Hardware Manager -> 选择板子( Micron part n25q128-3.3v,也可以根据板子来筛选)-> add configuration memory device

烧写完毕后,点击PROG按键,demo程序将会执行,LED1、LED2会点亮,用上位机打开串口会发现LOG输出:

sudo minicom -D /dev/ttyUSB0

Welcome to minicom 2.7.1

OPTIONS: I18n

Compiled on Aug 13 2017, 15:25:34.

Port /dev/ttyUSB0, 23:03:08

Press CTRL-A Z for help on special keys

core freq at 65000000 Hz

SIFIVE, INC.

5555555555555555555555555

5555 5555

5555 5555

5555 5555

5555 5555555555555555555555

5555 555555555555555555555555

5555 5555

5555 5555

5555 5555

5555555555555555555555555555 55555

55555 555555555 55555

55555 55555 55555

55555 5 55555

55555 55555

55555 55555

55555 55555

55555 55555

55555 55555

555555555

55555

5

SiFive E-Series Software Development Kit 'demo_gpio' program.

Every 2 second, the Timer Interrupt will invert the LEDs.

(Arty Dev Kit Only): Press Buttons 0, 1, 2 to Set the LEDs.

Pin 19 (HiFive1) or A5 (Arty Dev Kit) is being bit-banged

for GPIO speed demonstration.

BT0~3对应板子上的几个按键:

********************************************************

********************************************************

** Avnet/Digilent Arty Evaluation Board **

** LEDs and switches GPIO Demonstration **

********************************************************

********************************************************

**

Choose Task:

BTN0: Print PWM value.

BTN1: 'Cylon' LED display.

BTN2: Scrolling LED display.

BTN3: Return to this menu.

注: 只要用USB数据线连接上就行,查看串口会发现开发板占了两个USB,依次打开,第二个发现会有LOG输出

注: 此外上位机串口工具请参考: https://blog.csdn.net/zoujiachi666/article/details/79441340

LINKS

[1].Artix-7 35T Arty FPGA 评估套件官网

[2].vivado license在ubuntu上安装

[3].board fils下载地址

[4].Installing Vivado and Digilent Board Files

[5].Getting Started with Vivado

[6].Arty Programming Guide

[7].Programming Digilent FPGA Boards Through Multisim

@beautifulzzzz

智能硬件、物联网,热爱技术,关注产品

博客:http://blog.beautifulzzzz.com

园友交流群:414948975