到了CORTEX-M4,几乎每一快都有很大的知识量,单单GPIO库文件这一项就有很长的章节要描述,加油吧

GPIO.h。是最基础的一个库文件,下面结合数据手册来一一进行讲解:

先把库文件粘上,方便一一查阅:

/**************************************************************************//** * @file GPIO.h * @version V3.00 * $Revision: 21 $ * $Date: 15/08/11 10:26a $ * @brief M451 series GPIO driver header file * * @note * Copyright (C) 2011~2015 Nuvoton Technology Corp. All rights reserved. * ******************************************************************************/ #ifndef __GPIO_H__ #define __GPIO_H__ #ifdef __cplusplus extern "C" { #endif /** @addtogroup Standard_Driver Standard Driver @{ */ /** @addtogroup GPIO_Driver GPIO Driver @{ */ /** @addtogroup GPIO_EXPORTED_CONSTANTS GPIO Exported Constants @{ */ #define GPIO_PIN_MAX 16 /*!< Specify Maximum Pins of Each GPIO Port */ /*---------------------------------------------------------------------------------------------------------*/ /* GPIO_MODE Constant Definitions */ /*---------------------------------------------------------------------------------------------------------*/ #define GPIO_MODE_INPUT 0x0UL /*!< Input Mode */ #define GPIO_MODE_OUTPUT 0x1UL /*!< Output Mode */ #define GPIO_MODE_OPEN_DRAIN 0x2UL /*!< Open-Drain Mode */ #define GPIO_MODE_QUASI 0x3UL /*!< Quasi-bidirectional Mode */ /*---------------------------------------------------------------------------------------------------------*/ /* GPIO Interrupt Type Constant Definitions */ /*---------------------------------------------------------------------------------------------------------*/ #define GPIO_INT_RISING 0x00010000UL /*!< Interrupt enable by Input Rising Edge */ #define GPIO_INT_FALLING 0x00000001UL /*!< Interrupt enable by Input Falling Edge */ #define GPIO_INT_BOTH_EDGE 0x00010001UL /*!< Interrupt enable by both Rising Edge and Falling Edge */ #define GPIO_INT_HIGH 0x01010000UL /*!< Interrupt enable by Level-High */ #define GPIO_INT_LOW 0x01000001UL /*!< Interrupt enable by Level-Level */ /*---------------------------------------------------------------------------------------------------------*/ /* GPIO_INTTYPE Constant Definitions */ /*---------------------------------------------------------------------------------------------------------*/ #define GPIO_INTTYPE_EDGE 0UL /*!< GPIO_INTTYPE Setting for Edge Trigger Mode */ #define GPIO_INTTYPE_LEVEL 1UL /*!< GPIO_INTTYPE Setting for Edge Level Mode */ /*---------------------------------------------------------------------------------------------------------*/ /* GPIO_DBCTL Constant Definitions */ /*---------------------------------------------------------------------------------------------------------*/ #define GPIO_DBCTL_ICLK_ON 0x00000020UL /*!< GPIO_DBCTL setting for all IO pins edge detection circuit is always active after reset */ #define GPIO_DBCTL_ICLK_OFF 0x00000000UL /*!< GPIO_DBCTL setting for edge detection circuit is active only if IO pin corresponding GPIOx_IEN bit is set to 1 */ #define GPIO_DBCTL_DBCLKSRC_LIRC 0x00000010UL /*!< GPIO_DBCTL setting for de-bounce counter clock source is the internal 10 kHz */ #define GPIO_DBCTL_DBCLKSRC_HCLK 0x00000000UL /*!< GPIO_DBCTL setting for de-bounce counter clock source is the HCLK */ #define GPIO_DBCTL_DBCLKSEL_1 0x00000000UL /*!< GPIO_DBCTL setting for sampling cycle = 1 clocks */ #define GPIO_DBCTL_DBCLKSEL_2 0x00000001UL /*!< GPIO_DBCTL setting for sampling cycle = 2 clocks */ #define GPIO_DBCTL_DBCLKSEL_4 0x00000002UL /*!< GPIO_DBCTL setting for sampling cycle = 4 clocks */ #define GPIO_DBCTL_DBCLKSEL_8 0x00000003UL /*!< GPIO_DBCTL setting for sampling cycle = 8 clocks */ #define GPIO_DBCTL_DBCLKSEL_16 0x00000004UL /*!< GPIO_DBCTL setting for sampling cycle = 16 clocks */ #define GPIO_DBCTL_DBCLKSEL_32 0x00000005UL /*!< GPIO_DBCTL setting for sampling cycle = 32 clocks */ #define GPIO_DBCTL_DBCLKSEL_64 0x00000006UL /*!< GPIO_DBCTL setting for sampling cycle = 64 clocks */ #define GPIO_DBCTL_DBCLKSEL_128 0x00000007UL /*!< GPIO_DBCTL setting for sampling cycle = 128 clocks */ #define GPIO_DBCTL_DBCLKSEL_256 0x00000008UL /*!< GPIO_DBCTL setting for sampling cycle = 256 clocks */ #define GPIO_DBCTL_DBCLKSEL_512 0x00000009UL /*!< GPIO_DBCTL setting for sampling cycle = 512 clocks */ #define GPIO_DBCTL_DBCLKSEL_1024 0x0000000AUL /*!< GPIO_DBCTL setting for sampling cycle = 1024 clocks */ #define GPIO_DBCTL_DBCLKSEL_2048 0x0000000BUL /*!< GPIO_DBCTL setting for sampling cycle = 2048 clocks */ #define GPIO_DBCTL_DBCLKSEL_4096 0x0000000CUL /*!< GPIO_DBCTL setting for sampling cycle = 4096 clocks */ #define GPIO_DBCTL_DBCLKSEL_8192 0x0000000DUL /*!< GPIO_DBCTL setting for sampling cycle = 8192 clocks */ #define GPIO_DBCTL_DBCLKSEL_16384 0x0000000EUL /*!< GPIO_DBCTL setting for sampling cycle = 16384 clocks */ #define GPIO_DBCTL_DBCLKSEL_32768 0x0000000FUL /*!< GPIO_DBCTL setting for sampling cycle = 32768 clocks */ /* Define GPIO Pin Data Input/Output. It could be used to control each I/O pin by pin address mapping. Example 1: PA0 = 1; It is used to set GPIO PA.0 to high; Example 2: if (PA0) PA0 = 0; If GPIO PA.0 pin status is high, then set GPIO PA.0 data output to low. */ #define GPIO_PIN_DATA(port, pin) (*((volatile uint32_t *)((GPIO_PIN_DATA_BASE+(0x40*(port))) + ((pin)<<2)))) #define PA0 GPIO_PIN_DATA(0, 0 ) /*!< Specify PA.0 Pin Data Input/Output */ #define PA1 GPIO_PIN_DATA(0, 1 ) /*!< Specify PA.1 Pin Data Input/Output */ #define PA2 GPIO_PIN_DATA(0, 2 ) /*!< Specify PA.2 Pin Data Input/Output */ #define PA3 GPIO_PIN_DATA(0, 3 ) /*!< Specify PA.3 Pin Data Input/Output */ #define PA4 GPIO_PIN_DATA(0, 4 ) /*!< Specify PA.4 Pin Data Input/Output */ #define PA5 GPIO_PIN_DATA(0, 5 ) /*!< Specify PA.5 Pin Data Input/Output */ #define PA6 GPIO_PIN_DATA(0, 6 ) /*!< Specify PA.6 Pin Data Input/Output */ #define PA7 GPIO_PIN_DATA(0, 7 ) /*!< Specify PA.7 Pin Data Input/Output */ #define PA8 GPIO_PIN_DATA(0, 8 ) /*!< Specify PA.8 Pin Data Input/Output */ #define PA9 GPIO_PIN_DATA(0, 9 ) /*!< Specify PA.9 Pin Data Input/Output */ #define PA10 GPIO_PIN_DATA(0, 10) /*!< Specify PA.10 Pin Data Input/Output */ #define PA11 GPIO_PIN_DATA(0, 11) /*!< Specify PA.11 Pin Data Input/Output */ #define PA12 GPIO_PIN_DATA(0, 12) /*!< Specify PA.12 Pin Data Input/Output */ #define PA13 GPIO_PIN_DATA(0, 13) /*!< Specify PA.13 Pin Data Input/Output */ #define PA14 GPIO_PIN_DATA(0, 14) /*!< Specify PA.14 Pin Data Input/Output */ #define PA15 GPIO_PIN_DATA(0, 15) /*!< Specify PA.15 Pin Data Input/Output */ #define PB0 GPIO_PIN_DATA(1, 0 ) /*!< Specify PB.0 Pin Data Input/Output */ #define PB1 GPIO_PIN_DATA(1, 1 ) /*!< Specify PB.1 Pin Data Input/Output */ #define PB2 GPIO_PIN_DATA(1, 2 ) /*!< Specify PB.2 Pin Data Input/Output */ #define PB3 GPIO_PIN_DATA(1, 3 ) /*!< Specify PB.3 Pin Data Input/Output */ #define PB4 GPIO_PIN_DATA(1, 4 ) /*!< Specify PB.4 Pin Data Input/Output */ #define PB5 GPIO_PIN_DATA(1, 5 ) /*!< Specify PB.5 Pin Data Input/Output */ #define PB6 GPIO_PIN_DATA(1, 6 ) /*!< Specify PB.6 Pin Data Input/Output */ #define PB7 GPIO_PIN_DATA(1, 7 ) /*!< Specify PB.7 Pin Data Input/Output */ #define PB8 GPIO_PIN_DATA(1, 8 ) /*!< Specify PB.8 Pin Data Input/Output */ #define PB9 GPIO_PIN_DATA(1, 9 ) /*!< Specify PB.9 Pin Data Input/Output */ #define PB10 GPIO_PIN_DATA(1, 10) /*!< Specify PB.10 Pin Data Input/Output */ #define PB11 GPIO_PIN_DATA(1, 11) /*!< Specify PB.11 Pin Data Input/Output */ #define PB12 GPIO_PIN_DATA(1, 12) /*!< Specify PB.12 Pin Data Input/Output */ #define PB13 GPIO_PIN_DATA(1, 13) /*!< Specify PB.13 Pin Data Input/Output */ #define PB14 GPIO_PIN_DATA(1, 14) /*!< Specify PB.14 Pin Data Input/Output */ #define PB15 GPIO_PIN_DATA(1, 15) /*!< Specify PB.15 Pin Data Input/Output */ #define PC0 GPIO_PIN_DATA(2, 0 ) /*!< Specify PC.0 Pin Data Input/Output */ #define PC1 GPIO_PIN_DATA(2, 1 ) /*!< Specify PC.1 Pin Data Input/Output */ #define PC2 GPIO_PIN_DATA(2, 2 ) /*!< Specify PC.2 Pin Data Input/Output */ #define PC3 GPIO_PIN_DATA(2, 3 ) /*!< Specify PC.3 Pin Data Input/Output */ #define PC4 GPIO_PIN_DATA(2, 4 ) /*!< Specify PC.4 Pin Data Input/Output */ #define PC5 GPIO_PIN_DATA(2, 5 ) /*!< Specify PC.5 Pin Data Input/Output */ #define PC6 GPIO_PIN_DATA(2, 6 ) /*!< Specify PC.6 Pin Data Input/Output */ #define PC7 GPIO_PIN_DATA(2, 7 ) /*!< Specify PC.7 Pin Data Input/Output */ #define PC8 GPIO_PIN_DATA(2, 8 ) /*!< Specify PC.8 Pin Data Input/Output */ #define PC9 GPIO_PIN_DATA(2, 9 ) /*!< Specify PC.9 Pin Data Input/Output */ #define PC10 GPIO_PIN_DATA(2, 10) /*!< Specify PC.10 Pin Data Input/Output */ #define PC11 GPIO_PIN_DATA(2, 11) /*!< Specify PC.11 Pin Data Input/Output */ #define PC12 GPIO_PIN_DATA(2, 12) /*!< Specify PC.12 Pin Data Input/Output */ #define PC13 GPIO_PIN_DATA(2, 13) /*!< Specify PC.13 Pin Data Input/Output */ #define PC14 GPIO_PIN_DATA(2, 14) /*!< Specify PC.14 Pin Data Input/Output */ #define PC15 GPIO_PIN_DATA(2, 15) /*!< Specify PC.15 Pin Data Input/Output */ #define PD0 GPIO_PIN_DATA(3, 0 ) /*!< Specify PD.0 Pin Data Input/Output */ #define PD1 GPIO_PIN_DATA(3, 1 ) /*!< Specify PD.1 Pin Data Input/Output */ #define PD2 GPIO_PIN_DATA(3, 2 ) /*!< Specify PD.2 Pin Data Input/Output */ #define PD3 GPIO_PIN_DATA(3, 3 ) /*!< Specify PD.3 Pin Data Input/Output */ #define PD4 GPIO_PIN_DATA(3, 4 ) /*!< Specify PD.4 Pin Data Input/Output */ #define PD5 GPIO_PIN_DATA(3, 5 ) /*!< Specify PD.5 Pin Data Input/Output */ #define PD6 GPIO_PIN_DATA(3, 6 ) /*!< Specify PD.6 Pin Data Input/Output */ #define PD7 GPIO_PIN_DATA(3, 7 ) /*!< Specify PD.7 Pin Data Input/Output */ #define PD8 GPIO_PIN_DATA(3, 8 ) /*!< Specify PD.8 Pin Data Input/Output */ #define PD9 GPIO_PIN_DATA(3, 9 ) /*!< Specify PD.9 Pin Data Input/Output */ #define PD10 GPIO_PIN_DATA(3, 10) /*!< Specify PD.10 Pin Data Input/Output */ #define PD11 GPIO_PIN_DATA(3, 11) /*!< Specify PD.11 Pin Data Input/Output */ #define PD12 GPIO_PIN_DATA(3, 12) /*!< Specify PD.12 Pin Data Input/Output */ #define PD13 GPIO_PIN_DATA(3, 13) /*!< Specify PD.13 Pin Data Input/Output */ #define PD14 GPIO_PIN_DATA(3, 14) /*!< Specify PD.14 Pin Data Input/Output */ #define PD15 GPIO_PIN_DATA(3, 15) /*!< Specify PD.15 Pin Data Input/Output */ #define PE0 GPIO_PIN_DATA(4, 0 ) /*!< Specify PE.0 Pin Data Input/Output */ #define PE1 GPIO_PIN_DATA(4, 1 ) /*!< Specify PE.1 Pin Data Input/Output */ #define PE2 GPIO_PIN_DATA(4, 2 ) /*!< Specify PE.2 Pin Data Input/Output */ #define PE3 GPIO_PIN_DATA(4, 3 ) /*!< Specify PE.3 Pin Data Input/Output */ #define PE4 GPIO_PIN_DATA(4, 4 ) /*!< Specify PE.4 Pin Data Input/Output */ #define PE5 GPIO_PIN_DATA(4, 5 ) /*!< Specify PE.5 Pin Data Input/Output */ #define PE6 GPIO_PIN_DATA(4, 6 ) /*!< Specify PE.6 Pin Data Input/Output */ #define PE7 GPIO_PIN_DATA(4, 7 ) /*!< Specify PE.7 Pin Data Input/Output */ #define PE8 GPIO_PIN_DATA(4, 8 ) /*!< Specify PE.8 Pin Data Input/Output */ #define PE9 GPIO_PIN_DATA(4, 9 ) /*!< Specify PE.9 Pin Data Input/Output */ #define PE10 GPIO_PIN_DATA(4, 10) /*!< Specify PE.10 Pin Data Input/Output */ #define PE11 GPIO_PIN_DATA(4, 11) /*!< Specify PE.11 Pin Data Input/Output */ #define PE12 GPIO_PIN_DATA(4, 12) /*!< Specify PE.12 Pin Data Input/Output */ #define PE13 GPIO_PIN_DATA(4, 13) /*!< Specify PE.13 Pin Data Input/Output */ #define PE14 GPIO_PIN_DATA(4, 14) /*!< Specify PE.14 Pin Data Input/Output */ #define PF0 GPIO_PIN_DATA(5, 0 ) /*!< Specify PF.0 Pin Data Input/Output */ #define PF1 GPIO_PIN_DATA(5, 1 ) /*!< Specify PF.1 Pin Data Input/Output */ #define PF2 GPIO_PIN_DATA(5, 2 ) /*!< Specify PF.2 Pin Data Input/Output */ #define PF3 GPIO_PIN_DATA(5, 3 ) /*!< Specify PF.3 Pin Data Input/Output */ #define PF4 GPIO_PIN_DATA(5, 4 ) /*!< Specify PF.4 Pin Data Input/Output */ #define PF5 GPIO_PIN_DATA(5, 5 ) /*!< Specify PF.5 Pin Data Input/Output */ #define PF6 GPIO_PIN_DATA(5, 6 ) /*!< Specify PF.6 Pin Data Input/Output */ #define PF7 GPIO_PIN_DATA(5, 7 ) /*!< Specify PF.7 Pin Data Input/Output */ /*@}*/ /* end of group GPIO_EXPORTED_CONSTANTS */ /** @addtogroup GPIO_EXPORTED_FUNCTIONS GPIO Exported Functions @{ */ /** * @brief Clear GPIO Pin Interrupt Flag * * @param[in] port GPIO port. It could be PA, PB, PC, PD, PE or PF. * @param[in] u32PinMask The single or multiple pins of specified GPIO port. * It could be BIT0 ~ BIT15 for PA, PB, PC and PD. * It could be BIT0 ~ BIT14 for PE. * It could be BIT0 ~ BIT7 for PF. * * @return None * * @details Clear the interrupt status of specified GPIO pin. */ #define GPIO_CLR_INT_FLAG(port, u32PinMask) ((port)->INTSRC = (u32PinMask)) /** * @brief Disable Pin De-bounce Function * * @param[in] port GPIO port. It could be PA, PB, PC, PD, PE or PF. * @param[in] u32PinMask The single or multiple pins of specified GPIO port. * It could be BIT0 ~ BIT15 for PA, PB, PC and PD. * It could be BIT0 ~ BIT14 for PE. * It could be BIT0 ~ BIT7 for PF. * * @return None * * @details Disable the interrupt de-bounce function of specified GPIO pin. */ #define GPIO_DISABLE_DEBOUNCE(port, u32PinMask) ((port)->DBEN &= ~(u32PinMask)) /** * @brief Enable Pin De-bounce Function * * @param[in] port GPIO port. It could be PA, PB, PC, PD, PE or PF. * @param[in] u32PinMask The single or multiple pins of specified GPIO port. * It could be BIT0 ~ BIT15 for PA, PB, PC and PD. * It could be BIT0 ~ BIT14 for PE. * It could be BIT0 ~ BIT7 for PF. * @return None * * @details Enable the interrupt de-bounce function of specified GPIO pin. */ #define GPIO_ENABLE_DEBOUNCE(port, u32PinMask) ((port)->DBEN |= (u32PinMask)) /** * @brief Disable I/O Digital Input Path * * @param[in] port GPIO port. It could be PA, PB, PC, PD, PE or PF. * @param[in] u32PinMask The single or multiple pins of specified GPIO port. * It could be BIT0 ~ BIT15 for PA, PB, PC and PD. * It could be BIT0 ~ BIT14 for PE. * It could be BIT0 ~ BIT7 for PF. * * @return None * * @details Disable I/O digital input path of specified GPIO pin. */ #define GPIO_DISABLE_DIGITAL_PATH(port, u32PinMask) ((port)->DINOFF |= ((u32PinMask)<<16)) /** * @brief Enable I/O Digital Input Path * * @param[in] port GPIO port. It could be PA, PB, PC, PD, PE or PF. * @param[in] u32PinMask The single or multiple pins of specified GPIO port. * It could be BIT0 ~ BIT15 for PA, PB, PC and PD. * It could be BIT0 ~ BIT14 for PE. * It could be BIT0 ~ BIT7 for PF. * * @return None * * @details Enable I/O digital input path of specified GPIO pin. */ #define GPIO_ENABLE_DIGITAL_PATH(port, u32PinMask) ((port)->DINOFF &= ~((u32PinMask)<<16)) /** * @brief Disable I/O DOUT mask * * @param[in] port GPIO port. It could be PA, PB, PC, PD, PE or PF. * @param[in] u32PinMask The single or multiple pins of specified GPIO port. * It could be BIT0 ~ BIT15 for PA, PB, PC and PD. * It could be BIT0 ~ BIT14 for PE. * It could be BIT0 ~ BIT7 for PF. * * @return None * * @details Disable I/O DOUT mask of specified GPIO pin. */ #define GPIO_DISABLE_DOUT_MASK(port, u32PinMask) ((port)->DATMSK &= ~(u32PinMask)) /** * @brief Enable I/O DOUT mask * * @param[in] port GPIO port. It could be PA, PB, PC, PD, PE or PF. * @param[in] u32PinMask The single or multiple pins of specified GPIO port. * It could be BIT0 ~ BIT15 for PA, PB, PC and PD. * It could be BIT0 ~ BIT14 for PE. * It could be BIT0 ~ BIT7 for PF. * * @return None * * @details Enable I/O DOUT mask of specified GPIO pin. */ #define GPIO_ENABLE_DOUT_MASK(port, u32PinMask) ((port)->DATMSK |= (u32PinMask)) /** * @brief Get GPIO Pin Interrupt Flag * * @param[in] port GPIO port. It could be PA, PB, PC, PD, PE or PF. * @param[in] u32PinMask The single or multiple pins of specified GPIO port. * It could be BIT0 ~ BIT15 for PA, PB, PC and PD. * It could be BIT0 ~ BIT14 for PE. * It could be BIT0 ~ BIT7 for PF. * * @retval 0 No interrupt at specified GPIO pin * @retval 1 The specified GPIO pin generate an interrupt * * @details Get the interrupt status of specified GPIO pin. */ #define GPIO_GET_INT_FLAG(port, u32PinMask) ((port)->INTSRC & (u32PinMask)) /** * @brief Set De-bounce Sampling Cycle Time * * @param[in] u32ClkSrc The de-bounce counter clock source. It could be GPIO_DBCTL_DBCLKSRC_HCLK or GPIO_DBCTL_DBCLKSRC_LIRC. * @param[in] u32ClkSel The de-bounce sampling cycle selection. It could be * - ef GPIO_DBCTL_DBCLKSEL_1 * - ef GPIO_DBCTL_DBCLKSEL_2 * - ef GPIO_DBCTL_DBCLKSEL_4 * - ef GPIO_DBCTL_DBCLKSEL_8 * - ef GPIO_DBCTL_DBCLKSEL_16 * - ef GPIO_DBCTL_DBCLKSEL_32 * - ef GPIO_DBCTL_DBCLKSEL_64 * - ef GPIO_DBCTL_DBCLKSEL_128 * - ef GPIO_DBCTL_DBCLKSEL_256 * - ef GPIO_DBCTL_DBCLKSEL_512 * - ef GPIO_DBCTL_DBCLKSEL_1024 * - ef GPIO_DBCTL_DBCLKSEL_2048 * - ef GPIO_DBCTL_DBCLKSEL_4096 * - ef GPIO_DBCTL_DBCLKSEL_8192 * - ef GPIO_DBCTL_DBCLKSEL_16384 * - ef GPIO_DBCTL_DBCLKSEL_32768 * * @return None * * @details Set the interrupt de-bounce sampling cycle time based on the debounce counter clock source. * Example: _GPIO_SET_DEBOUNCE_TIME(GPIO_DBCTL_DBCLKSRC_LIRC, GPIO_DBCTL_DBCLKSEL_4). * It's meaning the De-debounce counter clock source is internal 10 KHz and sampling cycle selection is 4. * Then the target de-bounce sampling cycle time is (4)*(1/(10*1000)) s = 4*0.0001 s = 400 us, * and system will sampling interrupt input once per 00 us. */ #define GPIO_SET_DEBOUNCE_TIME(u32ClkSrc, u32ClkSel) (GPIO->DBCTL = (GPIO_DBCTL_ICLKON_Msk | (u32ClkSrc) | (u32ClkSel))) /** * @brief Get GPIO Port IN Data * * @param[in] port GPIO port. It could be PA, PB, PC, PD, PE or PF. * * @return The specified port data * * @details Get the PIN register of specified GPIO port. */ #define GPIO_GET_IN_DATA(port) ((port)->PIN) /** * @brief Set GPIO Port OUT Data * * @param[in] port GPIO port. It could be PA, PB, PC, PD, PE or PF. * @param[in] u32Data GPIO port data. * * @return None * * @details Set the Data into specified GPIO port. */ #define GPIO_SET_OUT_DATA(port, u32Data) ((port)->DOUT = (u32Data)) /** * @brief Toggle Specified GPIO pin * * @param[in] u32Pin Pxy * * @return None * * @details Toggle the specified GPIO pint. */ #define GPIO_TOGGLE(u32Pin) ((u32Pin) ^= 1) /** * @brief Enable External GPIO interrupt * * @param[in] port GPIO port. It could be PA, PB, PC, PD, PE or PF. * @param[in] u32Pin The pin of specified GPIO port. * It could be 0 ~ 15 for PA, PB, PC and PD GPIO port. * It could be 0 ~ 14 for PE GPIO port. * It could be 0 ~ 7 for PF GPIO port. * @param[in] u32IntAttribs The interrupt attribute of specified GPIO pin. It could be * GPIO_INT_RISING, GPIO_INT_FALLING, GPIO_INT_BOTH_EDGE, GPIO_INT_HIGH, GPIO_INT_LOW. * * @return None * * @details This function is used to enable specified GPIO pin interrupt. */ #define GPIO_EnableEINT GPIO_EnableInt /** * @brief Disable External GPIO interrupt * * @param[in] port GPIO port. It could be PA, PB, PC, PD, PE or PF. * @param[in] u32Pin The pin of specified GPIO port. * It could be 0 ~ 15 for PA, PB, PC and PD GPIO port. * It could be 0 ~ 14 for PE GPIO port. * It could be 0 ~ 7 for PF GPIO port. * * @return None * * @details This function is used to enable specified GPIO pin interrupt. */ #define GPIO_DisableEINT GPIO_DisableInt void GPIO_SetMode(GPIO_T *port, uint32_t u32PinMask, uint32_t u32Mode); void GPIO_EnableInt(GPIO_T *port, uint32_t u32Pin, uint32_t u32IntAttribs); void GPIO_DisableInt(GPIO_T *port, uint32_t u32Pin); /*@}*/ /* end of group GPIO_EXPORTED_FUNCTIONS */ /*@}*/ /* end of group GPIO_Driver */ /*@}*/ /* end of group Standard_Driver */ #ifdef __cplusplus } #endif #endif // __GPIO_H__ /*** (C) COPYRIGHT 2013~2015 Nuvoton Technology Corp. ***/

/**************************************************************************//** * @file gpio.c * @version V3.00 * $Revision: 6 $ * $Date: 15/08/11 10:26a $ * @brief M451 series GPIO driver source file * * @note * Copyright (C) 2014~2015 Nuvoton Technology Corp. All rights reserved. *****************************************************************************/ #include "M451Series.h" /** @addtogroup Standard_Driver Standard Driver @{ */ /** @addtogroup GPIO_Driver GPIO Driver @{ */ /** @addtogroup GPIO_EXPORTED_FUNCTIONS GPIO Exported Functions @{ */ /** * @brief Set GPIO operation mode * * @param[in] port GPIO port. It could be PA, PB, PC, PD, PE or PF. * @param[in] u32PinMask The single or multiple pins of specified GPIO port. * It could be BIT0 ~ BIT15 for PA, PB, PC and PD GPIO port. * It could be BIT0 ~ BIT14 for PE GPIO port. * It could be BIT0 ~ BIT7 for PF GPIO port. * @param[in] u32Mode Operation mode. It could be * GPIO_MODE_INPUT, GPIO_MODE_OUTPUT, GPIO_MODE_OPEN_DRAIN, GPIO_MODE_QUASI. * * @return None * * @details This function is used to set specified GPIO operation mode. */ void GPIO_SetMode(GPIO_T *port, uint32_t u32PinMask, uint32_t u32Mode) { uint32_t i; for(i = 0; i < GPIO_PIN_MAX; i++) { if(u32PinMask & (1 << i)) { port->MODE = (port->MODE & ~(0x3 << (i << 1))) | (u32Mode << (i << 1)); } } } /** * @brief Enable GPIO interrupt * * @param[in] port GPIO port. It could be PA, PB, PC, PD, PE or PF. * @param[in] u32Pin The pin of specified GPIO port. * It could be 0 ~ 15 for PA, PB, PC and PD GPIO port. * It could be 0 ~ 14 for PE GPIO port. * It could be 0 ~ 7 for PF GPIO port. * @param[in] u32IntAttribs The interrupt attribute of specified GPIO pin. It could be * GPIO_INT_RISING, GPIO_INT_FALLING, GPIO_INT_BOTH_EDGE, GPIO_INT_HIGH, GPIO_INT_LOW. * * @return None * * @details This function is used to enable specified GPIO pin interrupt. */ void GPIO_EnableInt(GPIO_T *port, uint32_t u32Pin, uint32_t u32IntAttribs) { port->INTTYPE |= (((u32IntAttribs >> 24) & 0xFFUL) << u32Pin); port->INTEN |= ((u32IntAttribs & 0xFFFFFFUL) << u32Pin); } /** * @brief Disable GPIO interrupt * * @param[in] port GPIO port. It could be PA, PB, PC, PD, PE or PF. * @param[in] u32Pin The pin of specified GPIO port. * It could be 0 ~ 15 for PA, PB, PC and PD GPIO port. * It could be 0 ~ 14 for PE GPIO port. * It could be 0 ~ 7 for PF GPIO port. * * @return None * * @details This function is used to enable specified GPIO pin interrupt. */ void GPIO_DisableInt(GPIO_T *port, uint32_t u32Pin) { port->INTTYPE &= ~(1UL << u32Pin); port->INTEN &= ~((0x00010001UL) << u32Pin); } /*@}*/ /* end of group GPIO_EXPORTED_FUNCTIONS */ /*@}*/ /* end of group GPIO_Driver */ /*@}*/ /* end of group Standard_Driver */ /*** (C) COPYRIGHT 2014~2015 Nuvoton Technology Corp. ***/

以上是它的底层库函数,也没有什么复杂的东西,用以上的库函数就可以进行编程了,按键和LED的例子就是用库函数进行编程,下面我就结合数据手册,利用寄存器来给M451进行配置;

NuMicro NUC451 系列多达87个通用I/O管脚和其他功能管脚共享,这取决于芯片的配置。87个管脚分配在PA, PB, PC, PD, PE 和 PF六个端口上。PA, PB, PC, 和 PD最多有16个管脚,PE最多15个管脚,PF最多8个管脚。每个管脚都是独立的,都有相应的寄存器位来控制管脚功能模式与数据。

I/O管脚的I状态可由软件独立地配置为输入,推挽式的输出,开漏或准双向模式。复位之后,所有管脚的模式取决于CIOIN (CONFIG0[10])的设置。每个I/O管脚有一个阻值为110K~300K的弱上拉电阻接到VDD 上,VDD范围从5.0 V 到2.5 V。

6.6.2 特性

四种 I/O 模式:

准双向模式

推挽输出

开漏输出

高阻态输入

可选TTL/Schmitt 触发输入

I/O可以配置为边沿/电平触发的中断源

支持高驱动力及高翻转速率的I/O模式。

通过CIOINI (CONFIG0[10])可配置所有I/O复位之后的默认模式。

如果CIOIN = 0, 复位后所有的GPIO管脚是准双向模式

如果CIOIN = 1, 复位后所有的GPIO管脚是输入模式

I/O管脚仅在准双向模式,内部上拉电阻才使能。

使能管脚中断功能同时也使能了GPIO唤醒功能。

基本配置

GPIO管脚通过配置SYS_GPA_MFPL, SYS_GPA_MFPH, SYS_GPB_MFPL, SYS_GPB_MFPH,SYS_GPC_MFPL, SYS_GPC_MFPH, SYS_GPD_MFPL, SYS_GPD_MFPH, SYS_GPE_MFPL, SYS_GPE_MFPH 和SYS_GPF_MFPL寄存器来设定相应的功能

比如配置串口模块的引脚

/* Set PD multi-function pins for UART0 RXD(PD.0) and TXD(PD.1) */ SYS->GPD_MFPL &= ~(SYS_GPD_MFPL_PD0MFP_Msk | SYS_GPD_MFPL_PD1MFP_Msk); SYS->GPD_MFPL |= (SYS_GPD_MFPL_PD0MFP_UART0_RXD | SYS_GPD_MFPL_PD1MFP_UART0_TXD);

功能描述

输入模式

设置 MODEn (Px_MODE[2n+1:2n]) 为00, Px.n 管脚为输入模式,I/O管脚为三态(高阻),没有输

出驱动能力。管脚 (Px_PIN[n]) 的值反映相应端口的状态。

PD->MODE = (PD->MODE & (~GPIO_MODE_MODE7_Msk)) | (GPIO_MODE_INPUT << GPIO_MODE_MODE7_Pos);

推挽输出模式

设置 MODEn (Px_MODE[2n+1:2n]) 为 01, Px.n 管脚为推挽输出模式,I/O支持数字输出功能,有

拉/灌电流能力。DOUT (Px_DOUT[n]) 相应位bit[n]的值被送到相应管脚上。

PB->MODE = (PB->MODE & (~GPIO_MODE_MODE3_Msk)) | (GPIO_MODE_OUTPUT << GPIO_MODE_MODE3_Pos);

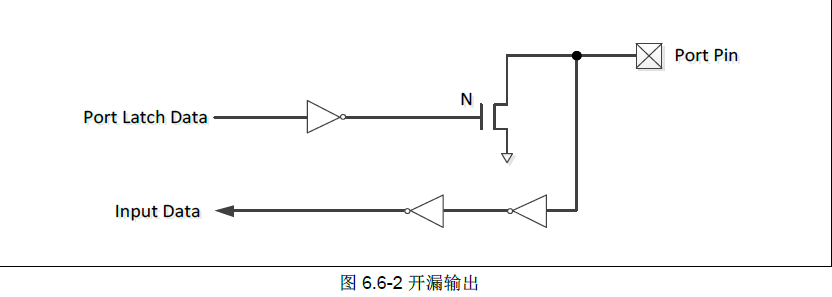

开漏输出模式

设置 MODEn (Px_MODE[2n+1:2n]) 为 10, Px.n 管脚为开漏模式且I/O管脚数字输出功能仅支持灌

电流, 驱动到高电平需要一个外加上拉电阻。如果DOUT (Px_DOUT[n]) 相应位为‘0’, 管脚上输出低.

如果DOUT (Px_DOUT[n]) 相应位为‘1’, 该管脚输出为高阻,可以由外部上拉电阻控制。

PB->MODE = (PB->MODE & (~GPIO_MODE_MODE3_Msk)) | (GPIO_MODE_QUASI << GPIO_MODE_MODE3_Pos);

PD->MODE = (PD->MODE & (~GPIO_MODE_MODE7_Msk)) | (GPIO_MODE_QUASI << GPIO_MODE_MODE7_Pos);

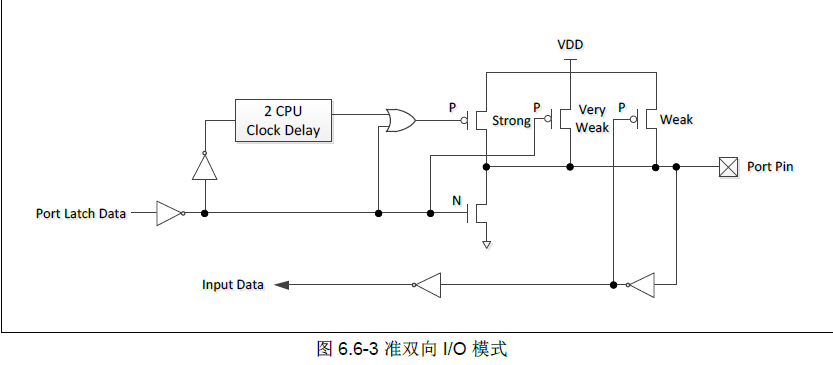

设置MODEn (Px_MODE[2n+1:2n])为11,Px.n 管脚为准双向模式,I/O同时支持数字输出和输入功

能,但拉电流能力仅达数百uA。要实现数字输入,需要先将DOUT (Px_DOUT[n])相应位置1。准双

向输出是80C51 及其派生产品常见的模式。若DOUT (Px_DOUT[n])相应位bit[n]为‘0’ ,管脚上输出

为“低”。若DOUT (Px_DOUT[n])相应位bit[n]为‘1’,该管脚将检测管脚值。若管脚值为高,没有任何

动作,若管脚值为低,在该管脚上将有强输出驱动2个时钟周期的高电平,然后禁止强输出驱动,

其后管脚状态由内部上拉电阻控制。注意: 准双向模式source电流的大小仅有200 uA到30 uA(相应

VDD的电压从5.0 V到2.5 V) 。

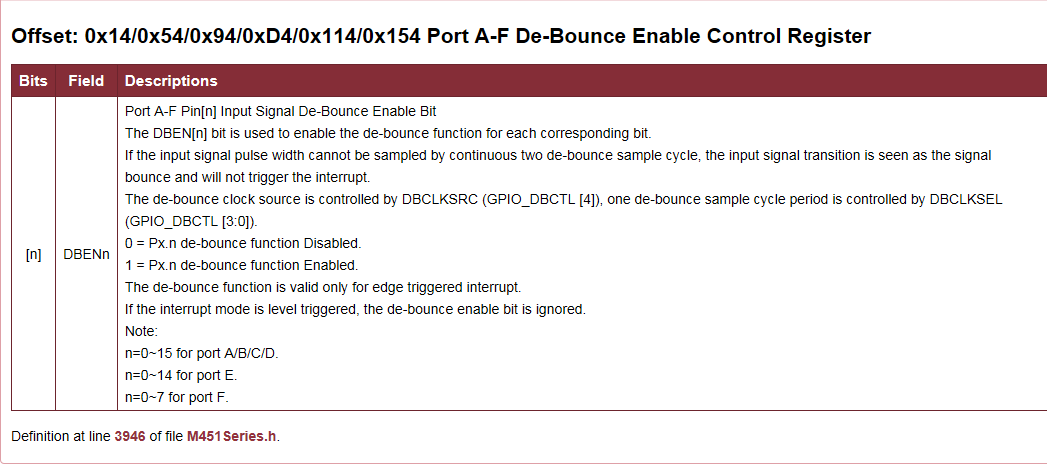

GPIO中断和唤醒功能

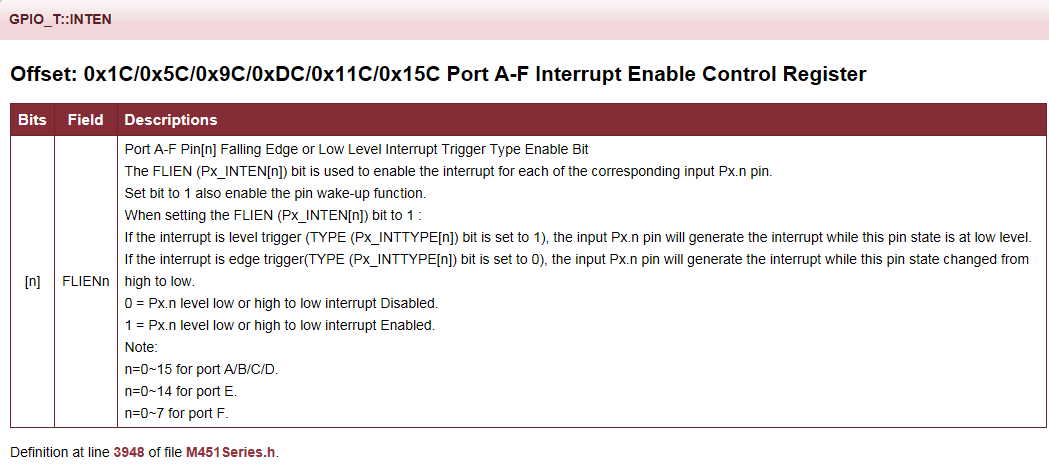

每个GPIO管脚都可以通过RHIEN (Px_INTEN[n+16])/FLIEN (Px_INTEN[n])位和TYPE (Px_INTTYPE[n])设置成芯片的中断源。有五种中断触发条件可以设置:低电平触发、高电平触发、下降沿触发和上升沿触发以及上升与下降沿同时触发。在边沿触发中用户可以通过使能输入信号去抖功能来阻止由噪声引起的意外中断。去抖时钟源和采样周期可以通过DBCLKSRC (GPIO_DBCTL[4]) 和DBCLKSEL (GPIO_DBCTL[3:0]) 寄存器来设置。

当芯片进入Idle/Power-down模式时,GPIO也可以唤醒系统。设置GPIO为唤醒触发的条件与GPIO中断触发的条件相同。

/* Configure PB.2 as Input mode and enable interrupt by rising edge trigger */ PB->MODE = (PB->MODE & (~GPIO_MODE_MODE2_Msk)) | (GPIO_MODE_INPUT << GPIO_MODE_MODE2_Pos); PB->INTTYPE |= (GPIO_INTTYPE_EDGE << GPIO_INTTYPE_TYPE2_Pos); PB->INTEN |= GPIO_INTEN_RHIEN2_Msk; NVIC_EnableIRQ(GPB_IRQn); /* Configure PC.5 as Quasi-bidirection mode and enable interrupt by falling edge trigger */ PC->MODE = (PC->MODE & (~GPIO_MODE_MODE5_Msk)) | (GPIO_MODE_QUASI << GPIO_MODE_MODE5_Pos); PC->INTTYPE |= (GPIO_INTTYPE_EDGE << GPIO_INTTYPE_TYPE5_Pos); PC->INTEN |= GPIO_INTEN_FLIEN5_Msk; NVIC_EnableIRQ(GPC_IRQn); /* Enable interrupt de-bounce function and select de-bounce sampling cycle time is 1024 clocks of LIRC clock */ GPIO->DBCTL = (GPIO_DBCTL_ICLK_ON | GPIO_DBCTL_DBCLKSRC_LIRC | GPIO_DBCTL_DBCLKSEL_1024); PB->DBEN |= BIT2; PC->DBEN |= BIT5;

如果上文有对数据手册不了解的,可以对照下文的数据手册一一阅读

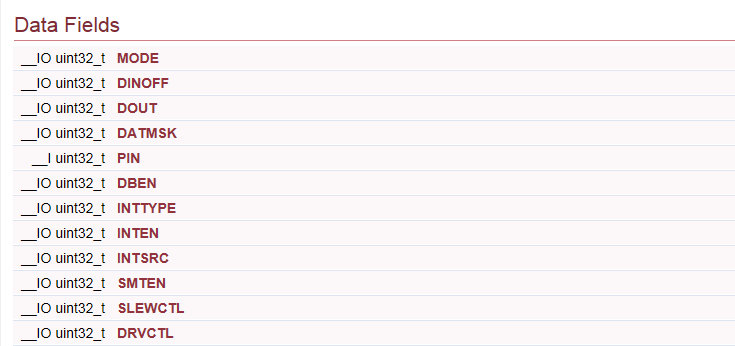

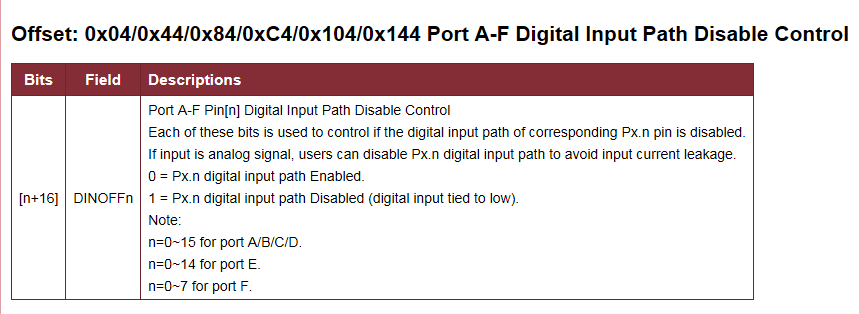

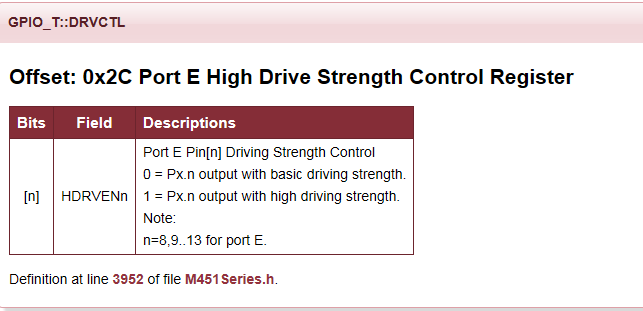

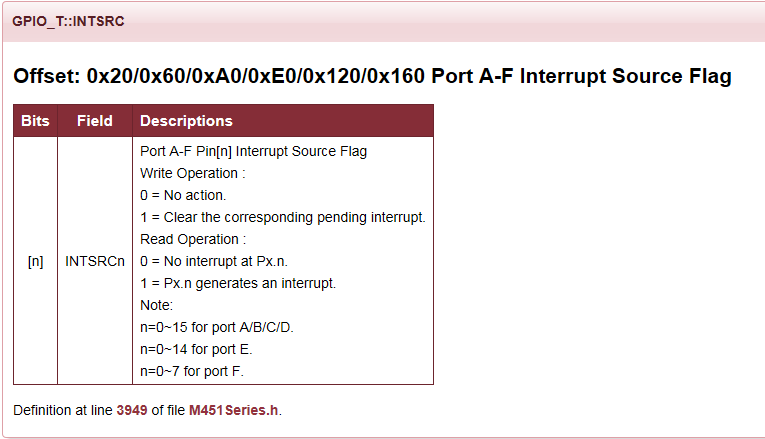

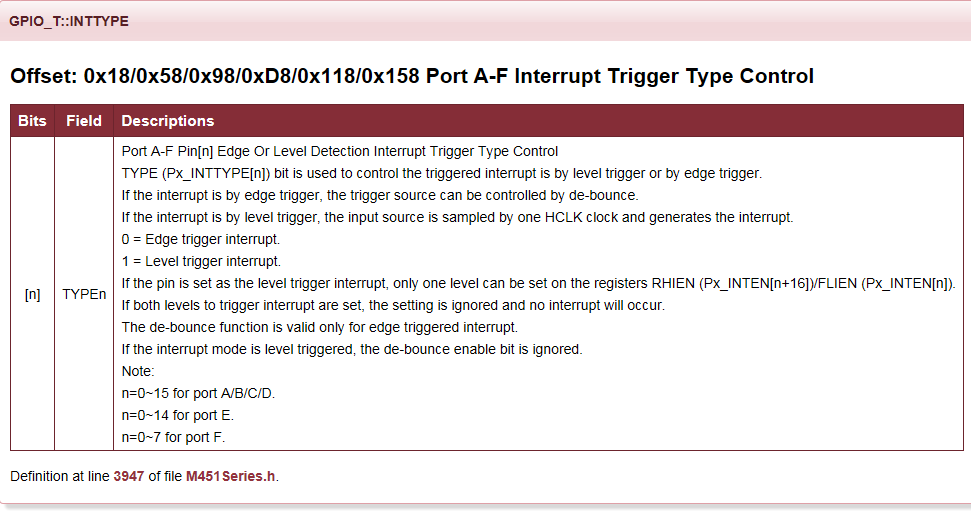

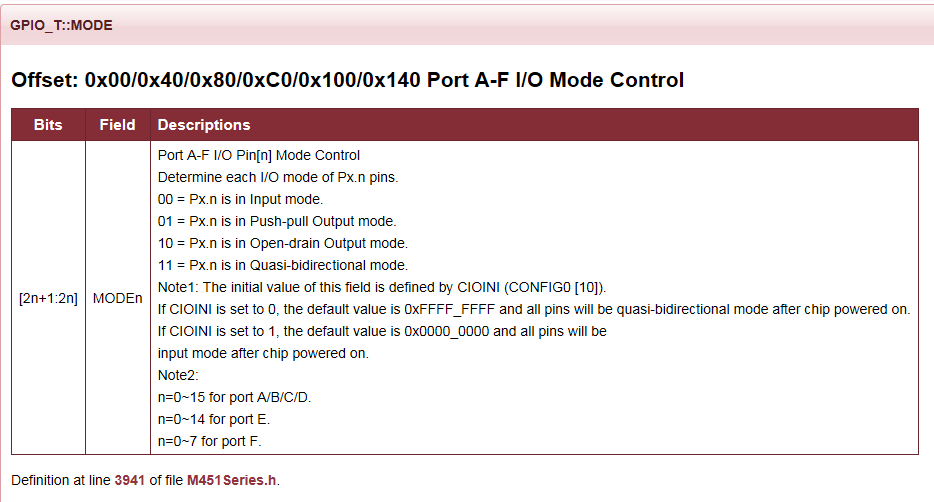

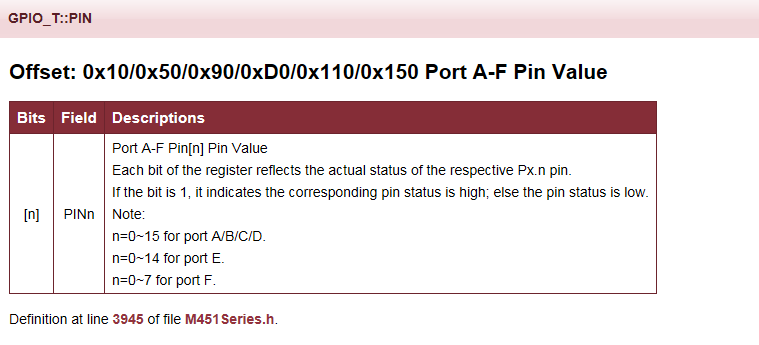

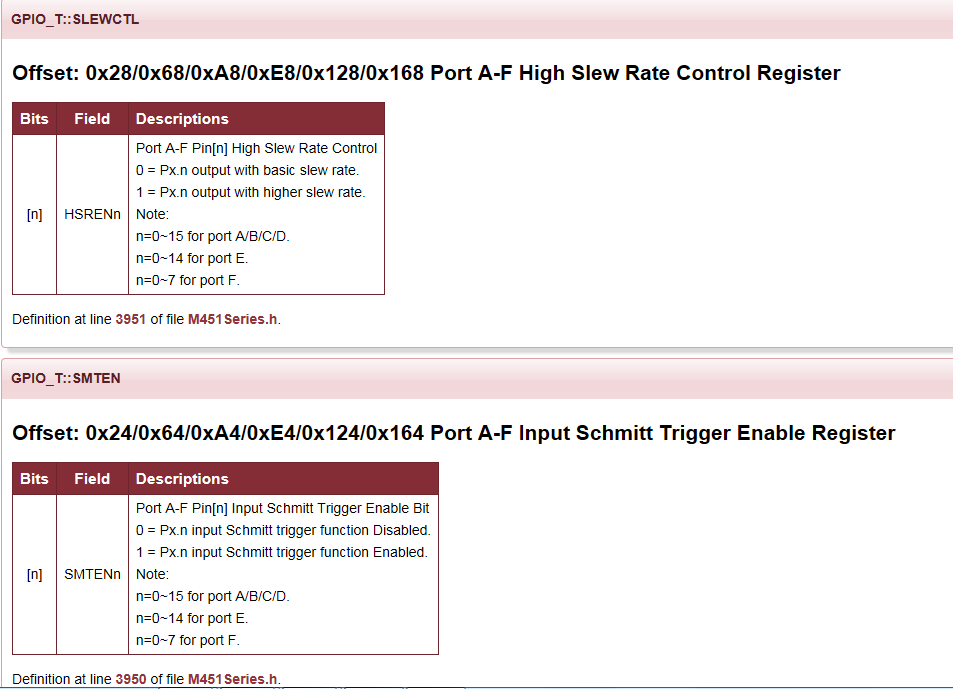

typedef struct { /** * @var GPIO_T::MODE * Offset: 0x00/0x40/0x80/0xC0/0x100/0x140 Port A-F I/O Mode Control * --------------------------------------------------------------------------------------------------- * |Bits |Field |Descriptions * | :----: | :----: | :---- | * |[2n+1:2n]|MODEn |Port A-F I/O Pin[n] Mode Control * | | |Determine each I/O mode of Px.n pins. * | | |00 = Px.n is in Input mode. * | | |01 = Px.n is in Push-pull Output mode. * | | |10 = Px.n is in Open-drain Output mode. * | | |11 = Px.n is in Quasi-bidirectional mode. * | | |Note1: The initial value of this field is defined by CIOINI (CONFIG0 [10]). * | | |If CIOINI is set to 0, the default value is 0xFFFF_FFFF and all pins will be quasi-bidirectional mode after chip powered on. * | | |If CIOINI is set to 1, the default value is 0x0000_0000 and all pins will be * | | |input mode after chip powered on. * | | |Note2: * | | |n=0~15 for port A/B/C/D. * | | |n=0~14 for port E. * | | |n=0~7 for port F. * @var GPIO_T::DINOFF * Offset: 0x04/0x44/0x84/0xC4/0x104/0x144 Port A-F Digital Input Path Disable Control * --------------------------------------------------------------------------------------------------- * |Bits |Field |Descriptions * | :----: | :----: | :---- | * |[n+16] |DINOFFn |Port A-F Pin[n] Digital Input Path Disable Control * | | |Each of these bits is used to control if the digital input path of corresponding Px.n pin is disabled. * | | |If input is analog signal, users can disable Px.n digital input path to avoid input current leakage. * | | |0 = Px.n digital input path Enabled. * | | |1 = Px.n digital input path Disabled (digital input tied to low). * | | |Note: * | | |n=0~15 for port A/B/C/D. * | | |n=0~14 for port E. * | | |n=0~7 for port F. * @var GPIO_T::DOUT * Offset: 0x08/0x48/0x88/0xC8/0x108/0x148 Port A-F Data Output Value * --------------------------------------------------------------------------------------------------- * |Bits |Field |Descriptions * | :----: | :----: | :---- | * |[n] |DOUTn |Port A-F Pin[n] Output Value * | | |Each of these bits controls the status of a Px.n pin when the Px.n is configured as Push-pull output, Open-drain output or Quasi-bidirectional mode. * | | |0 = Px.n will drive Low if the Px.n pin is configured as Push-pull output, Open-drain output or Quasi-bidirectional mode. * | | |1 = Px.n will drive High if the Px.n pin is configured as Push-pull output or Quasi-bidirectional mode. * | | |Note: * | | |n=0~15 for port A/B/C/D. * | | |n=0~14 for port E. * | | |n=0~7 for port F. * @var GPIO_T::DATMSK * Offset: 0x0C/0x4C/0x8C/0xCC/0x10C/0x14C Port A-F Data Output Write Mask * --------------------------------------------------------------------------------------------------- * |Bits |Field |Descriptions * | :----: | :----: | :---- | * |[n] |DMASKn |Port A-F Pin[n] Data Output Write Mask * | | |These bits are used to protect the corresponding DOUT (Px_DOUT[n]) bit. * | | |When the DATMSK (Px_DATMSK[n]) bit is set to 1, the corresponding DOUT (Px_DOUT[n]) bit is protected. * | | |If the write signal is masked, writing data to the protect bit is ignored. * | | |0 = Corresponding DOUT (Px_DOUT[n]) bit can be updated. * | | |1 = Corresponding DOUT (Px_DOUT[n]) bit protected. * | | |Note1: This function only protects the corresponding DOUT (Px_DOUT[n]) bit, and will not protect the corresponding PDIO (Pxn_PDIO[0]) bit. * | | |Note2: * | | |n=0~15 for port A/B/C/D. * | | |n=0~14 for port E. * | | |n=0~7 for port F. * @var GPIO_T::PIN * Offset: 0x10/0x50/0x90/0xD0/0x110/0x150 Port A-F Pin Value * --------------------------------------------------------------------------------------------------- * |Bits |Field |Descriptions * | :----: | :----: | :---- | * |[n] |PINn |Port A-F Pin[n] Pin Value * | | |Each bit of the register reflects the actual status of the respective Px.n pin. * | | |If the bit is 1, it indicates the corresponding pin status is high; else the pin status is low. * | | |Note: * | | |n=0~15 for port A/B/C/D. * | | |n=0~14 for port E. * | | |n=0~7 for port F. * @var GPIO_T::DBEN * Offset: 0x14/0x54/0x94/0xD4/0x114/0x154 Port A-F De-Bounce Enable Control Register * --------------------------------------------------------------------------------------------------- * |Bits |Field |Descriptions * | :----: | :----: | :---- | * |[n] |DBENn |Port A-F Pin[n] Input Signal De-Bounce Enable Bit * | | |The DBEN[n] bit is used to enable the de-bounce function for each corresponding bit. * | | |If the input signal pulse width cannot be sampled by continuous two de-bounce sample cycle, the input signal transition is seen as the signal bounce and will not trigger the interrupt. * | | |The de-bounce clock source is controlled by DBCLKSRC (GPIO_DBCTL [4]), one de-bounce sample cycle period is controlled by DBCLKSEL (GPIO_DBCTL [3:0]). * | | |0 = Px.n de-bounce function Disabled. * | | |1 = Px.n de-bounce function Enabled. * | | |The de-bounce function is valid only for edge triggered interrupt. * | | |If the interrupt mode is level triggered, the de-bounce enable bit is ignored. * | | |Note: * | | |n=0~15 for port A/B/C/D. * | | |n=0~14 for port E. * | | |n=0~7 for port F. * @var GPIO_T::INTTYPE * Offset: 0x18/0x58/0x98/0xD8/0x118/0x158 Port A-F Interrupt Trigger Type Control * --------------------------------------------------------------------------------------------------- * |Bits |Field |Descriptions * | :----: | :----: | :---- | * |[n] |TYPEn |Port A-F Pin[n] Edge Or Level Detection Interrupt Trigger Type Control * | | |TYPE (Px_INTTYPE[n]) bit is used to control the triggered interrupt is by level trigger or by edge trigger. * | | |If the interrupt is by edge trigger, the trigger source can be controlled by de-bounce. * | | |If the interrupt is by level trigger, the input source is sampled by one HCLK clock and generates the interrupt. * | | |0 = Edge trigger interrupt. * | | |1 = Level trigger interrupt. * | | |If the pin is set as the level trigger interrupt, only one level can be set on the registers RHIEN (Px_INTEN[n+16])/FLIEN (Px_INTEN[n]). * | | |If both levels to trigger interrupt are set, the setting is ignored and no interrupt will occur. * | | |The de-bounce function is valid only for edge triggered interrupt. * | | |If the interrupt mode is level triggered, the de-bounce enable bit is ignored. * | | |Note: * | | |n=0~15 for port A/B/C/D. * | | |n=0~14 for port E. * | | |n=0~7 for port F. * @var GPIO_T::INTEN * Offset: 0x1C/0x5C/0x9C/0xDC/0x11C/0x15C Port A-F Interrupt Enable Control Register * --------------------------------------------------------------------------------------------------- * |Bits |Field |Descriptions * | :----: | :----: | :---- | * |[n] |FLIENn |Port A-F Pin[n] Falling Edge or Low Level Interrupt Trigger Type Enable Bit * | | |The FLIEN (Px_INTEN[n]) bit is used to enable the interrupt for each of the corresponding input Px.n pin. * | | |Set bit to 1 also enable the pin wake-up function. * | | |When setting the FLIEN (Px_INTEN[n]) bit to 1 : * | | |If the interrupt is level trigger (TYPE (Px_INTTYPE[n]) bit is set to 1), the input Px.n pin will generate the interrupt while this pin state is at low level. * | | |If the interrupt is edge trigger(TYPE (Px_INTTYPE[n]) bit is set to 0), the input Px.n pin will generate the interrupt while this pin state changed from high to low. * | | |0 = Px.n level low or high to low interrupt Disabled. * | | |1 = Px.n level low or high to low interrupt Enabled. * | | |Note: * | | |n=0~15 for port A/B/C/D. * | | |n=0~14 for port E. * | | |n=0~7 for port F. * @var GPIO_T::INTSRC * Offset: 0x20/0x60/0xA0/0xE0/0x120/0x160 Port A-F Interrupt Source Flag * --------------------------------------------------------------------------------------------------- * |Bits |Field |Descriptions * | :----: | :----: | :---- | * |[n] |INTSRCn |Port A-F Pin[n] Interrupt Source Flag * | | |Write Operation : * | | |0 = No action. * | | |1 = Clear the corresponding pending interrupt. * | | |Read Operation : * | | |0 = No interrupt at Px.n. * | | |1 = Px.n generates an interrupt. * | | |Note: * | | |n=0~15 for port A/B/C/D. * | | |n=0~14 for port E. * | | |n=0~7 for port F. * @var GPIO_T::SMTEN * Offset: 0x24/0x64/0xA4/0xE4/0x124/0x164 Port A-F Input Schmitt Trigger Enable Register * --------------------------------------------------------------------------------------------------- * |Bits |Field |Descriptions * | :----: | :----: | :---- | * |[n] |SMTENn |Port A-F Pin[n] Input Schmitt Trigger Enable Bit * | | |0 = Px.n input Schmitt trigger function Disabled. * | | |1 = Px.n input Schmitt trigger function Enabled. * | | |Note: * | | |n=0~15 for port A/B/C/D. * | | |n=0~14 for port E. * | | |n=0~7 for port F. * @var GPIO_T::SLEWCTL * Offset: 0x28/0x68/0xA8/0xE8/0x128/0x168 Port A-F High Slew Rate Control Register * --------------------------------------------------------------------------------------------------- * |Bits |Field |Descriptions * | :----: | :----: | :---- | * |[n] |HSRENn |Port A-F Pin[n] High Slew Rate Control * | | |0 = Px.n output with basic slew rate. * | | |1 = Px.n output with higher slew rate. * | | |Note: * | | |n=0~15 for port A/B/C/D. * | | |n=0~14 for port E. * | | |n=0~7 for port F. * @var GPIO_T::DRVCTL * Offset: 0x2C Port E High Drive Strength Control Register * --------------------------------------------------------------------------------------------------- * |Bits |Field |Descriptions * | :----: | :----: | :---- | * |[n] |HDRVENn |Port E Pin[n] Driving Strength Control * | | |0 = Px.n output with basic driving strength. * | | |1 = Px.n output with high driving strength. * | | |Note: * | | |n=8,9..13 for port E. */ __IO uint32_t MODE; /* Offset: 0x00/0x40/0x80/0xC0/0x100/0x140 Port A-F I/O Mode Control */ __IO uint32_t DINOFF; /* Offset: 0x04/0x44/0x84/0xC4/0x104/0x144 Port A-F Digital Input Path Disable Control */ __IO uint32_t DOUT; /* Offset: 0x08/0x48/0x88/0xC8/0x108/0x148 Port A-F Data Output Value */ __IO uint32_t DATMSK; /* Offset: 0x0C/0x4C/0x8C/0xCC/0x10C/0x14C Port A-F Data Output Write Mask */ __I uint32_t PIN; /* Offset: 0x10/0x50/0x90/0xD0/0x110/0x150 Port A-F Pin Value */ __IO uint32_t DBEN; /* Offset: 0x14/0x54/0x94/0xD4/0x114/0x154 Port A-F De-Bounce Enable Control Register */ __IO uint32_t INTTYPE; /* Offset: 0x18/0x58/0x98/0xD8/0x118/0x158 Port A-F Interrupt Trigger Type Control */ __IO uint32_t INTEN; /* Offset: 0x1C/0x5C/0x9C/0xDC/0x11C/0x15C Port A-F Interrupt Enable Control Register */ __IO uint32_t INTSRC; /* Offset: 0x20/0x60/0xA0/0xE0/0x120/0x160 Port A-F Interrupt Source Flag */ __IO uint32_t SMTEN; /* Offset: 0x24/0x64/0xA4/0xE4/0x124/0x164 Port A-F Input Schmitt Trigger Enable Register */ __IO uint32_t SLEWCTL; /* Offset: 0x28/0x68/0xA8/0xE8/0x128/0x168 Port A-F High Slew Rate Control Register */ __IO uint32_t DRVCTL; /* Offset: 0x12C Port E High Drive Strength Control Register */ } GPIO_T; typedef struct { /** * @var GPIO_DBCTL_T::DBCTL * Offset: 0x440 Interrupt De-bounce Control Register * --------------------------------------------------------------------------------------------------- * |Bits |Field |Descriptions * | :----: | :----: | :---- | * |[3:0] |DBCLKSEL |De-Bounce Sampling Cycle Selection * | | |0000 = Sample interrupt input once per 1 clocks. * | | |0001 = Sample interrupt input once per 2 clocks. * | | |0010 = Sample interrupt input once per 4 clocks. * | | |0011 = Sample interrupt input once per 8 clocks. * | | |0100 = Sample interrupt input once per 16 clocks. * | | |0101 = Sample interrupt input once per 32 clocks. * | | |0110 = Sample interrupt input once per 64 clocks. * | | |0111 = Sample interrupt input once per 128 clocks. * | | |1000 = Sample interrupt input once per 256 clocks. * | | |1001 = Sample interrupt input once per 2*256 clocks. * | | |1010 = Sample interrupt input once per 4*256 clocks. * | | |1011 = Sample interrupt input once per 8*256 clocks. * | | |1100 = Sample interrupt input once per 16*256 clocks. * | | |1101 = Sample interrupt input once per 32*256 clocks. * | | |1110 = Sample interrupt input once per 64*256 clocks. * | | |1111 = Sample interrupt input once per 128*256 clocks. * |[4] |DBCLKSRC |De-Bounce Counter Clock Source Selection * | | |0 = De-bounce counter clock source is the HCLK. * | | |1 = De-bounce counter clock source is the internal 10 kHz internal low speed oscillator. * |[5] |ICLKON |Interrupt Clock On Mode * | | |0 = Edge detection circuit is active only if I/O pin corresponding RHIEN (Px_INTEN[n+16])/FLIEN (Px_INTEN[n]) bit is set to 1. * | | |1 = All I/O pins edge detection circuit is always active after reset. * | | |Note: It is recommended to disable this bit to save system power if no special application concern. */ __IO uint32_t DBCTL; /* Offset: 0x440 Interrupt De-bounce Control Register */ } GPIO_DBCTL_T; /** @addtogroup GPIO_CONST GPIO Bit Field Definition Constant Definitions for GPIO Controller @{ */ #define GPIO_MODE_MODE0_Pos (0) /*!< GPIO_T::MODE: MODE0 Position */ #define GPIO_MODE_MODE0_Msk (0x3ul << GPIO_MODE_MODE0_Pos) /*!< GPIO_T::MODE: MODE0 Mask */ #define GPIO_MODE_MODE1_Pos (2) /*!< GPIO_T::MODE: MODE1 Position */ #define GPIO_MODE_MODE1_Msk (0x3ul << GPIO_MODE_MODE1_Pos) /*!< GPIO_T::MODE: MODE1 Mask */ #define GPIO_MODE_MODE2_Pos (4) /*!< GPIO_T::MODE: MODE2 Position */ #define GPIO_MODE_MODE2_Msk (0x3ul << GPIO_MODE_MODE2_Pos) /*!< GPIO_T::MODE: MODE2 Mask */ #define GPIO_MODE_MODE3_Pos (6) /*!< GPIO_T::MODE: MODE3 Position */ #define GPIO_MODE_MODE3_Msk (0x3ul << GPIO_MODE_MODE3_Pos) /*!< GPIO_T::MODE: MODE3 Mask */ #define GPIO_MODE_MODE4_Pos (8) /*!< GPIO_T::MODE: MODE4 Position */ #define GPIO_MODE_MODE4_Msk (0x3ul << GPIO_MODE_MODE4_Pos) /*!< GPIO_T::MODE: MODE4 Mask */ #define GPIO_MODE_MODE5_Pos (10) /*!< GPIO_T::MODE: MODE5 Position */ #define GPIO_MODE_MODE5_Msk (0x3ul << GPIO_MODE_MODE5_Pos) /*!< GPIO_T::MODE: MODE5 Mask */ #define GPIO_MODE_MODE6_Pos (12) /*!< GPIO_T::MODE: MODE6 Position */ #define GPIO_MODE_MODE6_Msk (0x3ul << GPIO_MODE_MODE6_Pos) /*!< GPIO_T::MODE: MODE6 Mask */ #define GPIO_MODE_MODE7_Pos (14) /*!< GPIO_T::MODE: MODE7 Position */ #define GPIO_MODE_MODE7_Msk (0x3ul << GPIO_MODE_MODE7_Pos) /*!< GPIO_T::MODE: MODE7 Mask */ #define GPIO_MODE_MODE8_Pos (16) /*!< GPIO_T::MODE: MODE8 Position */ #define GPIO_MODE_MODE8_Msk (0x3ul << GPIO_MODE_MODE8_Pos) /*!< GPIO_T::MODE: MODE8 Mask */ #define GPIO_MODE_MODE9_Pos (18) /*!< GPIO_T::MODE: MODE9 Position */ #define GPIO_MODE_MODE9_Msk (0x3ul << GPIO_MODE_MODE9_Pos) /*!< GPIO_T::MODE: MODE9 Mask */ #define GPIO_MODE_MODE10_Pos (20) /*!< GPIO_T::MODE: MODE10 Position */ #define GPIO_MODE_MODE10_Msk (0x3ul << GPIO_MODE_MODE10_Pos) /*!< GPIO_T::MODE: MODE10 Mask */ #define GPIO_MODE_MODE11_Pos (22) /*!< GPIO_T::MODE: MODE11 Position */ #define GPIO_MODE_MODE11_Msk (0x3ul << GPIO_MODE_MODE11_Pos) /*!< GPIO_T::MODE: MODE11 Mask */ #define GPIO_MODE_MODE12_Pos (24) /*!< GPIO_T::MODE: MODE12 Position */ #define GPIO_MODE_MODE12_Msk (0x3ul << GPIO_MODE_MODE12_Pos) /*!< GPIO_T::MODE: MODE12 Mask */ #define GPIO_MODE_MODE13_Pos (26) /*!< GPIO_T::MODE: MODE13 Position */ #define GPIO_MODE_MODE13_Msk (0x3ul << GPIO_MODE_MODE13_Pos) /*!< GPIO_T::MODE: MODE13 Mask */ #define GPIO_MODE_MODE14_Pos (28) /*!< GPIO_T::MODE: MODE14 Position */ #define GPIO_MODE_MODE14_Msk (0x3ul << GPIO_MODE_MODE14_Pos) /*!< GPIO_T::MODE: MODE14 Mask */ #define GPIO_MODE_MODE15_Pos (30) /*!< GPIO_T::MODE: MODE15 Position */ #define GPIO_MODE_MODE15_Msk (0x3ul << GPIO_MODE_MODE15_Pos) /*!< GPIO_T::MODE: MODE15 Mask */ #define GPIO_DINOFF_DINOFF0_Pos (16) /*!< GPIO_T::DINOFF: DINOFF0 Position */ #define GPIO_DINOFF_DINOFF0_Msk (0x1ul << GPIO_DINOFF_DINOFF0_Pos) /*!< GPIO_T::DINOFF: DINOFF0 Mask */ #define GPIO_DINOFF_DINOFF1_Pos (17) /*!< GPIO_T::DINOFF: DINOFF1 Position */ #define GPIO_DINOFF_DINOFF1_Msk (0x1ul << GPIO_DINOFF_DINOFF1_Pos) /*!< GPIO_T::DINOFF: DINOFF1 Mask */ #define GPIO_DINOFF_DINOFF2_Pos (18) /*!< GPIO_T::DINOFF: DINOFF2 Position */ #define GPIO_DINOFF_DINOFF2_Msk (0x1ul << GPIO_DINOFF_DINOFF2_Pos) /*!< GPIO_T::DINOFF: DINOFF2 Mask */ #define GPIO_DINOFF_DINOFF3_Pos (19) /*!< GPIO_T::DINOFF: DINOFF3 Position */ #define GPIO_DINOFF_DINOFF3_Msk (0x1ul << GPIO_DINOFF_DINOFF3_Pos) /*!< GPIO_T::DINOFF: DINOFF3 Mask */ #define GPIO_DINOFF_DINOFF4_Pos (20) /*!< GPIO_T::DINOFF: DINOFF4 Position */ #define GPIO_DINOFF_DINOFF4_Msk (0x1ul << GPIO_DINOFF_DINOFF4_Pos) /*!< GPIO_T::DINOFF: DINOFF4 Mask */ #define GPIO_DINOFF_DINOFF5_Pos (21) /*!< GPIO_T::DINOFF: DINOFF5 Position */ #define GPIO_DINOFF_DINOFF5_Msk (0x1ul << GPIO_DINOFF_DINOFF5_Pos) /*!< GPIO_T::DINOFF: DINOFF5 Mask */ #define GPIO_DINOFF_DINOFF6_Pos (22) /*!< GPIO_T::DINOFF: DINOFF6 Position */ #define GPIO_DINOFF_DINOFF6_Msk (0x1ul << GPIO_DINOFF_DINOFF6_Pos) /*!< GPIO_T::DINOFF: DINOFF6 Mask */ #define GPIO_DINOFF_DINOFF7_Pos (23) /*!< GPIO_T::DINOFF: DINOFF7 Position */ #define GPIO_DINOFF_DINOFF7_Msk (0x1ul << GPIO_DINOFF_DINOFF7_Pos) /*!< GPIO_T::DINOFF: DINOFF7 Mask */ #define GPIO_DINOFF_DINOFF8_Pos (24) /*!< GPIO_T::DINOFF: DINOFF8 Position */ #define GPIO_DINOFF_DINOFF8_Msk (0x1ul << GPIO_DINOFF_DINOFF8_Pos) /*!< GPIO_T::DINOFF: DINOFF8 Mask */ #define GPIO_DINOFF_DINOFF9_Pos (25) /*!< GPIO_T::DINOFF: DINOFF9 Position */ #define GPIO_DINOFF_DINOFF9_Msk (0x1ul << GPIO_DINOFF_DINOFF9_Pos) /*!< GPIO_T::DINOFF: DINOFF9 Mask */ #define GPIO_DINOFF_DINOFF10_Pos (26) /*!< GPIO_T::DINOFF: DINOFF10 Position */ #define GPIO_DINOFF_DINOFF10_Msk (0x1ul << GPIO_DINOFF_DINOFF10_Pos) /*!< GPIO_T::DINOFF: DINOFF10 Mask */ #define GPIO_DINOFF_DINOFF11_Pos (27) /*!< GPIO_T::DINOFF: DINOFF11 Position */ #define GPIO_DINOFF_DINOFF11_Msk (0x1ul << GPIO_DINOFF_DINOFF11_Pos) /*!< GPIO_T::DINOFF: DINOFF11 Mask */ #define GPIO_DINOFF_DINOFF12_Pos (28) /*!< GPIO_T::DINOFF: DINOFF12 Position */ #define GPIO_DINOFF_DINOFF12_Msk (0x1ul << GPIO_DINOFF_DINOFF12_Pos) /*!< GPIO_T::DINOFF: DINOFF12 Mask */ #define GPIO_DINOFF_DINOFF13_Pos (29) /*!< GPIO_T::DINOFF: DINOFF13 Position */ #define GPIO_DINOFF_DINOFF13_Msk (0x1ul << GPIO_DINOFF_DINOFF13_Pos) /*!< GPIO_T::DINOFF: DINOFF13 Mask */ #define GPIO_DINOFF_DINOFF14_Pos (30) /*!< GPIO_T::DINOFF: DINOFF14 Position */ #define GPIO_DINOFF_DINOFF14_Msk (0x1ul << GPIO_DINOFF_DINOFF14_Pos) /*!< GPIO_T::DINOFF: DINOFF14 Mask */ #define GPIO_DINOFF_DINOFF15_Pos (31) /*!< GPIO_T::DINOFF: DINOFF15 Position */ #define GPIO_DINOFF_DINOFF15_Msk (0x1ul << GPIO_DINOFF_DINOFF15_Pos) /*!< GPIO_T::DINOFF: DINOFF15 Mask */ #define GPIO_DOUT_DOUT0_Pos (0) /*!< GPIO_T::DOUT: DOUT0 Position */ #define GPIO_DOUT_DOUT0_Msk (0x1ul << GPIO_DOUT_DOUT0_Pos) /*!< GPIO_T::DOUT: DOUT0 Mask */ #define GPIO_DOUT_DOUT1_Pos (1) /*!< GPIO_T::DOUT: DOUT1 Position */ #define GPIO_DOUT_DOUT1_Msk (0x1ul << GPIO_DOUT_DOUT1_Pos) /*!< GPIO_T::DOUT: DOUT1 Mask */ #define GPIO_DOUT_DOUT2_Pos (2) /*!< GPIO_T::DOUT: DOUT2 Position */ #define GPIO_DOUT_DOUT2_Msk (0x1ul << GPIO_DOUT_DOUT2_Pos) /*!< GPIO_T::DOUT: DOUT2 Mask */ #define GPIO_DOUT_DOUT3_Pos (3) /*!< GPIO_T::DOUT: DOUT3 Position */ #define GPIO_DOUT_DOUT3_Msk (0x1ul << GPIO_DOUT_DOUT3_Pos) /*!< GPIO_T::DOUT: DOUT3 Mask */ #define GPIO_DOUT_DOUT4_Pos (4) /*!< GPIO_T::DOUT: DOUT4 Position */ #define GPIO_DOUT_DOUT4_Msk (0x1ul << GPIO_DOUT_DOUT4_Pos) /*!< GPIO_T::DOUT: DOUT4 Mask */ #define GPIO_DOUT_DOUT5_Pos (5) /*!< GPIO_T::DOUT: DOUT5 Position */ #define GPIO_DOUT_DOUT5_Msk (0x1ul << GPIO_DOUT_DOUT5_Pos) /*!< GPIO_T::DOUT: DOUT5 Mask */ #define GPIO_DOUT_DOUT6_Pos (6) /*!< GPIO_T::DOUT: DOUT6 Position */ #define GPIO_DOUT_DOUT6_Msk (0x1ul << GPIO_DOUT_DOUT6_Pos) /*!< GPIO_T::DOUT: DOUT6 Mask */ #define GPIO_DOUT_DOUT7_Pos (7) /*!< GPIO_T::DOUT: DOUT7 Position */ #define GPIO_DOUT_DOUT7_Msk (0x1ul << GPIO_DOUT_DOUT7_Pos) /*!< GPIO_T::DOUT: DOUT7 Mask */ #define GPIO_DOUT_DOUT8_Pos (8) /*!< GPIO_T::DOUT: DOUT8 Position */ #define GPIO_DOUT_DOUT8_Msk (0x1ul << GPIO_DOUT_DOUT8_Pos) /*!< GPIO_T::DOUT: DOUT8 Mask */ #define GPIO_DOUT_DOUT9_Pos (9) /*!< GPIO_T::DOUT: DOUT9 Position */ #define GPIO_DOUT_DOUT9_Msk (0x1ul << GPIO_DOUT_DOUT9_Pos) /*!< GPIO_T::DOUT: DOUT9 Mask */ #define GPIO_DOUT_DOUT10_Pos (10) /*!< GPIO_T::DOUT: DOUT10 Position */ #define GPIO_DOUT_DOUT10_Msk (0x1ul << GPIO_DOUT_DOUT10_Pos) /*!< GPIO_T::DOUT: DOUT10 Mask */ #define GPIO_DOUT_DOUT11_Pos (11) /*!< GPIO_T::DOUT: DOUT11 Position */ #define GPIO_DOUT_DOUT11_Msk (0x1ul << GPIO_DOUT_DOUT11_Pos) /*!< GPIO_T::DOUT: DOUT11 Mask */ #define GPIO_DOUT_DOUT12_Pos (12) /*!< GPIO_T::DOUT: DOUT12 Position */ #define GPIO_DOUT_DOUT12_Msk (0x1ul << GPIO_DOUT_DOUT12_Pos) /*!< GPIO_T::DOUT: DOUT12 Mask */ #define GPIO_DOUT_DOUT13_Pos (13) /*!< GPIO_T::DOUT: DOUT13 Position */ #define GPIO_DOUT_DOUT13_Msk (0x1ul << GPIO_DOUT_DOUT13_Pos) /*!< GPIO_T::DOUT: DOUT13 Mask */ #define GPIO_DOUT_DOUT14_Pos (14) /*!< GPIO_T::DOUT: DOUT14 Position */ #define GPIO_DOUT_DOUT14_Msk (0x1ul << GPIO_DOUT_DOUT14_Pos) /*!< GPIO_T::DOUT: DOUT14 Mask */ #define GPIO_DOUT_DOUT15_Pos (15) /*!< GPIO_T::DOUT: DOUT15 Position */ #define GPIO_DOUT_DOUT15_Msk (0x1ul << GPIO_DOUT_DOUT15_Pos) /*!< GPIO_T::DOUT: DOUT15 Mask */ #define GPIO_DATMSK_DMASK0_Pos (0) /*!< GPIO_T::DATMSK: DMASK0 Position */ #define GPIO_DATMSK_DMASK0_Msk (0x1ul << GPIO_DATMSK_DMASK0_Pos) /*!< GPIO_T::DATMSK: DMASK0 Mask */ #define GPIO_DATMSK_DMASK1_Pos (1) /*!< GPIO_T::DATMSK: DMASK1 Position */ #define GPIO_DATMSK_DMASK1_Msk (0x1ul << GPIO_DATMSK_DMASK1_Pos) /*!< GPIO_T::DATMSK: DMASK1 Mask */ #define GPIO_DATMSK_DMASK2_Pos (2) /*!< GPIO_T::DATMSK: DMASK2 Position */ #define GPIO_DATMSK_DMASK2_Msk (0x1ul << GPIO_DATMSK_DMASK2_Pos) /*!< GPIO_T::DATMSK: DMASK2 Mask */ #define GPIO_DATMSK_DMASK3_Pos (3) /*!< GPIO_T::DATMSK: DMASK3 Position */ #define GPIO_DATMSK_DMASK3_Msk (0x1ul << GPIO_DATMSK_DMASK3_Pos) /*!< GPIO_T::DATMSK: DMASK3 Mask */ #define GPIO_DATMSK_DMASK4_Pos (4) /*!< GPIO_T::DATMSK: DMASK4 Position */ #define GPIO_DATMSK_DMASK4_Msk (0x1ul << GPIO_DATMSK_DMASK4_Pos) /*!< GPIO_T::DATMSK: DMASK4 Mask */ #define GPIO_DATMSK_DMASK5_Pos (5) /*!< GPIO_T::DATMSK: DMASK5 Position */ #define GPIO_DATMSK_DMASK5_Msk (0x1ul << GPIO_DATMSK_DMASK5_Pos) /*!< GPIO_T::DATMSK: DMASK5 Mask */ #define GPIO_DATMSK_DMASK6_Pos (6) /*!< GPIO_T::DATMSK: DMASK6 Position */ #define GPIO_DATMSK_DMASK6_Msk (0x1ul << GPIO_DATMSK_DMASK6_Pos) /*!< GPIO_T::DATMSK: DMASK6 Mask */ #define GPIO_DATMSK_DMASK7_Pos (7) /*!< GPIO_T::DATMSK: DMASK7 Position */ #define GPIO_DATMSK_DMASK7_Msk (0x1ul << GPIO_DATMSK_DMASK7_Pos) /*!< GPIO_T::DATMSK: DMASK7 Mask */ #define GPIO_DATMSK_DMASK8_Pos (8) /*!< GPIO_T::DATMSK: DMASK8 Position */ #define GPIO_DATMSK_DMASK8_Msk (0x1ul << GPIO_DATMSK_DMASK8_Pos) /*!< GPIO_T::DATMSK: DMASK8 Mask */ #define GPIO_DATMSK_DMASK9_Pos (9) /*!< GPIO_T::DATMSK: DMASK9 Position */ #define GPIO_DATMSK_DMASK9_Msk (0x1ul << GPIO_DATMSK_DMASK9_Pos) /*!< GPIO_T::DATMSK: DMASK9 Mask */ #define GPIO_DATMSK_DMASK10_Pos (10) /*!< GPIO_T::DATMSK: DMASK10 Position */ #define GPIO_DATMSK_DMASK10_Msk (0x1ul << GPIO_DATMSK_DMASK10_Pos) /*!< GPIO_T::DATMSK: DMASK10 Mask */ #define GPIO_DATMSK_DMASK11_Pos (11) /*!< GPIO_T::DATMSK: DMASK11 Position */ #define GPIO_DATMSK_DMASK11_Msk (0x1ul << GPIO_DATMSK_DMASK11_Pos) /*!< GPIO_T::DATMSK: DMASK11 Mask */ #define GPIO_DATMSK_DMASK12_Pos (12) /*!< GPIO_T::DATMSK: DMASK12 Position */ #define GPIO_DATMSK_DMASK12_Msk (0x1ul << GPIO_DATMSK_DMASK12_Pos) /*!< GPIO_T::DATMSK: DMASK12 Mask */ #define GPIO_DATMSK_DMASK13_Pos (13) /*!< GPIO_T::DATMSK: DMASK13 Position */ #define GPIO_DATMSK_DMASK13_Msk (0x1ul << GPIO_DATMSK_DMASK13_Pos) /*!< GPIO_T::DATMSK: DMASK13 Mask */ #define GPIO_DATMSK_DMASK14_Pos (14) /*!< GPIO_T::DATMSK: DMASK14 Position */ #define GPIO_DATMSK_DMASK14_Msk (0x1ul << GPIO_DATMSK_DMASK14_Pos) /*!< GPIO_T::DATMSK: DMASK14 Mask */ #define GPIO_DATMSK_DMASK15_Pos (15) /*!< GPIO_T::DATMSK: DMASK15 Position */ #define GPIO_DATMSK_DMASK15_Msk (0x1ul << GPIO_DATMSK_DMASK15_Pos) /*!< GPIO_T::DATMSK: DMASK15 Mask */ #define GPIO_PIN_PIN0_Pos (0) /*!< GPIO_T::PIN: PIN0 Position */ #define GPIO_PIN_PIN0_Msk (0x1ul << GPIO_PIN_PIN0_Pos) /*!< GPIO_T::PIN: PIN0 Mask */ #define GPIO_PIN_PIN1_Pos (1) /*!< GPIO_T::PIN: PIN1 Position */ #define GPIO_PIN_PIN1_Msk (0x1ul << GPIO_PIN_PIN1_Pos) /*!< GPIO_T::PIN: PIN1 Mask */ #define GPIO_PIN_PIN2_Pos (2) /*!< GPIO_T::PIN: PIN2 Position */ #define GPIO_PIN_PIN2_Msk (0x1ul << GPIO_PIN_PIN2_Pos) /*!< GPIO_T::PIN: PIN2 Mask */ #define GPIO_PIN_PIN3_Pos (3) /*!< GPIO_T::PIN: PIN3 Position */ #define GPIO_PIN_PIN3_Msk (0x1ul << GPIO_PIN_PIN3_Pos) /*!< GPIO_T::PIN: PIN3 Mask */ #define GPIO_PIN_PIN4_Pos (4) /*!< GPIO_T::PIN: PIN4 Position */ #define GPIO_PIN_PIN4_Msk (0x1ul << GPIO_PIN_PIN4_Pos) /*!< GPIO_T::PIN: PIN4 Mask */ #define GPIO_PIN_PIN5_Pos (5) /*!< GPIO_T::PIN: PIN5 Position */ #define GPIO_PIN_PIN5_Msk (0x1ul << GPIO_PIN_PIN5_Pos) /*!< GPIO_T::PIN: PIN5 Mask */ #define GPIO_PIN_PIN6_Pos (6) /*!< GPIO_T::PIN: PIN6 Position */ #define GPIO_PIN_PIN6_Msk (0x1ul << GPIO_PIN_PIN6_Pos) /*!< GPIO_T::PIN: PIN6 Mask */ #define GPIO_PIN_PIN7_Pos (7) /*!< GPIO_T::PIN: PIN7 Position */ #define GPIO_PIN_PIN7_Msk (0x1ul << GPIO_PIN_PIN7_Pos) /*!< GPIO_T::PIN: PIN7 Mask */ #define GPIO_PIN_PIN8_Pos (8) /*!< GPIO_T::PIN: PIN8 Position */ #define GPIO_PIN_PIN8_Msk (0x1ul << GPIO_PIN_PIN8_Pos) /*!< GPIO_T::PIN: PIN8 Mask */ #define GPIO_PIN_PIN9_Pos (9) /*!< GPIO_T::PIN: PIN9 Position */ #define GPIO_PIN_PIN9_Msk (0x1ul << GPIO_PIN_PIN9_Pos) /*!< GPIO_T::PIN: PIN9 Mask */ #define GPIO_PIN_PIN10_Pos (10) /*!< GPIO_T::PIN: PIN10 Position */ #define GPIO_PIN_PIN10_Msk (0x1ul << GPIO_PIN_PIN10_Pos) /*!< GPIO_T::PIN: PIN10 Mask */ #define GPIO_PIN_PIN11_Pos (11) /*!< GPIO_T::PIN: PIN11 Position */ #define GPIO_PIN_PIN11_Msk (0x1ul << GPIO_PIN_PIN11_Pos) /*!< GPIO_T::PIN: PIN11 Mask */ #define GPIO_PIN_PIN12_Pos (12) /*!< GPIO_T::PIN: PIN12 Position */ #define GPIO_PIN_PIN12_Msk (0x1ul << GPIO_PIN_PIN12_Pos) /*!< GPIO_T::PIN: PIN12 Mask */ #define GPIO_PIN_PIN13_Pos (13) /*!< GPIO_T::PIN: PIN13 Position */ #define GPIO_PIN_PIN13_Msk (0x1ul << GPIO_PIN_PIN13_Pos) /*!< GPIO_T::PIN: PIN13 Mask */ #define GPIO_PIN_PIN14_Pos (14) /*!< GPIO_T::PIN: PIN14 Position */ #define GPIO_PIN_PIN14_Msk (0x1ul << GPIO_PIN_PIN14_Pos) /*!< GPIO_T::PIN: PIN14 Mask */ #define GPIO_PIN_PIN15_Pos (15) /*!< GPIO_T::PIN: PIN15 Position */ #define GPIO_PIN_PIN15_Msk (0x1ul << GPIO_PIN_PIN15_Pos) /*!< GPIO_T::PIN: PIN15 Mask */ #define GPIO_DBEN_DBEN0_Pos (0) /*!< GPIO_T::DBEN: DBEN0 Position */ #define GPIO_DBEN_DBEN0_Msk (0x1ul << GPIO_DBEN_DBEN0_Pos) /*!< GPIO_T::DBEN: DBEN0 Mask */ #define GPIO_DBEN_DBEN1_Pos (1) /*!< GPIO_T::DBEN: DBEN1 Position */ #define GPIO_DBEN_DBEN1_Msk (0x1ul << GPIO_DBEN_DBEN1_Pos) /*!< GPIO_T::DBEN: DBEN1 Mask */ #define GPIO_DBEN_DBEN2_Pos (2) /*!< GPIO_T::DBEN: DBEN2 Position */ #define GPIO_DBEN_DBEN2_Msk (0x1ul << GPIO_DBEN_DBEN2_Pos) /*!< GPIO_T::DBEN: DBEN2 Mask */ #define GPIO_DBEN_DBEN3_Pos (3) /*!< GPIO_T::DBEN: DBEN3 Position */ #define GPIO_DBEN_DBEN3_Msk (0x1ul << GPIO_DBEN_DBEN3_Pos) /*!< GPIO_T::DBEN: DBEN3 Mask */ #define GPIO_DBEN_DBEN4_Pos (4) /*!< GPIO_T::DBEN: DBEN4 Position */ #define GPIO_DBEN_DBEN4_Msk (0x1ul << GPIO_DBEN_DBEN4_Pos) /*!< GPIO_T::DBEN: DBEN4 Mask */ #define GPIO_DBEN_DBEN5_Pos (5) /*!< GPIO_T::DBEN: DBEN5 Position */ #define GPIO_DBEN_DBEN5_Msk (0x1ul << GPIO_DBEN_DBEN5_Pos) /*!< GPIO_T::DBEN: DBEN5 Mask */ #define GPIO_DBEN_DBEN6_Pos (6) /*!< GPIO_T::DBEN: DBEN6 Position */ #define GPIO_DBEN_DBEN6_Msk (0x1ul << GPIO_DBEN_DBEN6_Pos) /*!< GPIO_T::DBEN: DBEN6 Mask */ #define GPIO_DBEN_DBEN7_Pos (7) /*!< GPIO_T::DBEN: DBEN7 Position */ #define GPIO_DBEN_DBEN7_Msk (0x1ul << GPIO_DBEN_DBEN7_Pos) /*!< GPIO_T::DBEN: DBEN7 Mask */ #define GPIO_DBEN_DBEN8_Pos (8) /*!< GPIO_T::DBEN: DBEN8 Position */ #define GPIO_DBEN_DBEN8_Msk (0x1ul << GPIO_DBEN_DBEN8_Pos) /*!< GPIO_T::DBEN: DBEN8 Mask */ #define GPIO_DBEN_DBEN9_Pos (9) /*!< GPIO_T::DBEN: DBEN9 Position */ #define GPIO_DBEN_DBEN9_Msk (0x1ul << GPIO_DBEN_DBEN9_Pos) /*!< GPIO_T::DBEN: DBEN9 Mask */ #define GPIO_DBEN_DBEN10_Pos (10) /*!< GPIO_T::DBEN: DBEN10 Position */ #define GPIO_DBEN_DBEN10_Msk (0x1ul << GPIO_DBEN_DBEN10_Pos) /*!< GPIO_T::DBEN: DBEN10 Mask */ #define GPIO_DBEN_DBEN11_Pos (11) /*!< GPIO_T::DBEN: DBEN11 Position */ #define GPIO_DBEN_DBEN11_Msk (0x1ul << GPIO_DBEN_DBEN11_Pos) /*!< GPIO_T::DBEN: DBEN11 Mask */ #define GPIO_DBEN_DBEN12_Pos (12) /*!< GPIO_T::DBEN: DBEN12 Position */ #define GPIO_DBEN_DBEN12_Msk (0x1ul << GPIO_DBEN_DBEN12_Pos) /*!< GPIO_T::DBEN: DBEN12 Mask */ #define GPIO_DBEN_DBEN13_Pos (13) /*!< GPIO_T::DBEN: DBEN13 Position */ #define GPIO_DBEN_DBEN13_Msk (0x1ul << GPIO_DBEN_DBEN13_Pos) /*!< GPIO_T::DBEN: DBEN13 Mask */ #define GPIO_DBEN_DBEN14_Pos (14) /*!< GPIO_T::DBEN: DBEN14 Position */ #define GPIO_DBEN_DBEN14_Msk (0x1ul << GPIO_DBEN_DBEN14_Pos) /*!< GPIO_T::DBEN: DBEN14 Mask */ #define GPIO_DBEN_DBEN15_Pos (15) /*!< GPIO_T::DBEN: DBEN15 Position */ #define GPIO_DBEN_DBEN15_Msk (0x1ul << GPIO_DBEN_DBEN15_Pos) /*!< GPIO_T::DBEN: DBEN15 Mask */ #define GPIO_INTTYPE_TYPE0_Pos (0) /*!< GPIO_T::INTTYPE: TYPE0 Position */ #define GPIO_INTTYPE_TYPE0_Msk (0x1ul << GPIO_INTTYPE_TYPE0_Pos) /*!< GPIO_T::INTTYPE: TYPE0 Mask */ #define GPIO_INTTYPE_TYPE1_Pos (1) /*!< GPIO_T::INTTYPE: TYPE1 Position */ #define GPIO_INTTYPE_TYPE1_Msk (0x1ul << GPIO_INTTYPE_TYPE1_Pos) /*!< GPIO_T::INTTYPE: TYPE1 Mask */ #define GPIO_INTTYPE_TYPE2_Pos (2) /*!< GPIO_T::INTTYPE: TYPE2 Position */ #define GPIO_INTTYPE_TYPE2_Msk (0x1ul << GPIO_INTTYPE_TYPE2_Pos) /*!< GPIO_T::INTTYPE: TYPE2 Mask */ #define GPIO_INTTYPE_TYPE3_Pos (3) /*!< GPIO_T::INTTYPE: TYPE3 Position */ #define GPIO_INTTYPE_TYPE3_Msk (0x1ul << GPIO_INTTYPE_TYPE3_Pos) /*!< GPIO_T::INTTYPE: TYPE3 Mask */ #define GPIO_INTTYPE_TYPE4_Pos (4) /*!< GPIO_T::INTTYPE: TYPE4 Position */ #define GPIO_INTTYPE_TYPE4_Msk (0x1ul << GPIO_INTTYPE_TYPE4_Pos) /*!< GPIO_T::INTTYPE: TYPE4 Mask */ #define GPIO_INTTYPE_TYPE5_Pos (5) /*!< GPIO_T::INTTYPE: TYPE5 Position */ #define GPIO_INTTYPE_TYPE5_Msk (0x1ul << GPIO_INTTYPE_TYPE5_Pos) /*!< GPIO_T::INTTYPE: TYPE5 Mask */ #define GPIO_INTTYPE_TYPE6_Pos (6) /*!< GPIO_T::INTTYPE: TYPE6 Position */ #define GPIO_INTTYPE_TYPE6_Msk (0x1ul << GPIO_INTTYPE_TYPE6_Pos) /*!< GPIO_T::INTTYPE: TYPE6 Mask */ #define GPIO_INTTYPE_TYPE7_Pos (7) /*!< GPIO_T::INTTYPE: TYPE7 Position */ #define GPIO_INTTYPE_TYPE7_Msk (0x1ul << GPIO_INTTYPE_TYPE7_Pos) /*!< GPIO_T::INTTYPE: TYPE7 Mask */ #define GPIO_INTTYPE_TYPE8_Pos (8) /*!< GPIO_T::INTTYPE: TYPE8 Position */ #define GPIO_INTTYPE_TYPE8_Msk (0x1ul << GPIO_INTTYPE_TYPE8_Pos) /*!< GPIO_T::INTTYPE: TYPE8 Mask */ #define GPIO_INTTYPE_TYPE9_Pos (9) /*!< GPIO_T::INTTYPE: TYPE9 Position */ #define GPIO_INTTYPE_TYPE9_Msk (0x1ul << GPIO_INTTYPE_TYPE9_Pos) /*!< GPIO_T::INTTYPE: TYPE9 Mask */ #define GPIO_INTTYPE_TYPE10_Pos (10) /*!< GPIO_T::INTTYPE: TYPE10 Position */ #define GPIO_INTTYPE_TYPE10_Msk (0x1ul << GPIO_INTTYPE_TYPE10_Pos) /*!< GPIO_T::INTTYPE: TYPE10 Mask */ #define GPIO_INTTYPE_TYPE11_Pos (11) /*!< GPIO_T::INTTYPE: TYPE11 Position */ #define GPIO_INTTYPE_TYPE11_Msk (0x1ul << GPIO_INTTYPE_TYPE11_Pos) /*!< GPIO_T::INTTYPE: TYPE11 Mask */ #define GPIO_INTTYPE_TYPE12_Pos (12) /*!< GPIO_T::INTTYPE: TYPE12 Position */ #define GPIO_INTTYPE_TYPE12_Msk (0x1ul << GPIO_INTTYPE_TYPE12_Pos) /*!< GPIO_T::INTTYPE: TYPE12 Mask */ #define GPIO_INTTYPE_TYPE13_Pos (13) /*!< GPIO_T::INTTYPE: TYPE13 Position */ #define GPIO_INTTYPE_TYPE13_Msk (0x1ul << GPIO_INTTYPE_TYPE13_Pos) /*!< GPIO_T::INTTYPE: TYPE13 Mask */ #define GPIO_INTTYPE_TYPE14_Pos (14) /*!< GPIO_T::INTTYPE: TYPE14 Position */ #define GPIO_INTTYPE_TYPE14_Msk (0x1ul << GPIO_INTTYPE_TYPE14_Pos) /*!< GPIO_T::INTTYPE: TYPE14 Mask */ #define GPIO_INTTYPE_TYPE15_Pos (15) /*!< GPIO_T::INTTYPE: TYPE15 Position */ #define GPIO_INTTYPE_TYPE15_Msk (0x1ul << GPIO_INTTYPE_TYPE15_Pos) /*!< GPIO_T::INTTYPE: TYPE15 Mask */ #define GPIO_INTEN_FLIEN0_Pos (0) /*!< GPIO_T::INTEN: FLIEN0 Position */ #define GPIO_INTEN_FLIEN0_Msk (0x1ul << GPIO_INTEN_FLIEN0_Pos) /*!< GPIO_T::INTEN: FLIEN0 Mask */ #define GPIO_INTEN_FLIEN1_Pos (1) /*!< GPIO_T::INTEN: FLIEN1 Position */ #define GPIO_INTEN_FLIEN1_Msk (0x1ul << GPIO_INTEN_FLIEN1_Pos) /*!< GPIO_T::INTEN: FLIEN1 Mask */ #define GPIO_INTEN_FLIEN2_Pos (2) /*!< GPIO_T::INTEN: FLIEN2 Position */ #define GPIO_INTEN_FLIEN2_Msk (0x1ul << GPIO_INTEN_FLIEN2_Pos) /*!< GPIO_T::INTEN: FLIEN2 Mask */ #define GPIO_INTEN_FLIEN3_Pos (3) /*!< GPIO_T::INTEN: FLIEN3 Position */ #define GPIO_INTEN_FLIEN3_Msk (0x1ul << GPIO_INTEN_FLIEN3_Pos) /*!< GPIO_T::INTEN: FLIEN3 Mask */ #define GPIO_INTEN_FLIEN4_Pos (4) /*!< GPIO_T::INTEN: FLIEN4 Position */ #define GPIO_INTEN_FLIEN4_Msk (0x1ul << GPIO_INTEN_FLIEN4_Pos) /*!< GPIO_T::INTEN: FLIEN4 Mask */ #define GPIO_INTEN_FLIEN5_Pos (5) /*!< GPIO_T::INTEN: FLIEN5 Position */ #define GPIO_INTEN_FLIEN5_Msk (0x1ul << GPIO_INTEN_FLIEN5_Pos) /*!< GPIO_T::INTEN: FLIEN5 Mask */ #define GPIO_INTEN_FLIEN6_Pos (6) /*!< GPIO_T::INTEN: FLIEN6 Position */ #define GPIO_INTEN_FLIEN6_Msk (0x1ul << GPIO_INTEN_FLIEN6_Pos) /*!< GPIO_T::INTEN: FLIEN6 Mask */ #define GPIO_INTEN_FLIEN7_Pos (7) /*!< GPIO_T::INTEN: FLIEN7 Position */ #define GPIO_INTEN_FLIEN7_Msk (0x1ul << GPIO_INTEN_FLIEN7_Pos) /*!< GPIO_T::INTEN: FLIEN7 Mask */ #define GPIO_INTEN_FLIEN8_Pos (8) /*!< GPIO_T::INTEN: FLIEN8 Position */ #define GPIO_INTEN_FLIEN8_Msk (0x1ul << GPIO_INTEN_FLIEN8_Pos) /*!< GPIO_T::INTEN: FLIEN8 Mask */ #define GPIO_INTEN_FLIEN9_Pos (9) /*!< GPIO_T::INTEN: FLIEN9 Position */ #define GPIO_INTEN_FLIEN9_Msk (0x1ul << GPIO_INTEN_FLIEN9_Pos) /*!< GPIO_T::INTEN: FLIEN9 Mask */ #define GPIO_INTEN_FLIEN10_Pos (10) /*!< GPIO_T::INTEN: FLIEN10 Position */ #define GPIO_INTEN_FLIEN10_Msk (0x1ul << GPIO_INTEN_FLIEN10_Pos) /*!< GPIO_T::INTEN: FLIEN10 Mask */ #define GPIO_INTEN_FLIEN11_Pos (11) /*!< GPIO_T::INTEN: FLIEN11 Position */ #define GPIO_INTEN_FLIEN11_Msk (0x1ul << GPIO_INTEN_FLIEN11_Pos) /*!< GPIO_T::INTEN: FLIEN11 Mask */ #define GPIO_INTEN_FLIEN12_Pos (12) /*!< GPIO_T::INTEN: FLIEN12 Position */ #define GPIO_INTEN_FLIEN12_Msk (0x1ul << GPIO_INTEN_FLIEN12_Pos) /*!< GPIO_T::INTEN: FLIEN12 Mask */ #define GPIO_INTEN_FLIEN13_Pos (13) /*!< GPIO_T::INTEN: FLIEN13 Position */ #define GPIO_INTEN_FLIEN13_Msk (0x1ul << GPIO_INTEN_FLIEN13_Pos) /*!< GPIO_T::INTEN: FLIEN13 Mask */ #define GPIO_INTEN_FLIEN14_Pos (14) /*!< GPIO_T::INTEN: FLIEN14 Position */ #define GPIO_INTEN_FLIEN14_Msk (0x1ul << GPIO_INTEN_FLIEN14_Pos) /*!< GPIO_T::INTEN: FLIEN14 Mask */ #define GPIO_INTEN_FLIEN15_Pos (15) /*!< GPIO_T::INTEN: FLIEN15 Position */ #define GPIO_INTEN_FLIEN15_Msk (0x1ul << GPIO_INTEN_FLIEN15_Pos) /*!< GPIO_T::INTEN: FLIEN15 Mask */ #define GPIO_INTEN_RHIEN0_Pos (16) /*!< GPIO_T::INTEN: RHIEN0 Position */ #define GPIO_INTEN_RHIEN0_Msk (0x1ul << GPIO_INTEN_RHIEN0_Pos) /*!< GPIO_T::INTEN: RHIEN0 Mask */ #define GPIO_INTEN_RHIEN1_Pos (17) /*!< GPIO_T::INTEN: RHIEN1 Position */ #define GPIO_INTEN_RHIEN1_Msk (0x1ul << GPIO_INTEN_RHIEN1_Pos) /*!< GPIO_T::INTEN: RHIEN1 Mask */ #define GPIO_INTEN_RHIEN2_Pos (18) /*!< GPIO_T::INTEN: RHIEN2 Position */ #define GPIO_INTEN_RHIEN2_Msk (0x1ul << GPIO_INTEN_RHIEN2_Pos) /*!< GPIO_T::INTEN: RHIEN2 Mask */ #define GPIO_INTEN_RHIEN3_Pos (19) /*!< GPIO_T::INTEN: RHIEN3 Position */ #define GPIO_INTEN_RHIEN3_Msk (0x1ul << GPIO_INTEN_RHIEN3_Pos) /*!< GPIO_T::INTEN: RHIEN3 Mask */ #define GPIO_INTEN_RHIEN4_Pos (20) /*!< GPIO_T::INTEN: RHIEN4 Position */ #define GPIO_INTEN_RHIEN4_Msk (0x1ul << GPIO_INTEN_RHIEN4_Pos) /*!< GPIO_T::INTEN: RHIEN4 Mask */ #define GPIO_INTEN_RHIEN5_Pos (21) /*!< GPIO_T::INTEN: RHIEN5 Position */ #define GPIO_INTEN_RHIEN5_Msk (0x1ul << GPIO_INTEN_RHIEN5_Pos) /*!< GPIO_T::INTEN: RHIEN5 Mask */ #define GPIO_INTEN_RHIEN6_Pos (22) /*!< GPIO_T::INTEN: RHIEN6 Position */ #define GPIO_INTEN_RHIEN6_Msk (0x1ul << GPIO_INTEN_RHIEN6_Pos) /*!< GPIO_T::INTEN: RHIEN6 Mask */ #define GPIO_INTEN_RHIEN7_Pos (23) /*!< GPIO_T::INTEN: RHIEN7 Position */ #define GPIO_INTEN_RHIEN7_Msk (0x1ul << GPIO_INTEN_RHIEN7_Pos) /*!< GPIO_T::INTEN: RHIEN7 Mask */ #define GPIO_INTEN_RHIEN8_Pos (24) /*!< GPIO_T::INTEN: RHIEN8 Position */ #define GPIO_INTEN_RHIEN8_Msk (0x1ul << GPIO_INTEN_RHIEN8_Pos) /*!< GPIO_T::INTEN: RHIEN8 Mask */ #define GPIO_INTEN_RHIEN9_Pos (25) /*!< GPIO_T::INTEN: RHIEN9 Position */ #define GPIO_INTEN_RHIEN9_Msk (0x1ul << GPIO_INTEN_RHIEN9_Pos) /*!< GPIO_T::INTEN: RHIEN9 Mask */ #define GPIO_INTEN_RHIEN10_Pos (26) /*!< GPIO_T::INTEN: RHIEN10 Position */ #define GPIO_INTEN_RHIEN10_Msk (0x1ul << GPIO_INTEN_RHIEN10_Pos) /*!< GPIO_T::INTEN: RHIEN10 Mask */ #define GPIO_INTEN_RHIEN11_Pos (27) /*!< GPIO_T::INTEN: RHIEN11 Position */ #define GPIO_INTEN_RHIEN11_Msk (0x1ul << GPIO_INTEN_RHIEN11_Pos) /*!< GPIO_T::INTEN: RHIEN11 Mask */ #define GPIO_INTEN_RHIEN12_Pos (28) /*!< GPIO_T::INTEN: RHIEN12 Position */ #define GPIO_INTEN_RHIEN12_Msk (0x1ul << GPIO_INTEN_RHIEN12_Pos) /*!< GPIO_T::INTEN: RHIEN12 Mask */ #define GPIO_INTEN_RHIEN13_Pos (29) /*!< GPIO_T::INTEN: RHIEN13 Position */ #define GPIO_INTEN_RHIEN13_Msk (0x1ul << GPIO_INTEN_RHIEN13_Pos) /*!< GPIO_T::INTEN: RHIEN13 Mask */ #define GPIO_INTEN_RHIEN14_Pos (30) /*!< GPIO_T::INTEN: RHIEN14 Position */ #define GPIO_INTEN_RHIEN14_Msk (0x1ul << GPIO_INTEN_RHIEN14_Pos) /*!< GPIO_T::INTEN: RHIEN14 Mask */ #define GPIO_INTEN_RHIEN15_Pos (31) /*!< GPIO_T::INTEN: RHIEN15 Position */ #define GPIO_INTEN_RHIEN15_Msk (0x1ul << GPIO_INTEN_RHIEN15_Pos) /*!< GPIO_T::INTEN: RHIEN15 Mask */ #define GPIO_INTSRC_INTSRC0_Pos (0) /*!< GPIO_T::INTSRC: INTSRC0 Position */ #define GPIO_INTSRC_INTSRC0_Msk (0x1ul << GPIO_INTSRC_INTSRC0_Pos) /*!< GPIO_T::INTSRC: INTSRC0 Mask */ #define GPIO_INTSRC_INTSRC1_Pos (1) /*!< GPIO_T::INTSRC: INTSRC1 Position */ #define GPIO_INTSRC_INTSRC1_Msk (0x1ul << GPIO_INTSRC_INTSRC1_Pos) /*!< GPIO_T::INTSRC: INTSRC1 Mask */ #define GPIO_INTSRC_INTSRC2_Pos (2) /*!< GPIO_T::INTSRC: INTSRC2 Position */ #define GPIO_INTSRC_INTSRC2_Msk (0x1ul << GPIO_INTSRC_INTSRC2_Pos) /*!< GPIO_T::INTSRC: INTSRC2 Mask */ #define GPIO_INTSRC_INTSRC3_Pos (3) /*!< GPIO_T::INTSRC: INTSRC3 Position */ #define GPIO_INTSRC_INTSRC3_Msk (0x1ul << GPIO_INTSRC_INTSRC3_Pos) /*!< GPIO_T::INTSRC: INTSRC3 Mask */ #define GPIO_INTSRC_INTSRC4_Pos (4) /*!< GPIO_T::INTSRC: INTSRC4 Position */ #define GPIO_INTSRC_INTSRC4_Msk (0x1ul << GPIO_INTSRC_INTSRC4_Pos) /*!< GPIO_T::INTSRC: INTSRC4 Mask */ #define GPIO_INTSRC_INTSRC5_Pos (5) /*!< GPIO_T::INTSRC: INTSRC5 Position */ #define GPIO_INTSRC_INTSRC5_Msk (0x1ul << GPIO_INTSRC_INTSRC5_Pos) /*!< GPIO_T::INTSRC: INTSRC5 Mask */ #define GPIO_INTSRC_INTSRC6_Pos (6) /*!< GPIO_T::INTSRC: INTSRC6 Position */ #define GPIO_INTSRC_INTSRC6_Msk (0x1ul << GPIO_INTSRC_INTSRC6_Pos) /*!< GPIO_T::INTSRC: INTSRC6 Mask */ #define GPIO_INTSRC_INTSRC7_Pos (7) /*!< GPIO_T::INTSRC: INTSRC7 Position */ #define GPIO_INTSRC_INTSRC7_Msk (0x1ul << GPIO_INTSRC_INTSRC7_Pos) /*!< GPIO_T::INTSRC: INTSRC7 Mask */ #define GPIO_INTSRC_INTSRC8_Pos (8) /*!< GPIO_T::INTSRC: INTSRC8 Position */ #define GPIO_INTSRC_INTSRC8_Msk (0x1ul << GPIO_INTSRC_INTSRC8_Pos) /*!< GPIO_T::INTSRC: INTSRC8 Mask */ #define GPIO_INTSRC_INTSRC9_Pos (9) /*!< GPIO_T::INTSRC: INTSRC9 Position */ #define GPIO_INTSRC_INTSRC9_Msk (0x1ul << GPIO_INTSRC_INTSRC9_Pos) /*!< GPIO_T::INTSRC: INTSRC9 Mask */ #define GPIO_INTSRC_INTSRC10_Pos (10) /*!< GPIO_T::INTSRC: INTSRC10 Position */ #define GPIO_INTSRC_INTSRC10_Msk (0x1ul << GPIO_INTSRC_INTSRC10_Pos) /*!< GPIO_T::INTSRC: INTSRC10 Mask */ #define GPIO_INTSRC_INTSRC11_Pos (11) /*!< GPIO_T::INTSRC: INTSRC11 Position */ #define GPIO_INTSRC_INTSRC11_Msk (0x1ul << GPIO_INTSRC_INTSRC11_Pos) /*!< GPIO_T::INTSRC: INTSRC11 Mask */ #define GPIO_INTSRC_INTSRC12_Pos (12) /*!< GPIO_T::INTSRC: INTSRC12 Position */ #define GPIO_INTSRC_INTSRC12_Msk (0x1ul << GPIO_INTSRC_INTSRC12_Pos) /*!< GPIO_T::INTSRC: INTSRC12 Mask */ #define GPIO_INTSRC_INTSRC13_Pos (13) /*!< GPIO_T::INTSRC: INTSRC13 Position */ #define GPIO_INTSRC_INTSRC13_Msk (0x1ul << GPIO_INTSRC_INTSRC13_Pos) /*!< GPIO_T::INTSRC: INTSRC13 Mask */ #define GPIO_INTSRC_INTSRC14_Pos (14) /*!< GPIO_T::INTSRC: INTSRC14 Position */ #define GPIO_INTSRC_INTSRC14_Msk (0x1ul << GPIO_INTSRC_INTSRC14_Pos) /*!< GPIO_T::INTSRC: INTSRC14 Mask */ #define GPIO_INTSRC_INTSRC15_Pos (15) /*!< GPIO_T::INTSRC: INTSRC15 Position */ #define GPIO_INTSRC_INTSRC15_Msk (0x1ul << GPIO_INTSRC_INTSRC15_Pos) /*!< GPIO_T::INTSRC: INTSRC15 Mask */ #define GPIO_SMTEN_SMTEN0_Pos (0) /*!< GPIO_T::SMTEN: SMTEN0 Position */ #define GPIO_SMTEN_SMTEN0_Msk (0x1ul << GPIO_SMTEN_SMTEN0_Pos) /*!< GPIO_T::SMTEN: SMTEN0 Mask */ #define GPIO_SMTEN_SMTEN1_Pos (1) /*!< GPIO_T::SMTEN: SMTEN1 Position */ #define GPIO_SMTEN_SMTEN1_Msk (0x1ul << GPIO_SMTEN_SMTEN1_Pos) /*!< GPIO_T::SMTEN: SMTEN1 Mask */ #define GPIO_SMTEN_SMTEN2_Pos (2) /*!< GPIO_T::SMTEN: SMTEN2 Position */ #define GPIO_SMTEN_SMTEN2_Msk (0x1ul << GPIO_SMTEN_SMTEN2_Pos) /*!< GPIO_T::SMTEN: SMTEN2 Mask */ #define GPIO_SMTEN_SMTEN3_Pos (3) /*!< GPIO_T::SMTEN: SMTEN3 Position */ #define GPIO_SMTEN_SMTEN3_Msk (0x1ul << GPIO_SMTEN_SMTEN3_Pos) /*!< GPIO_T::SMTEN: SMTEN3 Mask */ #define GPIO_SMTEN_SMTEN4_Pos (4) /*!< GPIO_T::SMTEN: SMTEN4 Position */ #define GPIO_SMTEN_SMTEN4_Msk (0x1ul << GPIO_SMTEN_SMTEN4_Pos) /*!< GPIO_T::SMTEN: SMTEN4 Mask */ #define GPIO_SMTEN_SMTEN5_Pos (5) /*!< GPIO_T::SMTEN: SMTEN5 Position */ #define GPIO_SMTEN_SMTEN5_Msk (0x1ul << GPIO_SMTEN_SMTEN5_Pos) /*!< GPIO_T::SMTEN: SMTEN5 Mask */ #define GPIO_SMTEN_SMTEN6_Pos (6) /*!< GPIO_T::SMTEN: SMTEN6 Position */ #define GPIO_SMTEN_SMTEN6_Msk (0x1ul << GPIO_SMTEN_SMTEN6_Pos) /*!< GPIO_T::SMTEN: SMTEN6 Mask */ #define GPIO_SMTEN_SMTEN7_Pos (7) /*!< GPIO_T::SMTEN: SMTEN7 Position */ #define GPIO_SMTEN_SMTEN7_Msk (0x1ul << GPIO_SMTEN_SMTEN7_Pos) /*!< GPIO_T::SMTEN: SMTEN7 Mask */ #define GPIO_SMTEN_SMTEN8_Pos (8) /*!< GPIO_T::SMTEN: SMTEN8 Position */ #define GPIO_SMTEN_SMTEN8_Msk (0x1ul << GPIO_SMTEN_SMTEN8_Pos) /*!< GPIO_T::SMTEN: SMTEN8 Mask */ #define GPIO_SMTEN_SMTEN9_Pos (9) /*!< GPIO_T::SMTEN: SMTEN9 Position */ #define GPIO_SMTEN_SMTEN9_Msk (0x1ul << GPIO_SMTEN_SMTEN9_Pos) /*!< GPIO_T::SMTEN: SMTEN9 Mask */ #define GPIO_SMTEN_SMTEN10_Pos (10) /*!< GPIO_T::SMTEN: SMTEN10 Position */ #define GPIO_SMTEN_SMTEN10_Msk (0x1ul << GPIO_SMTEN_SMTEN10_Pos) /*!< GPIO_T::SMTEN: SMTEN10 Mask */ #define GPIO_SMTEN_SMTEN11_Pos (11) /*!< GPIO_T::SMTEN: SMTEN11 Position */ #define GPIO_SMTEN_SMTEN11_Msk (0x1ul << GPIO_SMTEN_SMTEN11_Pos) /*!< GPIO_T::SMTEN: SMTEN11 Mask */ #define GPIO_SMTEN_SMTEN12_Pos (12) /*!< GPIO_T::SMTEN: SMTEN12 Position */ #define GPIO_SMTEN_SMTEN12_Msk (0x1ul << GPIO_SMTEN_SMTEN12_Pos) /*!< GPIO_T::SMTEN: SMTEN12 Mask */ #define GPIO_SMTEN_SMTEN13_Pos (13) /*!< GPIO_T::SMTEN: SMTEN13 Position */ #define GPIO_SMTEN_SMTEN13_Msk (0x1ul << GPIO_SMTEN_SMTEN13_Pos) /*!< GPIO_T::SMTEN: SMTEN13 Mask */ #define GPIO_SMTEN_SMTEN14_Pos (14) /*!< GPIO_T::SMTEN: SMTEN14 Position */ #define GPIO_SMTEN_SMTEN14_Msk (0x1ul << GPIO_SMTEN_SMTEN14_Pos) /*!< GPIO_T::SMTEN: SMTEN14 Mask */ #define GPIO_SMTEN_SMTEN15_Pos (15) /*!< GPIO_T::SMTEN: SMTEN15 Position */ #define GPIO_SMTEN_SMTEN15_Msk (0x1ul << GPIO_SMTEN_SMTEN15_Pos) /*!< GPIO_T::SMTEN: SMTEN15 Mask */ #define GPIO_SLEWCTL_HSREN0_Pos (0) /*!< GPIO_T::SLEWCTL: HSREN0 Position */ #define GPIO_SLEWCTL_HSREN0_Msk (0x1ul << GPIO_SLEWCTL_HSREN0_Pos) /*!< GPIO_T::SLEWCTL: HSREN0 Mask */ #define GPIO_SLEWCTL_HSREN1_Pos (1) /*!< GPIO_T::SLEWCTL: HSREN1 Position */ #define GPIO_SLEWCTL_HSREN1_Msk (0x1ul << GPIO_SLEWCTL_HSREN1_Pos) /*!< GPIO_T::SLEWCTL: HSREN1 Mask */ #define GPIO_SLEWCTL_HSREN2_Pos (2) /*!< GPIO_T::SLEWCTL: HSREN2 Position */ #define GPIO_SLEWCTL_HSREN2_Msk (0x1ul << GPIO_SLEWCTL_HSREN2_Pos) /*!< GPIO_T::SLEWCTL: HSREN2 Mask */ #define GPIO_SLEWCTL_HSREN3_Pos (3) /*!< GPIO_T::SLEWCTL: HSREN3 Position */ #define GPIO_SLEWCTL_HSREN3_Msk (0x1ul << GPIO_SLEWCTL_HSREN3_Pos) /*!< GPIO_T::SLEWCTL: HSREN3 Mask */ #define GPIO_SLEWCTL_HSREN4_Pos (4) /*!< GPIO_T::SLEWCTL: HSREN4 Position */ #define GPIO_SLEWCTL_HSREN4_Msk (0x1ul << GPIO_SLEWCTL_HSREN4_Pos) /*!< GPIO_T::SLEWCTL: HSREN4 Mask */ #define GPIO_SLEWCTL_HSREN5_Pos (5) /*!< GPIO_T::SLEWCTL: HSREN5 Position */ #define GPIO_SLEWCTL_HSREN5_Msk (0x1ul << GPIO_SLEWCTL_HSREN5_Pos) /*!< GPIO_T::SLEWCTL: HSREN5 Mask */ #define GPIO_SLEWCTL_HSREN6_Pos (6) /*!< GPIO_T::SLEWCTL: HSREN6 Position */ #define GPIO_SLEWCTL_HSREN6_Msk (0x1ul << GPIO_SLEWCTL_HSREN6_Pos) /*!< GPIO_T::SLEWCTL: HSREN6 Mask */ #define GPIO_SLEWCTL_HSREN7_Pos (7) /*!< GPIO_T::SLEWCTL: HSREN7 Position */ #define GPIO_SLEWCTL_HSREN7_Msk (0x1ul << GPIO_SLEWCTL_HSREN7_Pos) /*!< GPIO_T::SLEWCTL: HSREN7 Mask */ #define GPIO_SLEWCTL_HSREN8_Pos (8) /*!< GPIO_T::SLEWCTL: HSREN8 Position */ #define GPIO_SLEWCTL_HSREN8_Msk (0x1ul << GPIO_SLEWCTL_HSREN8_Pos) /*!< GPIO_T::SLEWCTL: HSREN8 Mask */ #define GPIO_SLEWCTL_HSREN9_Pos (9) /*!< GPIO_T::SLEWCTL: HSREN9 Position */ #define GPIO_SLEWCTL_HSREN9_Msk (0x1ul << GPIO_SLEWCTL_HSREN9_Pos) /*!< GPIO_T::SLEWCTL: HSREN9 Mask */ #define GPIO_SLEWCTL_HSREN10_Pos (10) /*!< GPIO_T::SLEWCTL: HSREN10 Position */ #define GPIO_SLEWCTL_HSREN10_Msk (0x1ul << GPIO_SLEWCTL_HSREN10_Pos) /*!< GPIO_T::SLEWCTL: HSREN10 Mask */ #define GPIO_SLEWCTL_HSREN11_Pos (11) /*!< GPIO_T::SLEWCTL: HSREN11 Position */ #define GPIO_SLEWCTL_HSREN11_Msk (0x1ul << GPIO_SLEWCTL_HSREN11_Pos) /*!< GPIO_T::SLEWCTL: HSREN11 Mask */ #define GPIO_SLEWCTL_HSREN12_Pos (12) /*!< GPIO_T::SLEWCTL: HSREN12 Position */ #define GPIO_SLEWCTL_HSREN12_Msk (0x1ul << GPIO_SLEWCTL_HSREN12_Pos) /*!< GPIO_T::SLEWCTL: HSREN12 Mask */ #define GPIO_SLEWCTL_HSREN13_Pos (13) /*!< GPIO_T::SLEWCTL: HSREN13 Position */ #define GPIO_SLEWCTL_HSREN13_Msk (0x1ul << GPIO_SLEWCTL_HSREN13_Pos) /*!< GPIO_T::SLEWCTL: HSREN13 Mask */ #define GPIO_SLEWCTL_HSREN14_Pos (14) /*!< GPIO_T::SLEWCTL: HSREN14 Position */ #define GPIO_SLEWCTL_HSREN14_Msk (0x1ul << GPIO_SLEWCTL_HSREN14_Pos) /*!< GPIO_T::SLEWCTL: HSREN14 Mask */ #define GPIO_SLEWCTL_HSREN15_Pos (15) /*!< GPIO_T::SLEWCTL: HSREN15 Position */ #define GPIO_SLEWCTL_HSREN15_Msk (0x1ul << GPIO_SLEWCTL_HSREN15_Pos) /*!< GPIO_T::SLEWCTL: HSREN15 Mask */ #define GPIO_DRVCTL_HDRVEN8_Pos (8) /*!< GPIO_T::DRVCTL: HDRVEN8 Position */ #define GPIO_DRVCTL_HDRVEN8_Msk (0x1ul << GPIO_DRVCTL_HDRVEN8_Pos) /*!< GPIO_T::DRVCTL: HDRVEN8 Mask */ #define GPIO_DRVCTL_HDRVEN9_Pos (9) /*!< GPIO_T::DRVCTL: HDRVEN9 Position */ #define GPIO_DRVCTL_HDRVEN9_Msk (0x1ul << GPIO_DRVCTL_HDRVEN9_Pos) /*!< GPIO_T::DRVCTL: HDRVEN9 Mask */ #define GPIO_DRVCTL_HDRVEN10_Pos (10) /*!< GPIO_T::DRVCTL: HDRVEN10 Position */ #define GPIO_DRVCTL_HDRVEN10_Msk (0x1ul << GPIO_DRVCTL_HDRVEN10_Pos) /*!< GPIO_T::DRVCTL: HDRVEN10 Mask */ #define GPIO_DRVCTL_HDRVEN11_Pos (11) /*!< GPIO_T::DRVCTL: HDRVEN11 Position */ #define GPIO_DRVCTL_HDRVEN11_Msk (0x1ul << GPIO_DRVCTL_HDRVEN11_Pos) /*!< GPIO_T::DRVCTL: HDRVEN11 Mask */ #define GPIO_DRVCTL_HDRVEN12_Pos (12) /*!< GPIO_T::DRVCTL: HDRVEN12 Position */ #define GPIO_DRVCTL_HDRVEN12_Msk (0x1ul << GPIO_DRVCTL_HDRVEN12_Pos) /*!< GPIO_T::DRVCTL: HDRVEN12 Mask */ #define GPIO_DRVCTL_HDRVEN13_Pos (13) /*!< GPIO_T::DRVCTL: HDRVEN13 Position */ #define GPIO_DRVCTL_HDRVEN13_Msk (0x1ul << GPIO_DRVCTL_HDRVEN13_Pos) /*!< GPIO_T::DRVCTL: HDRVEN13 Mask */ #define GPIO_DBCTL_DBCLKSEL_Pos (0) /*!< GPIO_T::DBCTL: DBCLKSEL Position */ #define GPIO_DBCTL_DBCLKSEL_Msk (0xFul << GPIO_DBCTL_DBCLKSEL_Pos) /*!< GPIO_T::DBCTL: DBCLKSEL Mask */ #define GPIO_DBCTL_DBCLKSRC_Pos (4) /*!< GPIO_T::DBCTL: DBCLKSRC Position */ #define GPIO_DBCTL_DBCLKSRC_Msk (1ul << GPIO_DBCTL_DBCLKSRC_Pos) /*!< GPIO_T::DBCTL: DBCLKSRC Mask */ #define GPIO_DBCTL_ICLKON_Pos (5) /*!< GPIO_T::DBCTL: ICLKON Position */ #define GPIO_DBCTL_ICLKON_Msk (1ul << GPIO_DBCTL_ICLKON_Pos) /*!< GPIO_T::DBCTL: ICLKON Mask */ /**@}*/ /* GPIO_CONST */ /**@}*/ /* end of GPIO register group */

PB->MODE = (PB->MODE & (~GPIO_MODE_MODE2_Msk)) | (GPIO_MODE_INPUT << GPIO_MODE_MODE2_Pos);

设置PB2为输入模式通过这个,你是否明白了?

void GPIO_SetMode(GPIO_T *port, uint32_t u32PinMask, uint32_t u32Mode)

{

uint32_t i;

for(i = 0; i < GPIO_PIN_MAX; i++)

{

if(u32PinMask & (1 << i))

{

port->MODE = (port->MODE & ~(0x3 << (i << 1))) | (u32Mode << (i << 1));

}

}

}

这个一一对应之后,之后的关于类似的问题都可以迎刃而解啦,哈哈

i为2 0X3<<(i<<1)=0X3<<0X4即0X3左移4位对照上文的宏定义对应GPIO_MODE_MODE2_Msk

#define GPIO_MODE_MODE2_Msk (0x3ul << GPIO_MODE_MODE2_Pos) /*!< GPIO_T::MODE: MODE2 Mask */