<ignore_js_op>

<ignore_js_op>

1. 管脚复用以及引脚配置

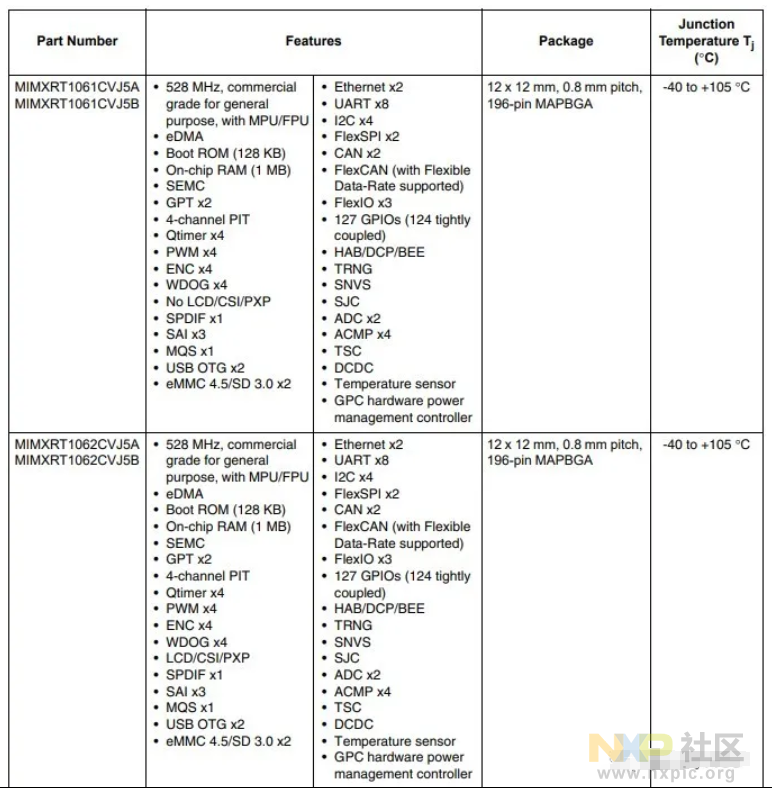

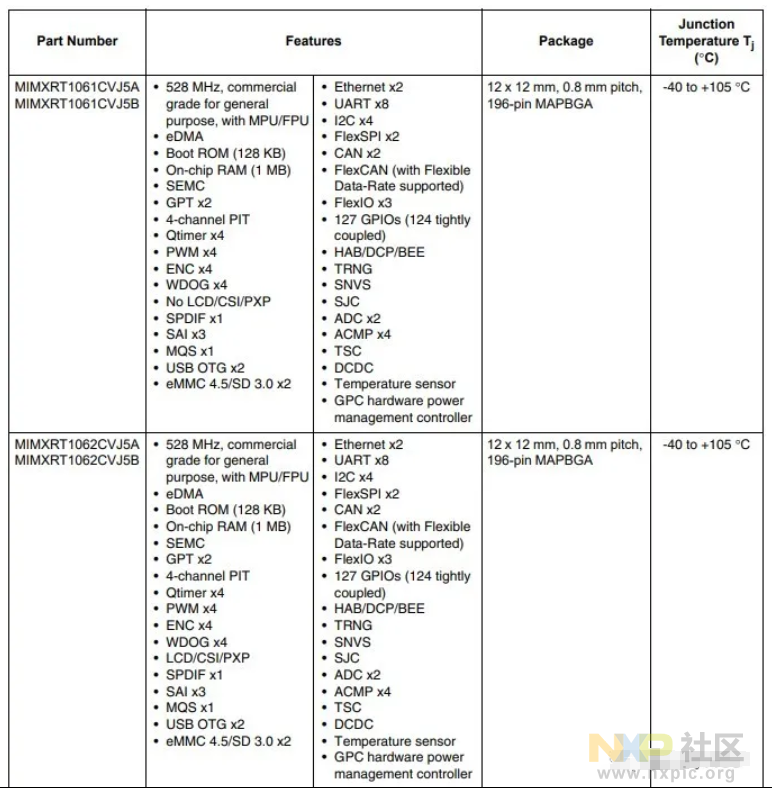

官方的以太网接口电路图,采用的是KSZ8081的PHY芯片,官方默认的一路以太网使用的配置接口采用RMII模式,如下图所示:

<ignore_js_op>

<ignore_js_op>

当然如果有其他外设的需求,比如需要外扩SDRAM等,MDC和MDIO的引脚可以选择配置为不占用SDRAM外扩总线EMC接口的复用引脚。

<ignore_js_op>

BT_CFG8, BT_CFG_9, BT_CFG_10,BT_CFG11这4个引脚配置为第二路以太网的引脚(BT_CFG8作为第二路以太网的TXD0;BT_CFG9作为第二路以太网的TXD1;BT_CFG10作为第二路以太网的TXEN;BT_CFG11作为以太网的TX_CLK)。同时,又作为BOOT的启动引脚,上电复位前,BT_CFG8,BT_CFG_9, BT_CFG_10这3个脚的状态都应该是高电平才能进入QSPI启动模式。

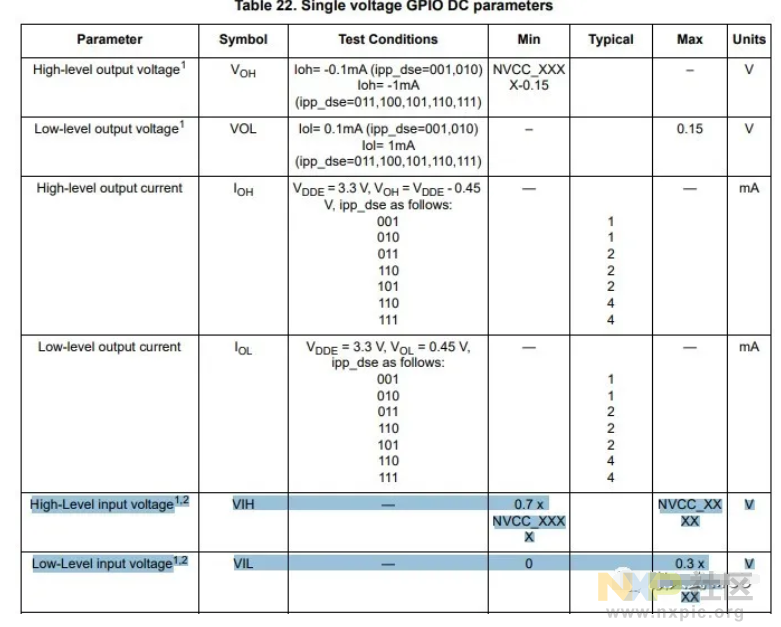

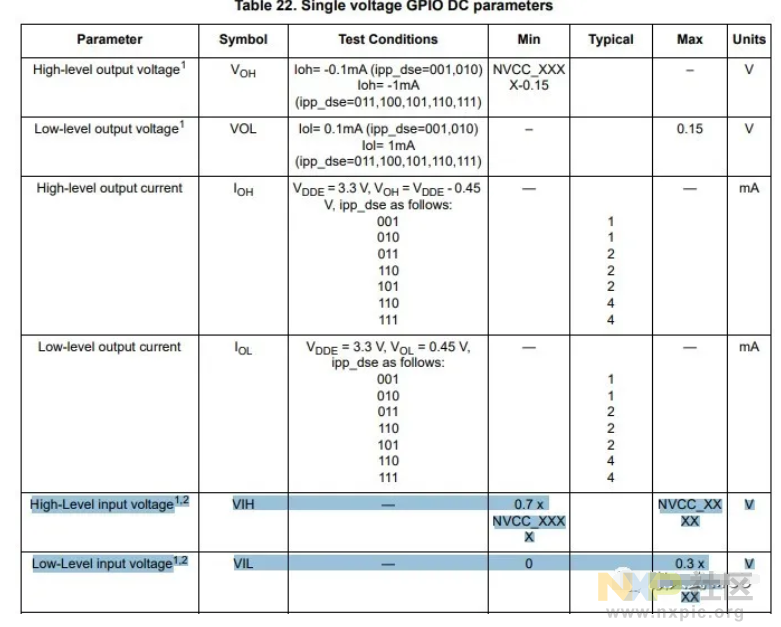

如果在上电前或者是POR引脚处于复位状态时,这几个引脚电平如果是未定状态,例如如果是1.6v,也就是既非高(3.3v的70%以上),也非低电平(3.3v的30%以下)的状态,则系统上电启动会失败。

<ignore_js_op>

其中默认情况下,BT_CFG8, BT_CFG9, BT_CFG10在使用QSPI模式的时候,应该是低电平状态。但是如果使用BT_CFG8, BT_CFG9, BT_CFG10作为复选功能,也就是以太网功能的时候,需要设置为高电平。根据参考手册i.MX RT1060 Processor Reference Manual, Rev. 2 215页的描述,BT_CFG[10], BT_CFG[9], BT_CFG[8]的电平设置应该是111b–QSPIdevice supports 3B read by default (on secondary pinmux option) (command: 0x03,SPI mode)。

<ignore_js_op>

当然也可以通过MCUBootUtility工具将BT_FUSE_SEL写入1,上电的时候就不会判断这几个BOOT引脚的电平状态,直接根据eFUSE的配置,从QSPI启动即可。这种这几个BT_CFG 引脚上电的时候就可以配置为其他的功能口, 而不作为BOOT引脚功能。

<ignore_js_op>

2. SDK中代码的修改

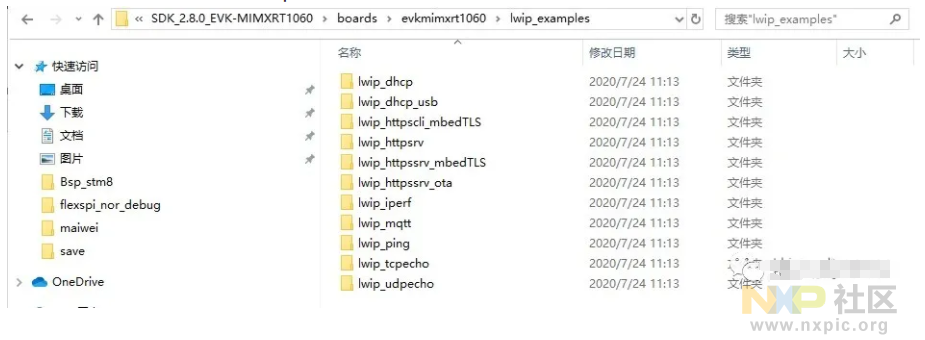

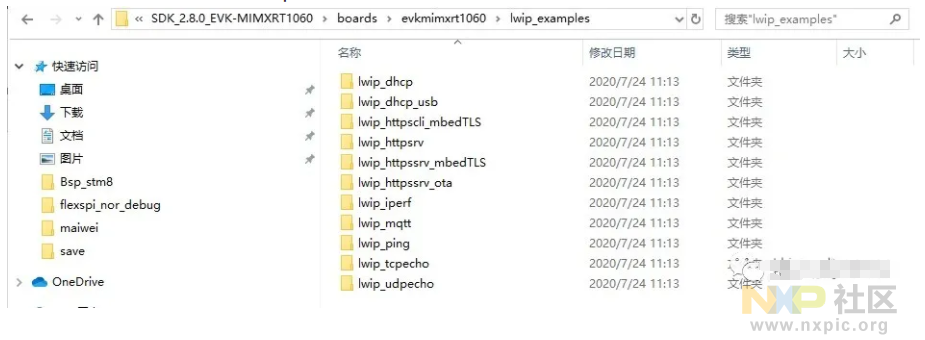

SDK里面提供了丰富的Lwip以太网的参考代码,有基于裸机和基于Freertos的版本。

<ignore_js_op>

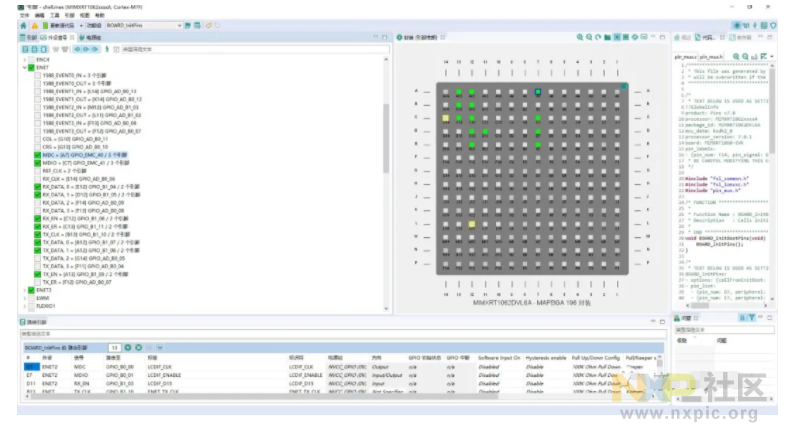

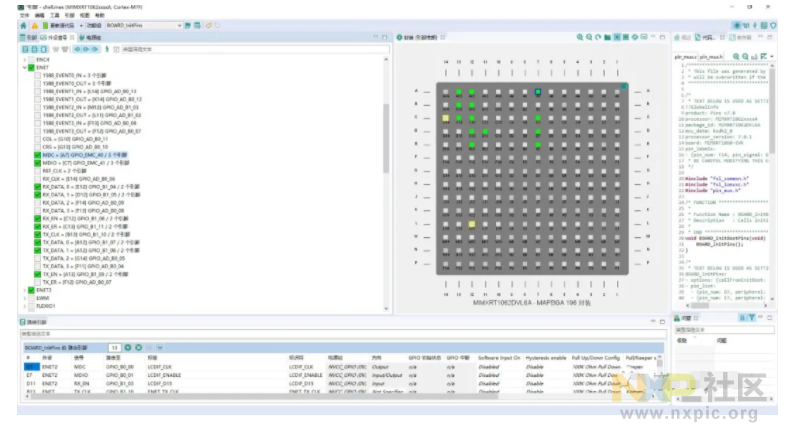

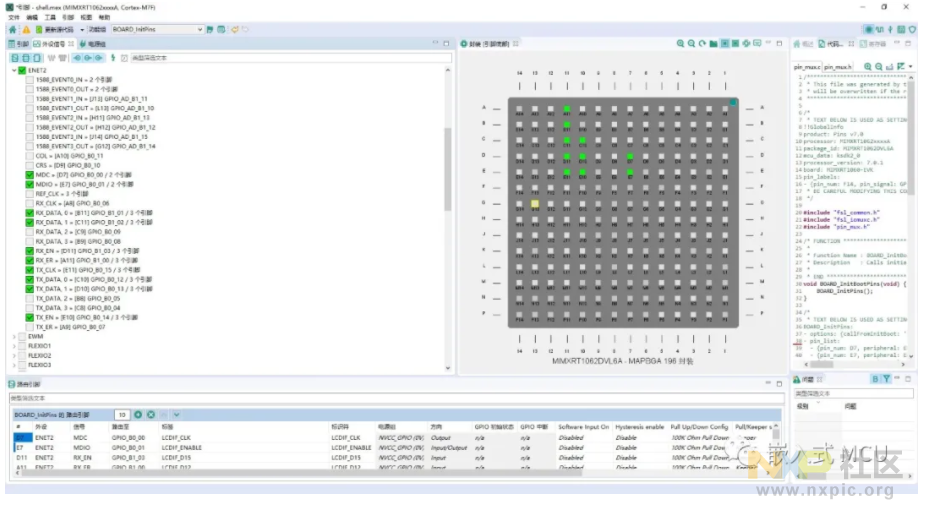

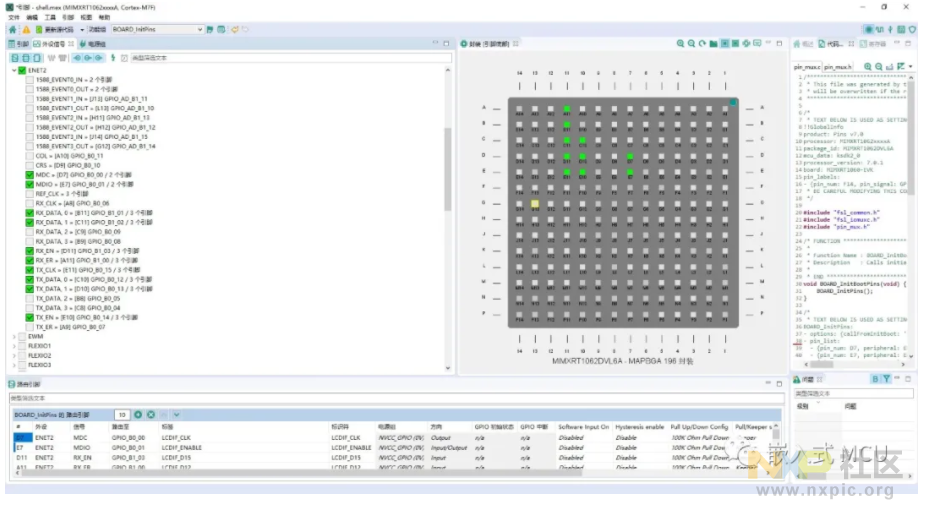

SDK2.8代码里面只是配置了第一路以太网,如果需要同时使用两路以太网。则配置第二路以太网的方法如下,采用MCU Config Tool来配置管脚,自动生成代码。

<ignore_js_op>

- IOMUXC_SetPinMux(

- IOMUXC_GPIO_B0_00_ENET2_MDC,/* GPIO_B0_00配置为 ENET2_MDC */

- 0U); /* Software Input On Field: InputPath is determined by functionality */

- IOMUXC_SetPinMux(

- IOMUXC_GPIO_B0_01_ENET2_MDIO,/*GPIO_B0_01配置为ENET2_MDIO */

- 0U);

- IOMUXC_SetPinMux(

- IOMUXC_GPIO_B0_12_ENET2_TDATA00,

- /*GPIO_B0_12配置为ENET2_TDATA00 */

- 0U);

- IOMUXC_SetPinMux(

- IOMUXC_GPIO_B0_13_ENET2_TDATA01,

- /*GPIO_B0_13配置为ENET2_TDATA01 */

- 0U);

- IOMUXC_SetPinMux(

- IOMUXC_GPIO_B0_14_ENET2_TX_EN,

- /*GPIO_B0_14配置为ENET2_TX_EN */

- 0U);

- IOMUXC_SetPinMux(

- IOMUXC_GPIO_B0_15_ENET2_REF_CLK2,

- /*GPIO_B0_15配置为ENET2_REF_CLK2 */

- 0x31U);

- IOMUXC_SetPinMux(

- IOMUXC_GPIO_B1_00_ENET2_RX_ER,

- /*GPIO_B1_00配置为ENET2_RX_ER */

- 0U);

- IOMUXC_SetPinMux(

- IOMUXC_GPIO_B1_01_ENET2_RDATA00,

- /*GPIO_B1_01配置为 ENET2_RDATA00 */

- 0U);

- IOMUXC_SetPinMux(

- IOMUXC_GPIO_B1_02_ENET2_RDATA01,

- /*GPIO_B1_02配置为 ENET2_RDATA01 */

- 0U);

- IOMUXC_SetPinMux(

- IOMUXC_GPIO_B1_03_ENET2_RX_EN,/*GPIO_B1_03配置为ENET2_RX_EN */

- 0U);

- IOMUXC_SetPinConfig(

- IOMUXC_GPIO_B0_00_ENET2_MDC,/* GPIO_B0_00配置为ENET2_MDC */

- 0xB0E9U);

- IOMUXC_SetPinConfig(

- IOMUXC_GPIO_B0_01_ENET2_MDIO,/*GPIO_B0_01配置为ENET2_MDIO */

- 0xB829U);

- IOMUXC_SetPinConfig(

- IOMUXC_GPIO_B0_12_ENET2_TDATA00,

- /*GPIO_B0_12配置为ENET2_TDATA00 */

- 0xB0E9U);

- IOMUXC_SetPinConfig(

- IOMUXC_GPIO_B0_13_ENET2_TDATA01,

- /* GPIO_B0_13配置为 ENET2_TDATA01 */

- 0xB0E9U);

- IOMUXC_SetPinConfig(

- IOMUXC_GPIO_B0_14_ENET2_TX_EN,

- /*GPIO_B0_14配置为ENET2_TX_EN */

- 0xB0E9U);

- IOMUXC_SetPinConfig(

- IOMUXC_GPIO_B0_15_ENET2_REF_CLK2,

- /*GPIO_B0_15配置为 ENET2_REF_CLK2 */

- 0xB0E9U);

- IOMUXC_SetPinConfig(

- IOMUXC_GPIO_B1_00_ENET2_RX_ER,

- /*GPIO_B1_00配置为ENET2_RX_ER */

- 0xB0E9U);

- IOMUXC_SetPinConfig(

- IOMUXC_GPIO_B1_01_ENET2_RDATA00,

- /*GPIO_B1_01配置为 ENET2_RDATA00 */

- 0xB0E9U);

- IOMUXC_SetPinConfig(

- IOMUXC_GPIO_B1_02_ENET2_RDATA01,

- /*GPIO_B1_02配置为 ENET2_RDATA01 */

- 0xB0E9U);

- IOMUXC_SetPinConfig(

- IOMUXC_GPIO_B1_03_ENET2_RX_EN,

- /*GPIO_B1_03配置为ENET2_RX_EN */

- 0xB0E9U);

- IOMUXC_EnableMode(IOMUXC_GPR,kIOMUXC_GPR_ENET2TxClkOutputDir, true);

- voidBOARD_InitModuleClock(void) {

- const clock_enet_pll_config_t config =

- {.enableClkOutput1= true, .enableClkOutput25M = false, .loopDivider1 = 1,

- };

- CLOCK_InitEnetPll(&config);

- }

- IOMUXC_SetPinMux(

- IOMUXC_GPIO_AD_B0_10_GPIO1_IO10,0U);

- IOMUXC_SetPinConfig(

- IOMUXC_GPIO_AD_B0_10_GPIO1_IO10,0xB0A9U);

- GPIO_PinInit(GPIO2, 3,&gpio_config); //复位引脚

- GPIO_PinInit(GPIO1, 10, &gpio_config);

- /*在复位前,上拉ENET_INT */

- GPIO_WritePinOutput(GPIO1, 10, 1);

- GPIO_WritePinOutput(GPIO2, 3, 0);

- delay();

- GPIO_WritePinOutput(GPIO2,3, 1);

我现在使用ENET_MDC,ENET_MDIO并接两个PHY,以PHY地址区分,结果是PHY2一直初始化不了,或者卡在初始化过程中。