make是一种控制编译或者重复编译软件的工具。

make可以自动关键软件的编译内容、方式和时机,从而使程序员把更多的精力集中在编写代码上。

make主要的机制是在命令行键入make命令,make会自动执行当前目录下的makefile文件

makefile规则

标号:依赖项

(tab键)命令代码

(tab键)命令代码

--每个命令代码的第一个字符必须是tab键,而不是空格键,不然make会报错。

命令行直接键入make,make默认只会执行第一个标号的命令代码

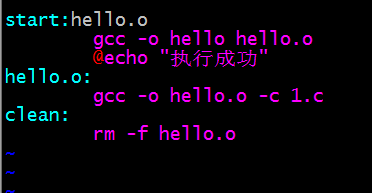

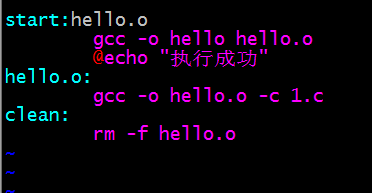

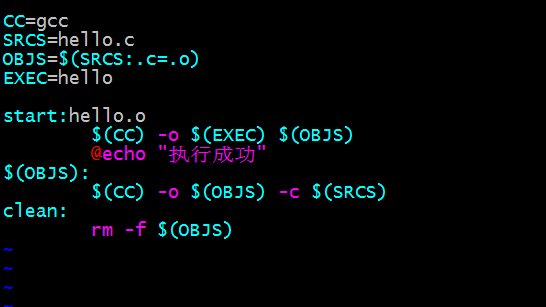

上图命令行详解

start:hello.o--表示执行start标号下的命令行需要hello.o文件,

如果当前目录下有hello.o文件,那么会直接执行start标号下的命令行;

如果当前目录下没有hello.o文件,那么make会自动寻找生成hello.o文件的标号,找到hello.o标号,

执行hello.o标号下的命令行,然后执行start标号下的命令行。

如果需要执行指定标号的命令行,必须使用make参数

--make 需要执行的标号

--例如:make clean

在make语法中"@"表示不打印该命令语句,只打印命令执行结果

--例如@echo "-OK--" 只会打印-OK---

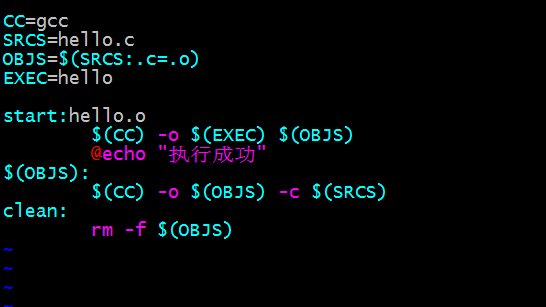

为了简化编辑和维护makefile,可以在makefile中使用变量。

--varname=some_text

把变量用括号扩起来,前面加上$符号就可以引用该变量的值

--$(varname)

按照惯例makefile的变量都是大写

$(SRCS:.c=.o)意思是将SRCS变量中的.c替换成.o

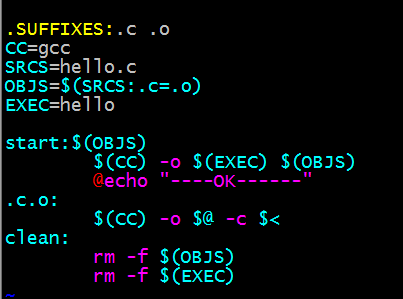

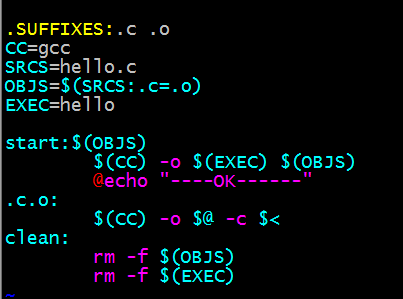

make中的依赖声明

.SUFFIXES:.c (一个空格) .o

--这表明.o文件依赖于.c文件,.c和.o文件之间存在着依赖关系

--强调:使用.SUFFIXES来表示两个文件的依赖关系,必须两个文件的文件名一致,只是文件类型不同才可以适应.SUFFIXES

在make语句start:$(OBJS)中,表明依赖项是.o文件,根据.SUFFIXES声明,.o文件依赖于.c文件,找到".c.o"标签,执行该标签下的命令

--$@表示生成的目标文件

--$<表示生成目标的源文件

--$^表示依赖项

--$@、$<都是针对于.SUFFIXES声明而言的,在.SUFFIXES声明定义的目标文件才用$@表示,源文件才用$<表示。

make中多个.c文件联合编译

--SRCS=hello.c

(tab键)add.c

--这表示有两个源文件,

--OBJS=$(SRCS:.c=.o) 此时也会对应的生成两个.o文件

--start:$(OBJS)这时候会发现两个依赖项,所以会执行".c.o"标签两次,从而生成两个.o文件。

make编译多文件时,会以.c文件的时间和.o文件的时间做对比,只编译修改过的.c文件,提高编译效率。

.PHONY:clean

WORKDIR=.

VPATH = ./src

LIBOBJS= socketclient.o itcastlog.o

OBJS= demo01_testplatform.o

LIB1 = libmysocket.so

EXE1 = mysocketexe

CC = gcc

CFLGS= -Wall -g -I$(WORKDIR)/inc/

LIBFLAG = -L$(HOME)/lib

all: $(LIB1) $(EXE1)

$(LIB1):$(LIBOBJS)

$(CC) -shared -fPIC $^ -o $@

cp $(LIB1) $(HOME)/lib

mv $(LIB1) ./lib

$(EXE1):$(OBJS)

$(CC) $^ $(LIBFLAG) -lmysocket -o $@

.c.o:

$(CC) $(CFLGS) -c $< -o $@ -shared -fPIC

clean:

rm -rf $(BIN) *.o $(HOME)/lib/$(LIB1) ./$(LIB1)