第三章处理器体系结构

4.1Y86指令体系结构

包括定义各种状态元素、指令集和他们的编码、一组编程规范和异常事件处理。

1. 8个寄存器:%eax %ecx %ebx %esi %edi %esp %ebp %edx;

2. 3个一位条件码:ZF、SF、OF;

3. Y86指令:

IA32的movl指令:irmovl、rrmovl、mrmovl、rmmovl;

整数操作指令:addl subl andl xorl ;

跳转指令:jmp jle jl je jne jge jg;

条件传送指令:cmovle cmovl cmove cmovne cmovge cmovg;

4. 指令编码:指令编码

每条指令的第一个字节表明指令的类型。这个字节分为两个部分,每个部分4位,高4位是代码部分,低4位是功能部分。

5. Y86异常

遇到异常的时候,让处理器停止执行命令。通常会调用异常处理程序,指定用来处理遇到的异常。异常处理程序还可以配置成不同的结果。

6. Y86的两种指令组合:

a. push1会将栈指针减4

b. 将一个寄存器写入存储器中

所以有两种约定:

a. 压入%esp的值

b. 压入减去4的%esp的值

4.2逻辑设计和硬件设计控制语言HCl

1.组合逻辑电路有两条限制

*两个或者多个逻辑门不能连接在一起,会使线上信号矛盾。

*网必须是无环的,不能形成回路否则会导致网络计算的函数有歧义。

2.HCl表达式和C表达式的区别

*组合电路的输出会持续的相应输入的变化,C表达式只会在执行过程中遇到被遇到时才进行求值;

*C允许参数是任意整数,而逻辑门只对应位值0和1;

*C的逻辑表达式有可能只被部分求值,逻辑门只是简单相应输入变化

3.时钟存储器和随机访问存储器

*时钟寄存器存储单个位或者字。时钟信号控制寄存器加载输入值

*随机访问存储器存储多个字,用地址来选择该读入或者该写哪个字

4.3 Y86顺序实现

1.处理组织组成阶段操作:

*取指:从寄存器读取指令字节,地址为程序计数器的值。计算下一条指令地址等于PC中的值加上已取出指令的长度

*译码:从寄存器文件中最多读出两个操作数

*执行:ALU执行指明的操作、引用的有效地址或者是修改栈指针

*访存:将数据写入存储器或者从存储器读出数据

*写回:写两个结果到寄存器文件

*更新PC:将PC设置成下条指令地址

2. SEQ的时序

*SEQ的实现包括组合逻辑和两种存储器:时钟存储器和随机访问存储器

*四个硬件但单元:程序计数器、条码寄存器数据存储器和寄存器文件

*要控制文件中的时序,只需要寄存器和存储器时钟控制

*Y86指令集遵循以下原则计算:处理器重来不需要为了完成一条指令而去读由该指更新了的状态。

实验《深入理解计算机系统》 实验五

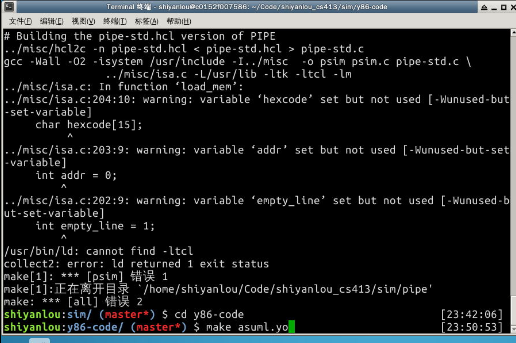

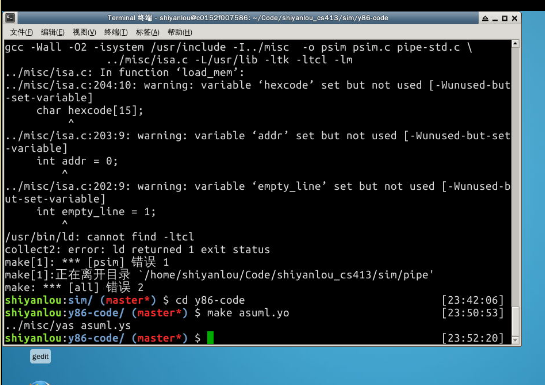

1. 构建YIS环境

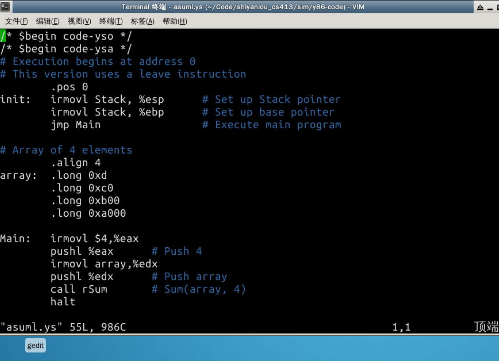

2. 测试书中P239代码asuml.y

遇到的问题和感想

在做实验楼的时候,并不知道图中的错误1和2是错在哪,只是跟着指导书往下做,仍能编译,也不知道是为什么?