参阅了一些书籍和网上的写法,在此Mark。

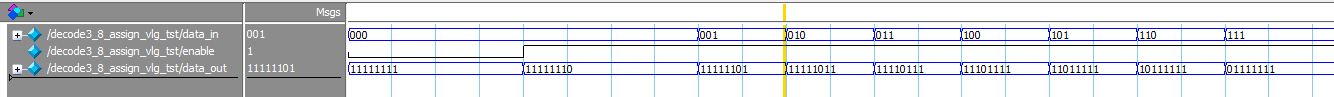

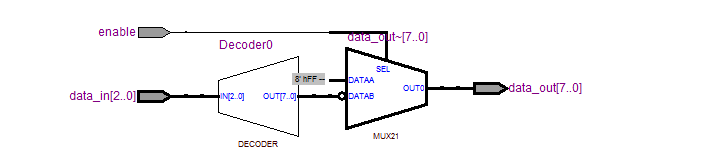

布尔表达式法

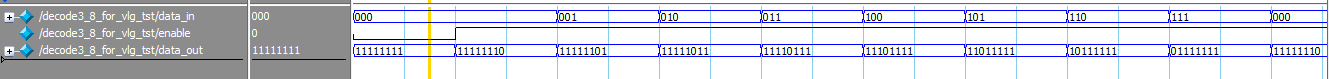

1 module decode3_8_assign (data_in,data_out,enable);//算法实现 2 input [2:0] data_in; 3 input enable; 4 output [7:0] data_out; 5 reg data_a = 8'b00000001; 6 assign data_out = (enable)?(~(data_a << data_in)):8'b11111111; 7 endmodule

testbench:

1 `timescale 1 ns/ 1 ps 2 module decode3_8_assign_vlg_tst(); 3 reg [2:0] data_in; 4 reg enable; 5 wire [7:0] data_out; 6 decode3_8_assign i1 ( 7 .data_in(data_in), 8 .data_out(data_out), 9 .enable(enable) 10 ); 11 initial 12 begin 13 enable = 0; 14 data_in = 0; 15 #20 enable = 1; 16 #10 data_in = 0; 17 #10 data_in = 1; 18 #10 data_in = 2; 19 #10 data_in = 3; 20 #10 data_in = 4; 21 #10 data_in = 5; 22 #10 data_in = 6; 23 #10 data_in = 7; 24 end 25 endmodule

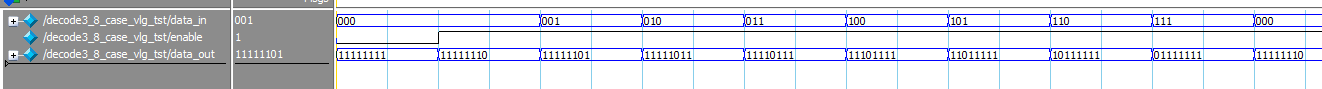

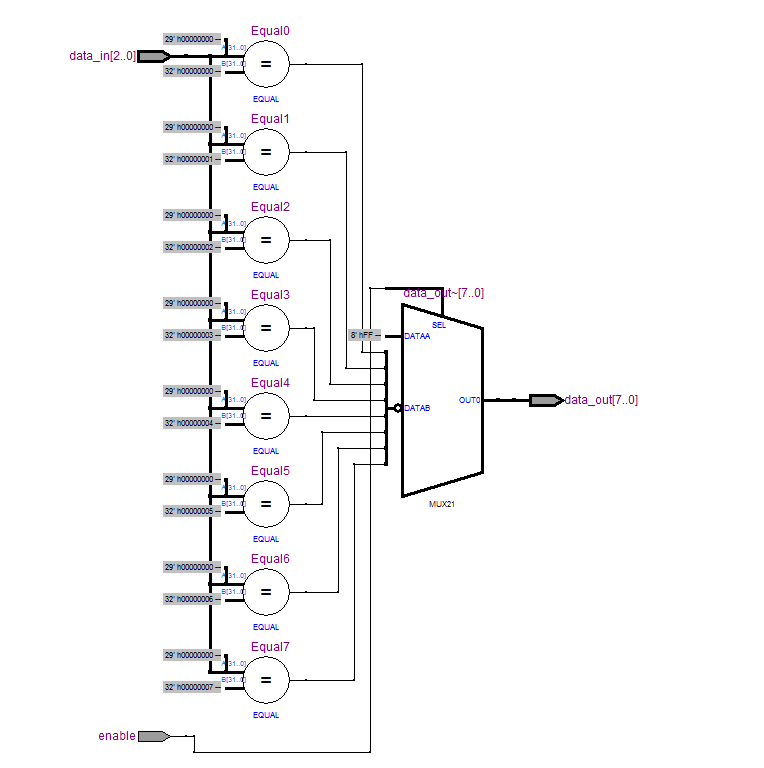

case语句法

1 module decode3_8_case (data_in,data_out,enable); 2 input [2:0] data_in; 3 input enable; 4 output [7:0] data_out; 5 reg [7:0] data_out; 6 always @ (data_in or enable) 7 begin 8 if (enable) 9 case (data_in) 10 3'b000 : data_out = 8'b11111110; 11 3'b001 : data_out = 8'b11111101; 12 3'b010 : data_out = 8'b11111011; 13 3'b011 : data_out = 8'b11110111; 14 3'b100 : data_out = 8'b11101111; 15 3'b101 : data_out = 8'b11011111; 16 3'b110 : data_out = 8'b10111111; 17 3'b111 : data_out = 8'b01111111; 18 default : data_out = 8'bxxxxxxxx; 19 endcase 20 else data_out = 8'b11111111; 21 end 22 endmodule

testbench:

1 `timescale 1 ps/ 1 ps 2 module decode3_8_case_vlg_tst(); 3 reg [2:0] data_in; 4 reg enable; 5 wire [7:0] data_out; 6 decode3_8_case i1 ( 7 .data_in(data_in), 8 .data_out(data_out), 9 .enable(enable) 10 ); 11 initial 12 begin 13 data_in = 0; 14 enable = 0; 15 #20 enable = 1; 16 while (data_in <= 3'b111)//for (i = 0;i <= 3'b111;i = i + 1) 17 begin 18 #20 data_in = data_in + 1; 19 end 20 #200 $stop; 21 end 22 endmodule

for语句法

1 module decode3_8_for (data_out,data_in,enable); 2 input [2:0] data_in; 3 input enable; 4 output [7:0] data_out; 5 reg [7:0] data_out; 6 integer i; 7 always @ (data_in or enable) 8 begin 9 if (enable) 10 begin 11 for (i = 0;i < 8;i = i + 1) 12 begin 13 if (data_in == i) 14 data_out[i] = 0; 15 else 16 data_out[i] = 1; 17 end 18 end 19 else 20 data_out = 8'hff; 21 end 22 endmodule

testbench:

1 `timescale 1 ps/ 1 ps 2 module decode3_8_for_vlg_tst(); 3 reg [2:0] data_in; 4 reg enable; 5 wire [7:0] data_out; 6 decode3_8_for i1 ( 7 .data_in(data_in), 8 .data_out(data_out), 9 .enable(enable) 10 ); 11 initial 12 begin 13 data_in = 0; 14 enable = 0; 15 #20 enable = 1; 16 while (data_in <= 3'b111)//for (i = 0;i <= 3'b111;i = i + 1) 17 begin 18 #20 data_in = data_in + 1; 19 end 20 #200 $stop; 21 end 22 endmodule

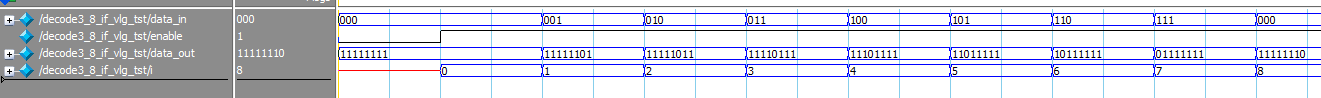

if语句法

1 `timescale 1 ps/ 1 ps 2 module decode3_8_for_vlg_tst(); 3 reg [2:0] data_in; 4 reg enable; 5 wire [7:0] data_out; 6 decode3_8_for i1 ( 7 .data_in(data_in), 8 .data_out(data_out), 9 .enable(enable) 10 ); 11 initial 12 begin 13 data_in = 0; 14 enable = 0; 15 #20 enable = 1; 16 while (data_in <= 3'b111)//for (i = 0;i <= 3'b111;i = i + 1) 17 begin 18 #20 data_in = data_in + 1; 19 end 20 #200 $stop; 21 end 22 endmodule

testbench:

1 `timescale 1 ns/ 1 ps 2 module decode3_8_if_vlg_tst(); 3 reg [2:0] data_in; 4 reg enable; 5 wire [7:0] data_out; 6 integer i; 7 decode3_8_if i1 ( 8 .data_in(data_in), 9 .data_out(data_out), 10 .enable(enable) 11 ); 12 initial 13 begin 14 data_in = 0; 15 enable = 0; 16 #20 enable = 1; 17 for (i = 0;i < 8;i = i + 1) 18 begin 19 #20 data_in = data_in + 1; 20 end 21 end 22 endmodule

如有错误还请指出,如有侵权还请告知,如需转载请注明出处!