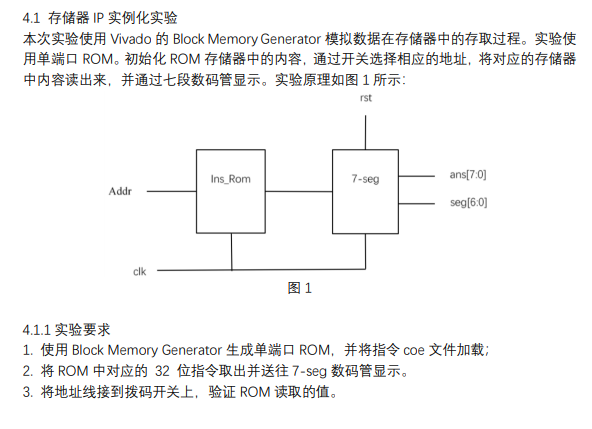

(实验环境:Vivado 2017.4)

实验要求:

实验过程:

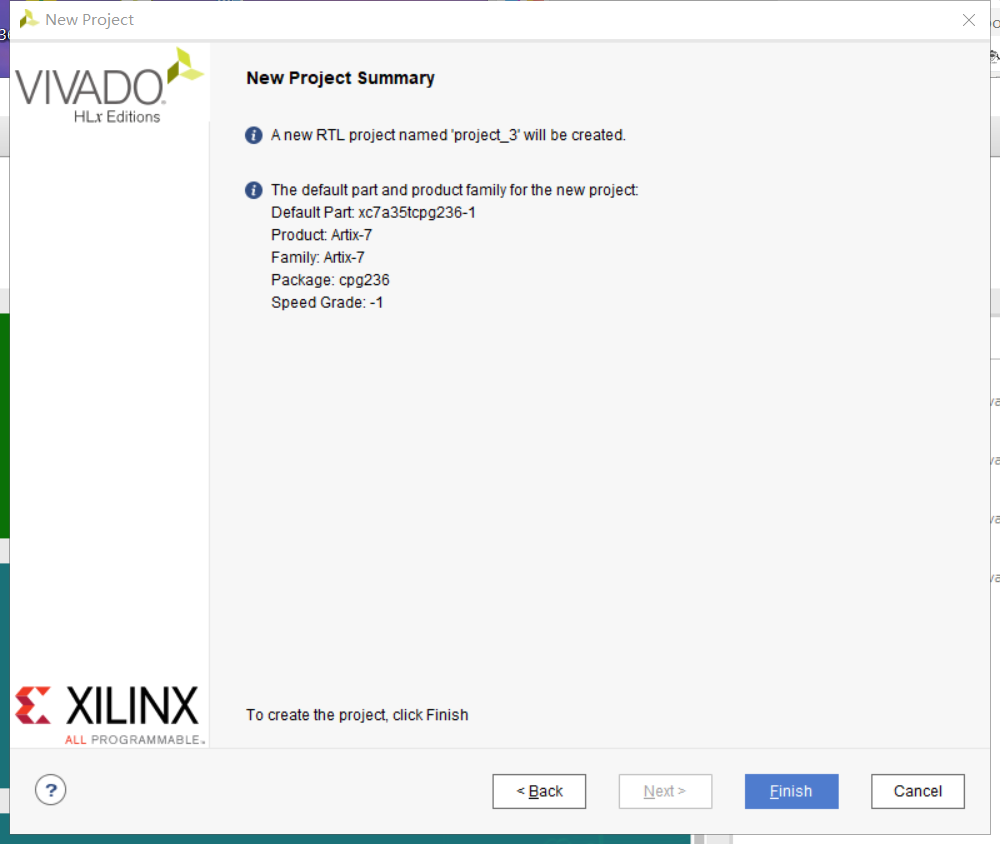

1.打开Vivado,创建文件,选择xc7a35tcpg236-1核。

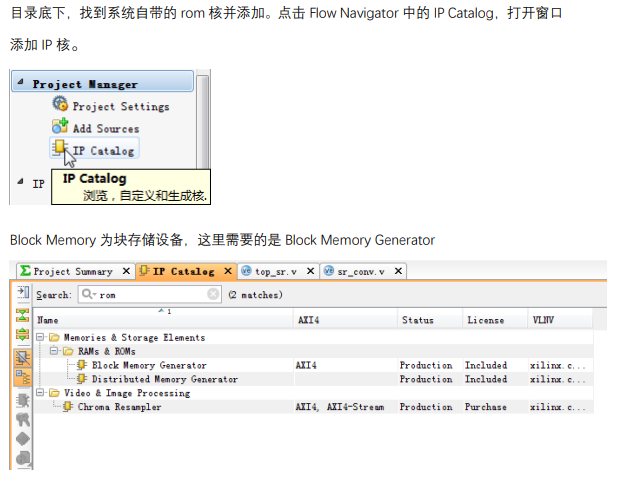

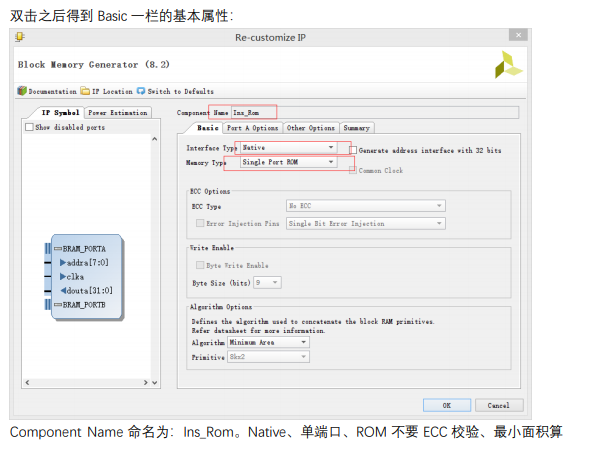

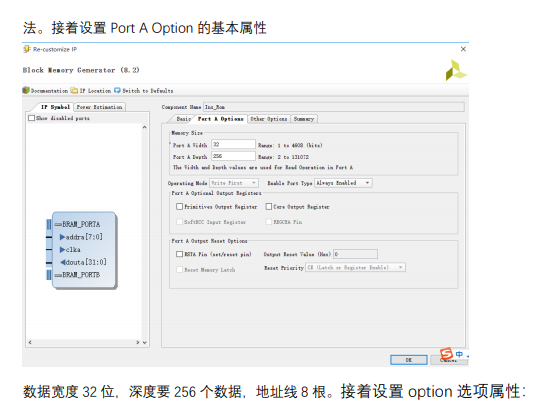

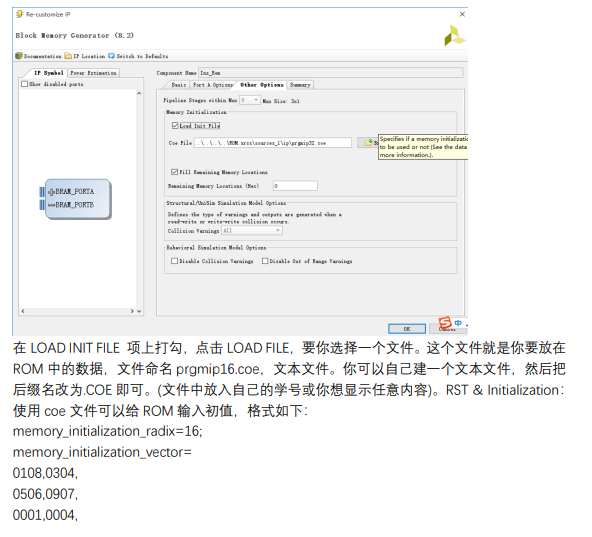

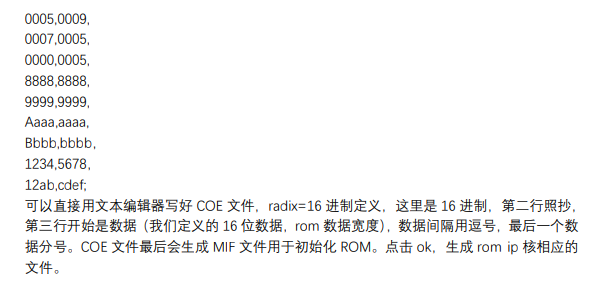

2.添加调用rom IP核。(图片来源老师,侵删)

coe文件内容:

memory_initialization_radix = 16; memory_initialization_vector = 3c01ffff, 343cf000, 8c190004, 8c180008, 8c17000c, 8c160010, 8c150014, 8c140018, 8c13001c, 8c120020, 8c110024, 8c1d0000, 23bdffff, 17a0fffe, 03e00008, af980c60, 0c00000b, af970c60, 0c00000b, af960c60, 0c00000b, af950c60, 0c00000b, af940c60, 0c00000b, af930c60, 0c00000b, af920c60, 0c00000b, af910c60, 0c00000b, af920c60, 0c00000b, af930c60, 0c00000b, af940c60, 0c00000b, af950c60, 0c00000b, af960c60, 0c00000b, af970c60, 0c00000b, af980c60, 0c00000b, af990c60, 8c1d0000, 23bdffff, 17a0fffe, 0800000f, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000, 00000000

3.添加源文件:

顶层模块:

module top( input clk, input rst, input [7:0] addr, output [3:0] ans, output [6:0] seg ); wire [31:0] data; wire [15:0] data1; assign data1=data[15:0]; Ins_Rom rom ( .clka(clk), // input wire clka .addra(addr), // input wire [7 : 0] addra .douta(data) // output wire [31 : 0] douta ); display segg( .clk(clk), .reset(rst), .s(data1), .ans(ans), .seg(seg) ); endmodule

display模块:

module display( input wire clk,reset, input wire [15:0]s, output wire [6:0]seg, output reg [3:0]ans ); reg [20:0]count; reg [4:0]digit; always@(posedge clk,posedge reset) if(reset) count = 0; else count = count + 1; always @(posedge clk) case(count[20:19]) 0:begin ans = 4'b1110; digit = s[3:0]; end 1:begin ans = 4'b1101; digit = s[7:4]; end 2:begin ans = 4'b1011; digit =s[11:8]; end 3:begin ans = 4'b0111; digit = s[15:12]; end endcase seg7 U4(.din(digit),.dout(seg)); endmodule

seg7模块:

module seg7( input wire [3:0]din, output reg [6:0]dout ); always@(*) case(din) 5'h0:dout = 7'b000_0001; 5'h1:dout = 7'b100_1111; 5'h2:dout = 7'b001_0010; 5'h3:dout = 7'b000_0110; 5'h4:dout = 7'b100_1100; 5'h5:dout = 7'b010_0100; 5'h6:dout = 7'b010_0000; 5'h7:dout = 7'b000_1111; 5'h8:dout = 7'b000_0000; 5'h9:dout = 7'b000_0100; 5'ha:dout = 7'b000_1000; 5'hb:dout = 7'b110_0000; 5'hc:dout = 7'b011_0001; 5'hd:dout = 7'b100_0010; 5'he:dout = 7'b011_0000; 5'hf:dout = 7'b011_1000; default:dout = 7'b111_1111; endcase endmodule

管脚约束文件:

## This file is a general .xdc for the Basys3 rev B board ## To use it in a project: ## - uncomment the lines corresponding to used pins ## - rename the used ports (in each line, after get_ports) according to the top level signal names in the project # Clock signal set_property PACKAGE_PIN W5 [get_ports clk] set_property IOSTANDARD LVCMOS33 [get_ports clk] create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports clk] # Switches #set_property PACKAGE_PIN V17 [get_ports {SW_in}] # set_property IOSTANDARD LVCMOS33 [get_ports {SW_in}] #set_property PACKAGE_PIN V16 [get_ports {sw[1]}] # set_property IOSTANDARD LVCMOS33 [get_ports {sw[1]}] #set_property PACKAGE_PIN W16 [get_ports {sw[2]}] #set_property IOSTANDARD LVCMOS33 [get_ports {sw[2]}] #set_property PACKAGE_PIN W17 [get_ports {sw[3]}] #set_property IOSTANDARD LVCMOS33 [get_ports {sw[3]}] #assign pins for op port #set_property PACKAGE_PIN W15 [get_ports {sw[4]}] #set_property IOSTANDARD LVCMOS33 [get_ports {sw[4]}] #set_property PACKAGE_PIN V15 [get_ports {sw[5]}] #set_property IOSTANDARD LVCMOS33 [get_ports {sw[5]}] #set_property PACKAGE_PIN W14 [get_ports {sw[6]}] #set_property IOSTANDARD LVCMOS33 [get_ports {sw[6]}] #set_property PACKAGE_PIN W13 [get_ports {sw[7]}] #set_property IOSTANDARD LVCMOS33 [get_ports {sw[7]}] #set_property PACKAGE_PIN V2 [get_ports {sw[8]}] #set_property IOSTANDARD LVCMOS33 [get_ports {sw[8]}] #set_property PACKAGE_PIN T3 [get_ports {sw[9]}] #set_property IOSTANDARD LVCMOS33 [get_ports {sw[9]}] #set_property PACKAGE_PIN T2 [get_ports {sw[10]}] #set_property IOSTANDARD LVCMOS33 [get_ports {sw[10]}] #set_property PACKAGE_PIN R3 [get_ports {sw[11]}] #set_property IOSTANDARD LVCMOS33 [get_ports {sw[11]}] #assign pins for addr port set_property PACKAGE_PIN W15 [get_ports {addr[0]}] set_property IOSTANDARD LVCMOS33 [get_ports {addr[0]}] set_property PACKAGE_PIN V15 [get_ports {addr[1]}] set_property IOSTANDARD LVCMOS33 [get_ports {addr[1]}] set_property PACKAGE_PIN W14 [get_ports {addr[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {addr[2]}] set_property PACKAGE_PIN W13 [get_ports {addr[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {addr[3]}] set_property PACKAGE_PIN V2 [get_ports {addr[4]}] set_property IOSTANDARD LVCMOS33 [get_ports {addr[4]}] set_property PACKAGE_PIN T3 [get_ports {addr[5]}] set_property IOSTANDARD LVCMOS33 [get_ports {addr[5]}] set_property PACKAGE_PIN T2 [get_ports {addr[6]}] set_property IOSTANDARD LVCMOS33 [get_ports {addr[6]}] set_property PACKAGE_PIN R3 [get_ports {addr[7]}] set_property IOSTANDARD LVCMOS33 [get_ports {addr[7]}] #set_property PACKAGE_PIN W2 [get_ports {sw[12]}] #set_property IOSTANDARD LVCMOS33 [get_ports {sw[12]}] #set_property PACKAGE_PIN U1 [get_ports {sw[13]}] #set_property IOSTANDARD LVCMOS33 [get_ports {sw[13]}] #set_property PACKAGE_PIN T1 [get_ports {sw[14]}] #set_property IOSTANDARD LVCMOS33 [get_ports {sw[14]}] #set_property PACKAGE_PIN R2 [get_ports {sw[15]}] #set_property IOSTANDARD LVCMOS33 [get_ports {sw[15]}] ## leds #set_property PACKAGE_PIN U16 [get_ports {led[0]}] # set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}] #set_property PACKAGE_PIN E19 [get_ports {led[1]}] # set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}] #set_property PACKAGE_PIN U19 [get_ports {led[2]}] # set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}] #set_property PACKAGE_PIN V19 [get_ports {led[3]}] # set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}] #set_property PACKAGE_PIN W18 [get_ports {led[4]}] # set_property IOSTANDARD LVCMOS33 [get_ports {led[4]}] #set_property PACKAGE_PIN U15 [get_ports {led[5]}] # set_property IOSTANDARD LVCMOS33 [get_ports {led[5]}] #set_property PACKAGE_PIN U14 [get_ports {led[6]}] # set_property IOSTANDARD LVCMOS33 [get_ports {led[6]}] #set_property PACKAGE_PIN V14 [get_ports {led[7]}] # set_property IOSTANDARD LVCMOS33 [get_ports {led[7]}] #set_property PACKAGE_PIN V13 [get_ports {led[8]}] # set_property IOSTANDARD LVCMOS33 [get_ports {led[8]}] #set_property PACKAGE_PIN V3 [get_ports {led[9]}] # set_property IOSTANDARD LVCMOS33 [get_ports {led[9]}] #set_property PACKAGE_PIN W3 [get_ports {led[10]}] # set_property IOSTANDARD LVCMOS33 [get_ports {led[10]}] #set_property PACKAGE_PIN U3 [get_ports {led[11]}] # set_property IOSTANDARD LVCMOS33 [get_ports {led[11]}] #set_property PACKAGE_PIN P3 [get_ports {led[12]}] # set_property IOSTANDARD LVCMOS33 [get_ports {led[12]}] #set_property PACKAGE_PIN N3 [get_ports {led[13]}] # set_property IOSTANDARD LVCMOS33 [get_ports {led[13]}] #set_property PACKAGE_PIN P1 [get_ports {led[14]}] # set_property IOSTANDARD LVCMOS33 [get_ports {led[14]}] #set_property PACKAGE_PIN L1 [get_ports {led[15]}] # set_property IOSTANDARD LVCMOS33 [get_ports {led[15]}] #7 segment display set_property PACKAGE_PIN W7 [get_ports {seg[6]}] set_property IOSTANDARD LVCMOS33 [get_ports {seg[6]}] set_property PACKAGE_PIN W6 [get_ports {seg[5]}] set_property IOSTANDARD LVCMOS33 [get_ports {seg[5]}] set_property PACKAGE_PIN U8 [get_ports {seg[4]}] set_property IOSTANDARD LVCMOS33 [get_ports {seg[4]}] set_property PACKAGE_PIN V8 [get_ports {seg[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {seg[3]}] set_property PACKAGE_PIN U5 [get_ports {seg[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {seg[2]}] set_property PACKAGE_PIN V5 [get_ports {seg[1]}] set_property IOSTANDARD LVCMOS33 [get_ports {seg[1]}] set_property PACKAGE_PIN U7 [get_ports {seg[0]}] set_property IOSTANDARD LVCMOS33 [get_ports {seg[0]}] #set_property PACKAGE_PIN V7 [get_ports dp] # set_property IOSTANDARD LVCMOS33 [get_ports dp] set_property PACKAGE_PIN U2 [get_ports {ans[0]}] set_property IOSTANDARD LVCMOS33 [get_ports {ans[0]}] set_property PACKAGE_PIN U4 [get_ports {ans[1]}] set_property IOSTANDARD LVCMOS33 [get_ports {ans[1]}] set_property PACKAGE_PIN V4 [get_ports {ans[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {ans[2]}] set_property PACKAGE_PIN W4 [get_ports {ans[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {ans[3]}] ##Buttons #set_property PACKAGE_PIN U18 [get_ports btnC] #set_property IOSTANDARD LVCMOS33 [get_ports btnC] set_property PACKAGE_PIN U18 [get_ports rst] set_property IOSTANDARD LVCMOS33 [get_ports rst] #set_property PACKAGE_PIN T18 [get_ports btnU] #set_property IOSTANDARD LVCMOS33 [get_ports btnU] #set_property PACKAGE_PIN W19 [get_ports btnL] #set_property IOSTANDARD LVCMOS33 [get_ports btnL] #set_property PACKAGE_PIN T17 [get_ports btnR] #set_property IOSTANDARD LVCMOS33 [get_ports btnR] #set_property PACKAGE_PIN U17 [get_ports btnD] #set_property IOSTANDARD LVCMOS33 [get_ports btnD] ##Pmod Header JA ##Sch name = JA1 #set_property PACKAGE_PIN J1 [get_ports {JA[0]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JA[0]}] ##Sch name = JA2 #set_property PACKAGE_PIN L2 [get_ports {JA[1]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JA[1]}] ##Sch name = JA3 #set_property PACKAGE_PIN J2 [get_ports {JA[2]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JA[2]}] ##Sch name = JA4 #set_property PACKAGE_PIN G2 [get_ports {JA[3]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JA[3]}] ##Sch name = JA7 #set_property PACKAGE_PIN H1 [get_ports {JA[4]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JA[4]}] ##Sch name = JA8 #set_property PACKAGE_PIN K2 [get_ports {JA[5]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JA[5]}] ##Sch name = JA9 #set_property PACKAGE_PIN H2 [get_ports {JA[6]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JA[6]}] ##Sch name = JA10 #set_property PACKAGE_PIN G3 [get_ports {JA[7]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JA[7]}] ##Pmod Header JB ##Sch name = JB1 #set_property PACKAGE_PIN A14 [get_ports {JB[0]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JB[0]}] ##Sch name = JB2 #set_property PACKAGE_PIN A16 [get_ports {JB[1]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JB[1]}] ##Sch name = JB3 #set_property PACKAGE_PIN B15 [get_ports {JB[2]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JB[2]}] ##Sch name = JB4 #set_property PACKAGE_PIN B16 [get_ports {JB[3]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JB[3]}] ##Sch name = JB7 #set_property PACKAGE_PIN A15 [get_ports {JB[4]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JB[4]}] ##Sch name = JB8 #set_property PACKAGE_PIN A17 [get_ports {JB[5]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JB[5]}] ##Sch name = JB9 #set_property PACKAGE_PIN C15 [get_ports {JB[6]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JB[6]}] ##Sch name = JB10 #set_property PACKAGE_PIN C16 [get_ports {JB[7]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JB[7]}] ##Pmod Header JC ##Sch name = JC1 #set_property PACKAGE_PIN K17 [get_ports {JC[0]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JC[0]}] ##Sch name = JC2 #set_property PACKAGE_PIN M18 [get_ports {JC[1]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JC[1]}] ##Sch name = JC3 #set_property PACKAGE_PIN N17 [get_ports {JC[2]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JC[2]}] ##Sch name = JC4 #set_property PACKAGE_PIN P18 [get_ports {JC[3]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JC[3]}] ##Sch name = JC7 #set_property PACKAGE_PIN L17 [get_ports {JC[4]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JC[4]}] ##Sch name = JC8 #set_property PACKAGE_PIN M19 [get_ports {JC[5]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JC[5]}] ##Sch name = JC9 #set_property PACKAGE_PIN P17 [get_ports {JC[6]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JC[6]}] ##Sch name = JC10 #set_property PACKAGE_PIN R18 [get_ports {JC[7]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JC[7]}] ##Pmod Header JXADC ##Sch name = XA1_P #set_property PACKAGE_PIN J3 [get_ports {vauxp6}] # set_property IOSTANDARD LVCMOS33 [get_ports {vauxp6}] ##Sch name = XA2_P #set_property PACKAGE_PIN L3 [get_ports {vauxp14}] # set_property IOSTANDARD LVCMOS33 [get_ports {vauxp14}] ##Sch name = XA3_P #set_property PACKAGE_PIN M2 [get_ports {vauxp7}] # set_property IOSTANDARD LVCMOS33 [get_ports {vauxp7}] ##Sch name = XA4_P #set_property PACKAGE_PIN N2 [get_ports {vauxp15}] # set_property IOSTANDARD LVCMOS33 [get_ports {vauxp15}] ##Sch name = XA1_N #set_property PACKAGE_PIN K3 [get_ports {vauxn6}] # set_property IOSTANDARD LVCMOS33 [get_ports {vauxn6}] ##Sch name = XA2_N #set_property PACKAGE_PIN M3 [get_ports {vauxn14}] # set_property IOSTANDARD LVCMOS33 [get_ports {vauxn14}] #Sch name = XA3_N #set_property PACKAGE_PIN M1 [get_ports {vauxn7}] # set_property IOSTANDARD LVCMOS33 [get_ports {vauxn7}] #Sch name = XA4_N #set_property PACKAGE_PIN N1 [get_ports {vauxn15}] # set_property IOSTANDARD LVCMOS33 [get_ports {vauxn15}] ##VGA Connector #set_property PACKAGE_PIN G19 [get_ports {vgaRed[0]}] #set_property IOSTANDARD LVCMOS33 [get_ports {vgaRed[0]}] #set_property PACKAGE_PIN H19 [get_ports {vgaRed[1]}] #set_property IOSTANDARD LVCMOS33 [get_ports {vgaRed[1]}] #set_property PACKAGE_PIN J19 [get_ports {vgaRed[2]}] #set_property IOSTANDARD LVCMOS33 [get_ports {vgaRed[2]}] #set_property PACKAGE_PIN N19 [get_ports {vgaRed[3]}] #set_property IOSTANDARD LVCMOS33 [get_ports {vgaRed[3]}] #set_property PACKAGE_PIN N18 [get_ports {vgaBlue[0]}] #set_property IOSTANDARD LVCMOS33 [get_ports {vgaBlue[0]}] #set_property PACKAGE_PIN L18 [get_ports {vgaBlue[1]}] #set_property IOSTANDARD LVCMOS33 [get_ports {vgaBlue[1]}] #set_property PACKAGE_PIN K18 [get_ports {vgaBlue[2]}] #set_property IOSTANDARD LVCMOS33 [get_ports {vgaBlue[2]}] #set_property PACKAGE_PIN J18 [get_ports {vgaBlue[3]}] #set_property IOSTANDARD LVCMOS33 [get_ports {vgaBlue[3]}] #set_property PACKAGE_PIN J17 [get_ports {vgaGreen[0]}] #set_property IOSTANDARD LVCMOS33 [get_ports {vgaGreen[0]}] #set_property PACKAGE_PIN H17 [get_ports {vgaGreen[1]}] #set_property IOSTANDARD LVCMOS33 [get_ports {vgaGreen[1]}] #set_property PACKAGE_PIN G17 [get_ports {vgaGreen[2]}] #set_property IOSTANDARD LVCMOS33 [get_ports {vgaGreen[2]}] #set_property PACKAGE_PIN D17 [get_ports {vgaGreen[3]}] #set_property IOSTANDARD LVCMOS33 [get_ports {vgaGreen[3]}] #set_property PACKAGE_PIN P19 [get_ports Hsync] #set_property IOSTANDARD LVCMOS33 [get_ports Hsync] #set_property PACKAGE_PIN R19 [get_ports Vsync] #set_property IOSTANDARD LVCMOS33 [get_ports Vsync] ##USB-RS232 Interface #set_property PACKAGE_PIN B18 [get_ports RsRx] #set_property IOSTANDARD LVCMOS33 [get_ports RsRx] #set_property PACKAGE_PIN A18 [get_ports RsTx] #set_property IOSTANDARD LVCMOS33 [get_ports RsTx] ##USB HID (PS/2) #set_property PACKAGE_PIN C17 [get_ports PS2Clk] #set_property IOSTANDARD LVCMOS33 [get_ports PS2Clk] #set_property PULLUP true [get_ports PS2Clk] #set_property PACKAGE_PIN B17 [get_ports PS2Data] #set_property IOSTANDARD LVCMOS33 [get_ports PS2Data] #set_property PULLUP true [get_ports PS2Data] ##Quad SPI Flash ##Note that CCLK_0 cannot be placed in 7 series devices. You can access it using the ##STARTUPE2 primitive. #set_property PACKAGE_PIN D18 [get_ports {QspiDB[0]}] #set_property IOSTANDARD LVCMOS33 [get_ports {QspiDB[0]}] #set_property PACKAGE_PIN D19 [get_ports {QspiDB[1]}] #set_property IOSTANDARD LVCMOS33 [get_ports {QspiDB[1]}] #set_property PACKAGE_PIN G18 [get_ports {QspiDB[2]}] #set_property IOSTANDARD LVCMOS33 [get_ports {QspiDB[2]}] #set_property PACKAGE_PIN F18 [get_ports {QspiDB[3]}] #set_property IOSTANDARD LVCMOS33 [get_ports {QspiDB[3]}] #set_property PACKAGE_PIN K19 [get_ports QspiCSn] #set_property IOSTANDARD LVCMOS33 [get_ports QspiCSn]

4.综合,执行,生成比特流文件。

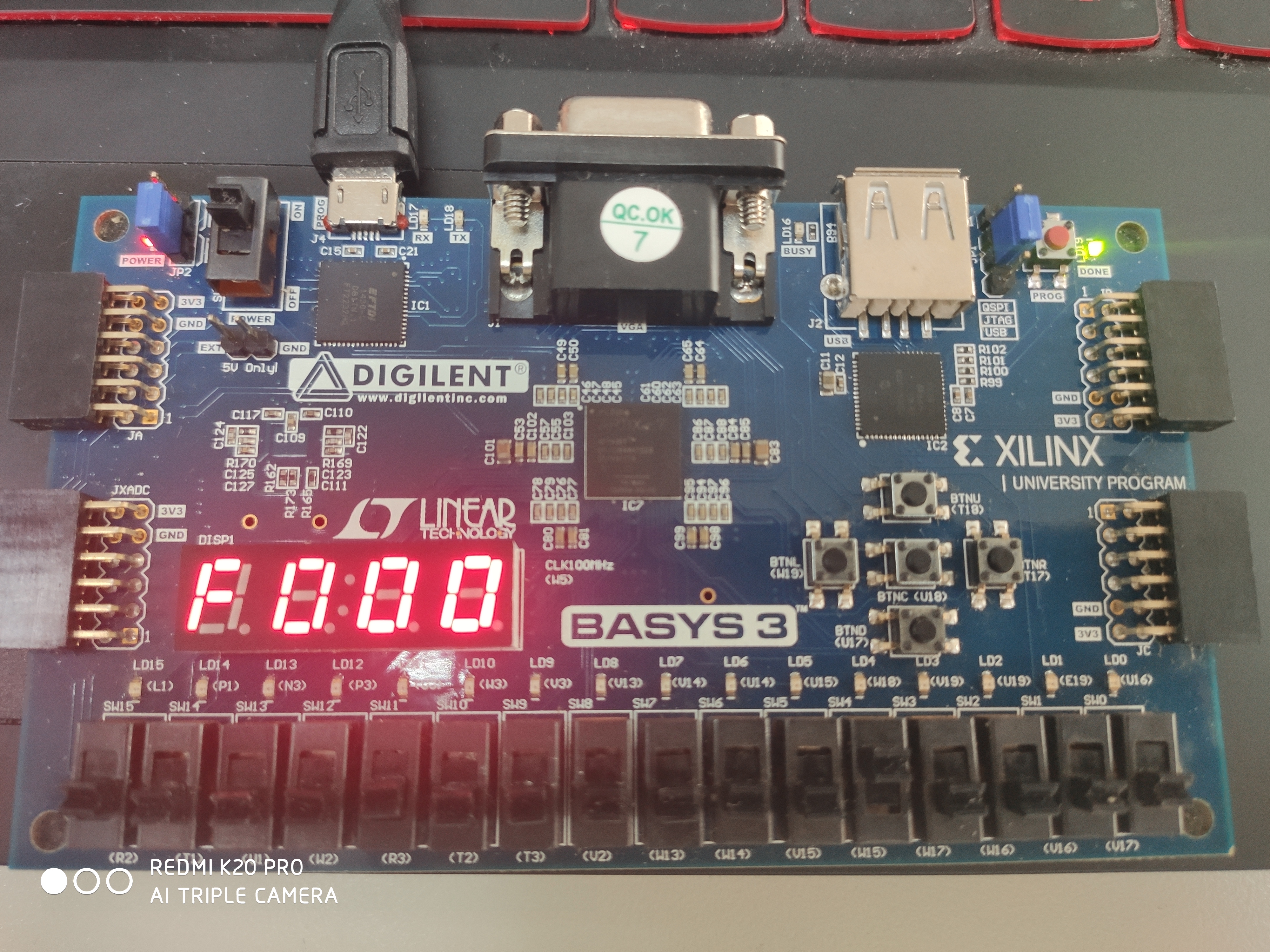

5.打开硬件管理器,连接电路板,将代码加载到板子上。

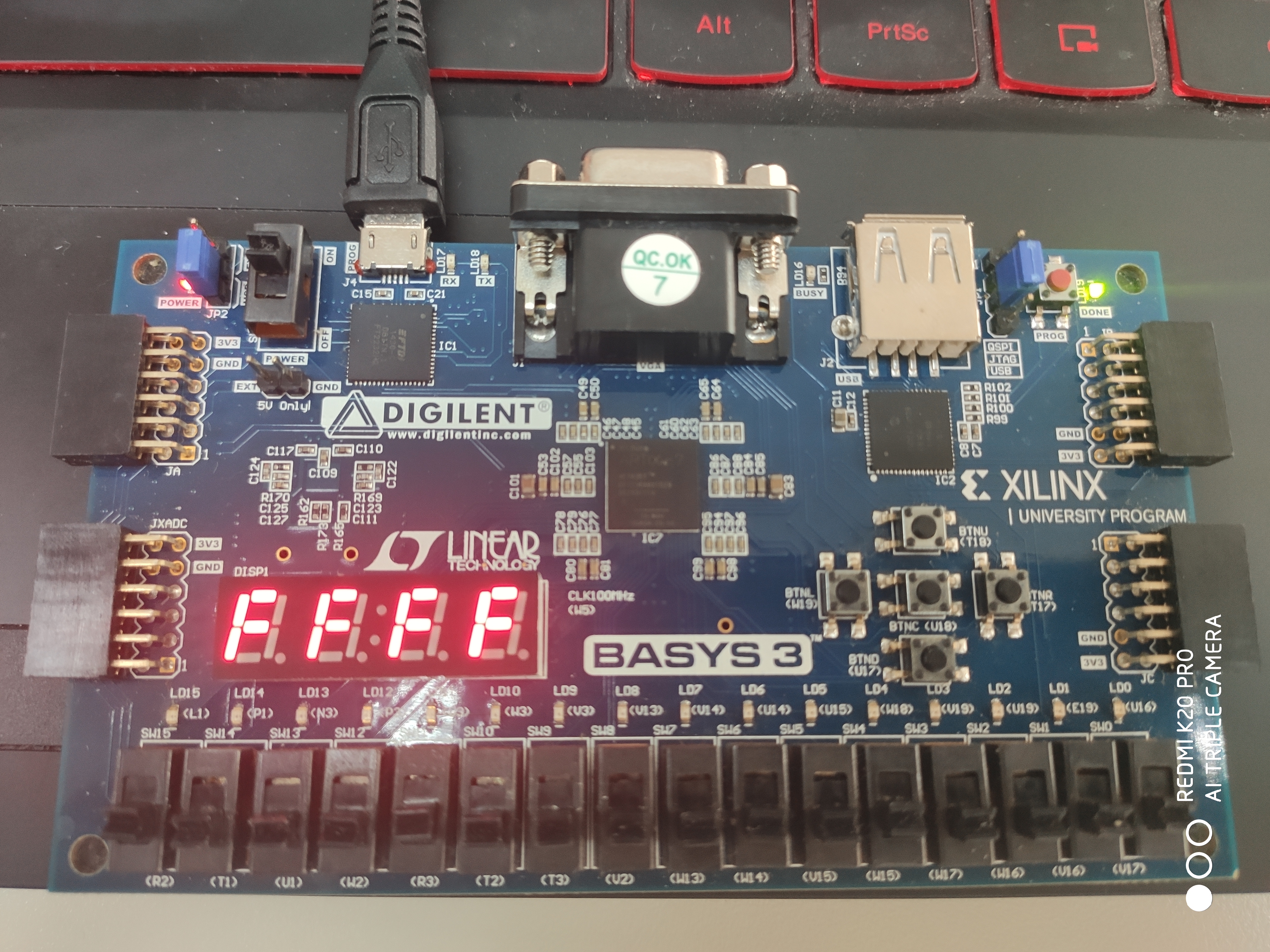

6.观察板子上数码管效果。

可以看到,显示内容与coe文件中的数后4位一致。