(环境:Vivado 2017.4)

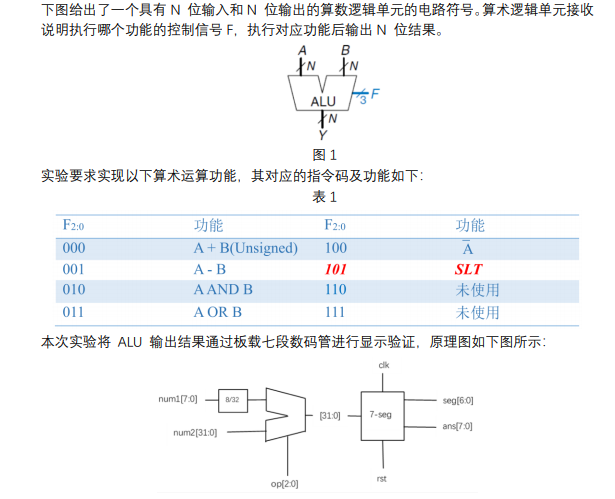

实验要求:

实验过程:

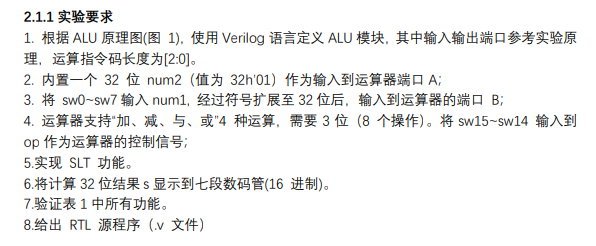

1.打开Vivado,创建文件,选择xc7a35tcpg236-1核。

2.添加源文件。

calculate模块:

module calculate( input wire [7:0] num1, input wire [2:0] op, output reg [31:0] result ); wire [31:0] num2; wire [31:0] Sign_extend; assign num2=32'h01; assign Sign_extend={24'b0,num1}; always@(*)begin if(op == 3'b000) result=num2+Sign_extend; else if(op==3'b001) result=num2-Sign_extend; else if(op==3'b010) result=Sign_extend&num2; else if(op==3'b011) result=Sign_extend|num2; else if(op==3'b100) result=~num2; else if(op==3'b101) result=(num2<Sign_extend)?1:0; end endmodule

display模块:

module display( input wire clk,reset, input wire [31:0]s, output wire [6:0]seg, output reg [3:0]ans ); reg [20:0]count; reg [4:0]digit; always@(posedge clk,posedge reset) if(reset) count = 0; else count = count + 1; always @(posedge clk) case(count[20:19]) 0:begin ans = 4'b1110; digit = s[3:0]; end 1:begin ans = 4'b1101; digit = s[7:4]; end 2:begin ans = 4'b1011; digit =s[11:8]; end 3:begin ans = 4'b0111; digit = s[15:12]; end endcase seg7 U4(.din(digit),.dout(seg)); endmodule

seg7模块:

module seg7( input wire [3:0]din, output reg [6:0]dout ); always@(*) case(din) 5'h0:dout = 7'b000_0001; 5'h1:dout = 7'b100_1111; 5'h2:dout = 7'b001_0010; 5'h3:dout = 7'b000_0110; 5'h4:dout = 7'b100_1100; 5'h5:dout = 7'b010_0100; 5'h6:dout = 7'b010_0000; 5'h7:dout = 7'b000_1111; 5'h8:dout = 7'b000_0000; 5'h9:dout = 7'b000_0100; 5'ha:dout = 7'b000_1000; 5'hb:dout = 7'b110_0000; 5'hc:dout = 7'b011_0001; 5'hd:dout = 7'b100_0010; 5'he:dout = 7'b011_0000; 5'hf:dout = 7'b011_1000; default:dout = 7'b111_1111; endcase endmodule

顶层模块:

module top( input clk, input rst, input [2:0] op, input [7:0] num1, output [3:0] ans, //select for seg output [6:0] seg //segment digital ); wire [31:0] s; calculate U1(.num1(num1),.op(op),.result(s)); display U2(.clk(clk),.reset(rst),.s(s),.ans(ans),.seg(seg)); endmodule

管脚约束文件:

set_property PACKAGE_PIN W5 [get_ports clk] set_property IOSTANDARD LVCMOS33 [get_ports clk] create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports clk] set_property PACKAGE_PIN V16 [get_ports {op[0]}] set_property IOSTANDARD LVCMOS33 [get_ports {op[0]}] set_property PACKAGE_PIN W16 [get_ports {op[1]}] set_property IOSTANDARD LVCMOS33 [get_ports {op[1]}] set_property PACKAGE_PIN W17 [get_ports {op[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {op[2]}] set_property PACKAGE_PIN W15 [get_ports {num1[0]}] set_property IOSTANDARD LVCMOS33 [get_ports {num1[0]}] set_property PACKAGE_PIN V15 [get_ports {num1[1]}] set_property IOSTANDARD LVCMOS33 [get_ports {num1[1]}] set_property PACKAGE_PIN W14 [get_ports {num1[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {num1[2]}] set_property PACKAGE_PIN W13 [get_ports {num1[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {num1[3]}] set_property PACKAGE_PIN V2 [get_ports {num1[4]}] set_property IOSTANDARD LVCMOS33 [get_ports {num1[4]}] set_property PACKAGE_PIN T3 [get_ports {num1[5]}] set_property IOSTANDARD LVCMOS33 [get_ports {num1[5]}] set_property PACKAGE_PIN T2 [get_ports {num1[6]}] set_property IOSTANDARD LVCMOS33 [get_ports {num1[6]}] set_property PACKAGE_PIN R3 [get_ports {num1[7]}] set_property IOSTANDARD LVCMOS33 [get_ports {num1[7]}] set_property PACKAGE_PIN W7 [get_ports {seg[6]}] set_property IOSTANDARD LVCMOS33 [get_ports {seg[6]}] set_property PACKAGE_PIN W6 [get_ports {seg[5]}] set_property IOSTANDARD LVCMOS33 [get_ports {seg[5]}] set_property PACKAGE_PIN U8 [get_ports {seg[4]}] set_property IOSTANDARD LVCMOS33 [get_ports {seg[4]}] set_property PACKAGE_PIN V8 [get_ports {seg[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {seg[3]}] set_property PACKAGE_PIN U5 [get_ports {seg[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {seg[2]}] set_property PACKAGE_PIN V5 [get_ports {seg[1]}] set_property IOSTANDARD LVCMOS33 [get_ports {seg[1]}] set_property PACKAGE_PIN U7 [get_ports {seg[0]}] set_property IOSTANDARD LVCMOS33 [get_ports {seg[0]}] set_property PACKAGE_PIN U2 [get_ports {ans[0]}] set_property IOSTANDARD LVCMOS33 [get_ports {ans[0]}] set_property PACKAGE_PIN U4 [get_ports {ans[1]}] set_property IOSTANDARD LVCMOS33 [get_ports {ans[1]}] set_property PACKAGE_PIN V4 [get_ports {ans[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {ans[2]}] set_property PACKAGE_PIN W4 [get_ports {ans[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {ans[3]}] set_property PACKAGE_PIN U18 [get_ports rst] set_property IOSTANDARD LVCMOS33 [get_ports rst]

3.综合,执行,生成比特流文件。

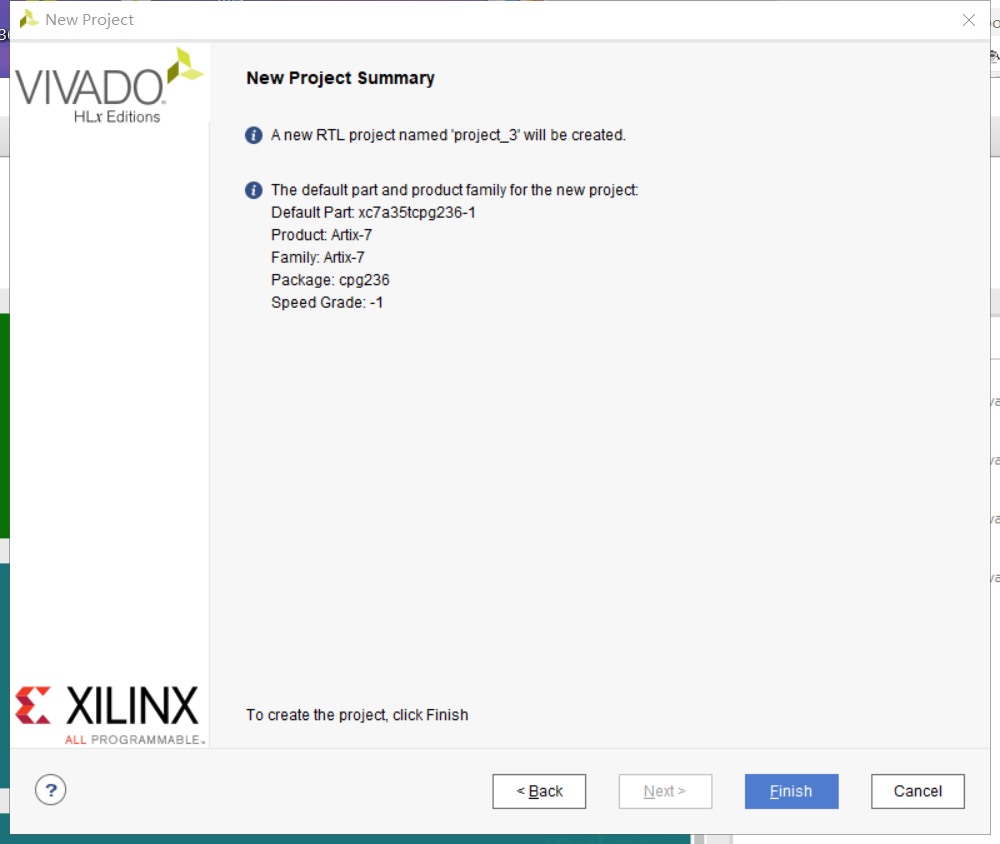

4.打开硬件管理器,连接电路板,将代码加载到板子上。

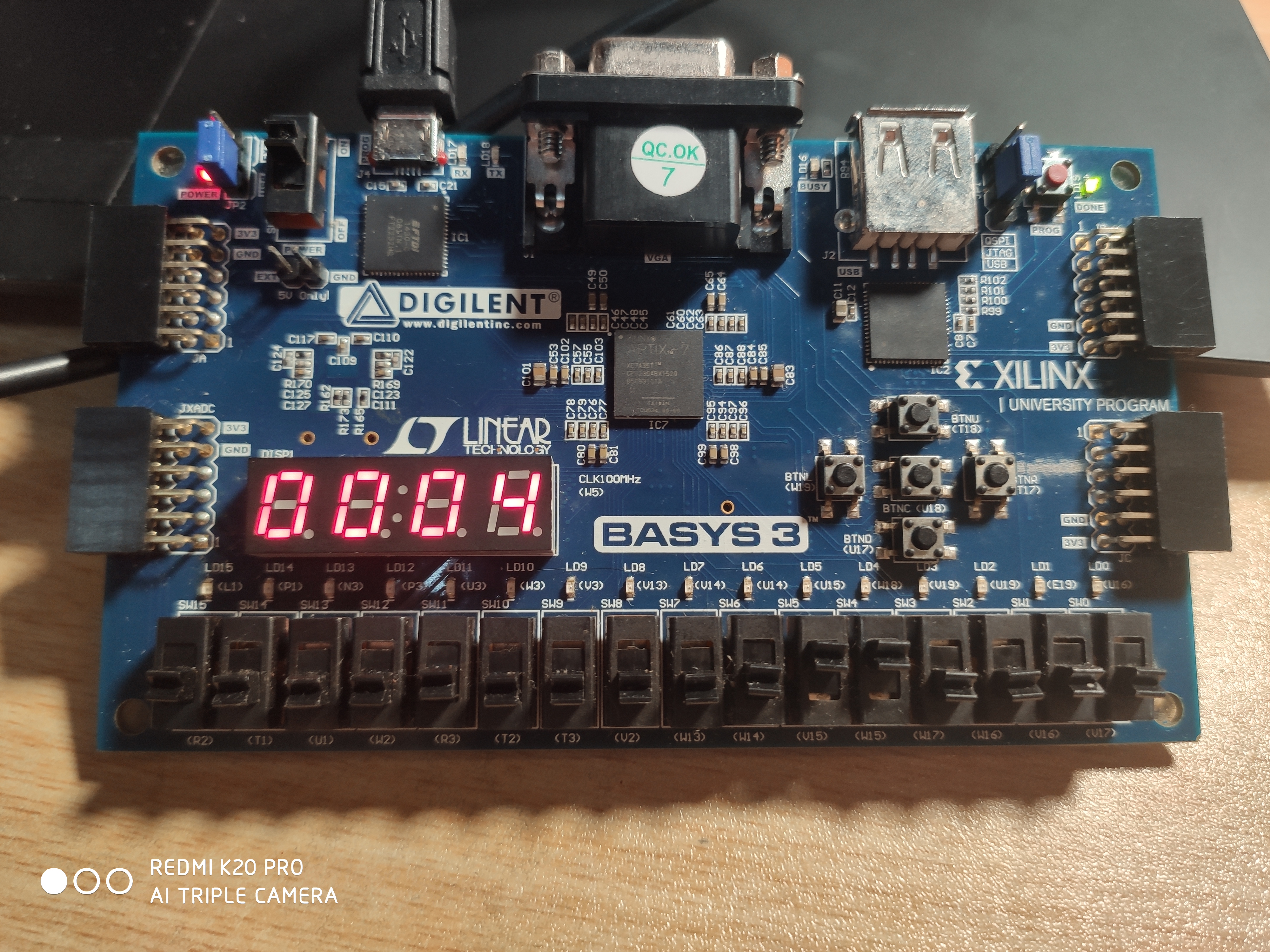

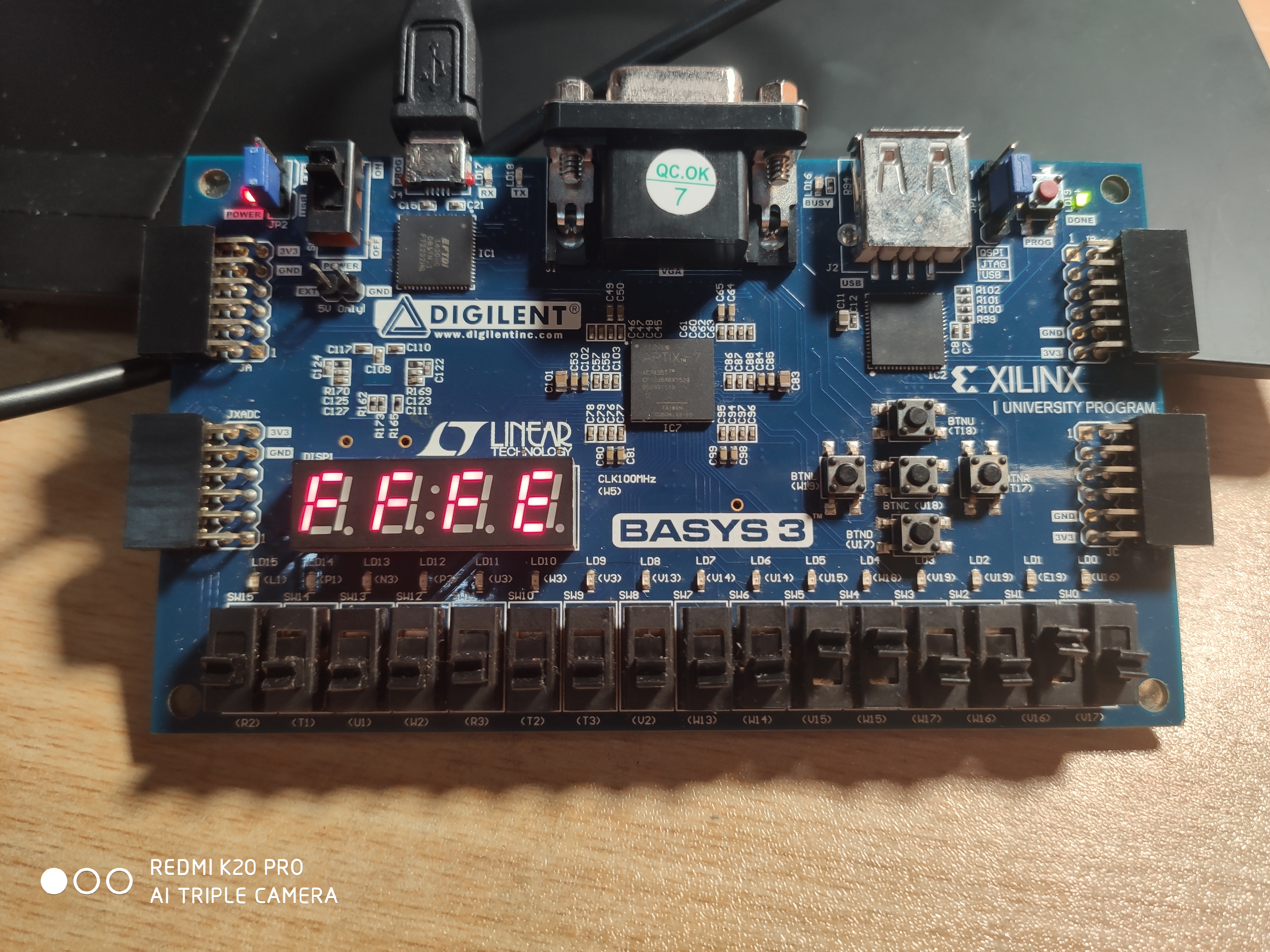

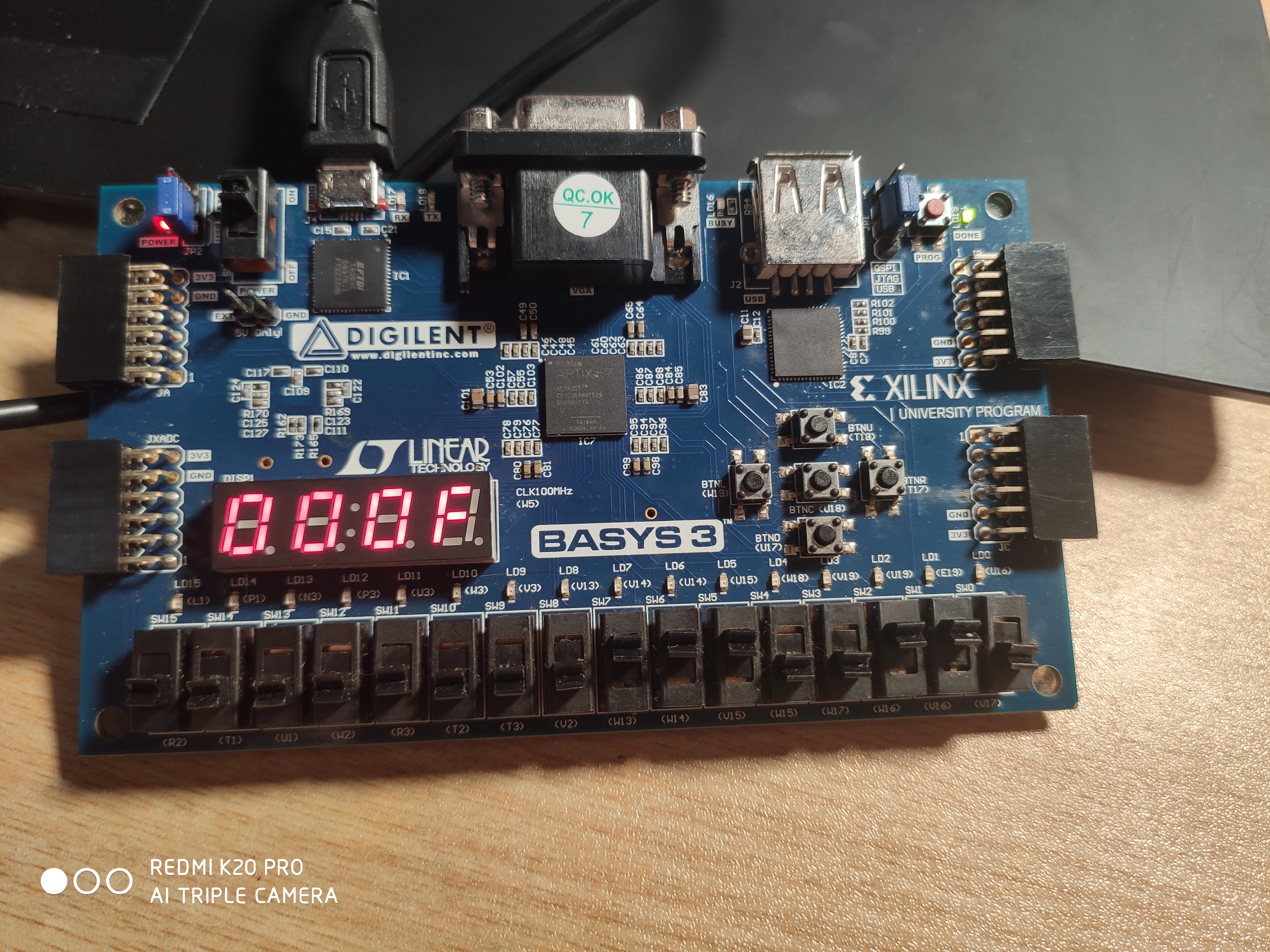

5.观察板子上数码管效果。(图片光线较差,见谅)

加法:

减法:

或运算:

其他可自己试验。