在 20nm 以下的工艺中,由于相邻 metal wire 的间距太小,使得光刻过程中,相邻的光线间距过小,相互之间发生干涉,导致 metal wire 边缘模糊,出现瑕疵。

为了解决这个问题,先进工艺开始采用 double pattern(DPT),也称为 double mask,就是将原来的一层 mask 拆分成两层,在每一层 mask 中都不出现最小间距,才能保证制造不出现瑕疵,代价就是制造费用成倍增加,原来只需一层光罩的费用,现在需要两层。

图1. 拆分成两组 mask

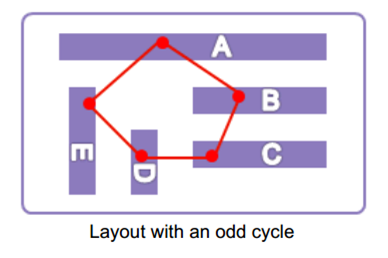

相应地,在芯片物理设计过程中,需要确保每层metal 都可以拆分成两层 mask,如果出现无法拆分的情况,就会报 odd cycle drc

什么样的情况无法拆分?

如下图所示,在这个区域内有 5 条 metal (奇数条),如果所有相邻的 metal 间距都小于 DPT 规定的最小间距(DPTminSpacing),就会出现无法拆分的情况

划重点:奇数条 metal ,相邻间距都小于 DPTminSpacing

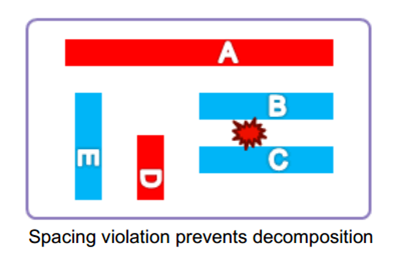

假设拆分为 AD 和 BCE,如下图,由于 BC 间距小于double pattern 规定的最小 spacing,无法制造!

可能有人会问,为什么不拆分成 ACE 和 BD? 这样 BC 之间不就没问题了吗?

实际上由于 AE 间距也小于 double pattern 规定的最小 spacing,也无法制造!

(这里要强调这个区域内所有相邻的 metal wire spacing 都小于 DBT 规定的最小spacing)

所以这个 mask 无法拆成两个满足要求的 mask,ICC2 会检测到这种问题,并且报 odd cycle drc error

如何解决 odd cycle drc error ?

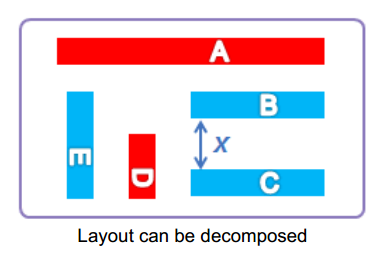

很简单,拉开 spacing 即可,以刚才的图为例,拉开 BC 间的 spacing:

这样,可以拆分成 AD 和 BCE 两组,两组 mask 都满足 DPT 最小 spacing 要求了

怎样快速判断某个区域是否存在 odd cycle drc error ?

随机选取一根 metal 线作为第一根,如果第一根线与第二根线是最小间距,就要检查是否有第三根线与第二根线是最小间距,如果有,接着去找第四根,如果找到第 n 根,且第 n 根与第一根也是最小间距,那么就构成了一个闭合环路,这样一组 metal 就叫做 “ 最小间距环 ”,这个 n 如果是奇数,那就一定会出现 odd cycle error !!

顾名思义, odd cycle 就是指这个 “ 奇数环 ” 。

ICC2 就是先找出这些 “ 最小间距环 ” ,然后检查是否是奇数。

如果 ICC2 检测到 “奇数环”,会自动修掉,但是检测难点在于,这个环可能非常大,如果检测窗口不够大,就检测不到,这时候就需要手动介入修掉了。

其它相关:

1). DPT 一般应用于低层 metal ,比如 M2 M3 等,因为先进工艺 cell 出 pin 更加密集,需要更多的低层绕线资源,低层 metal 方便连接底层 cell pin

2). 采用 DPT 的 metal layer 绕线利用率不宜太高,一般默认设定在 60% 左右,因为密度越高,出现 odd cycle 的几率越大

3). DPT 的最小spacing 要求一般可以在 tech file 中查到,比如在某厂商 10nm 工艺中,M2 是DPT layer,其 minSpacing = 0.024u,其 DPTminSpacing = 0.072u (side2side),而对于不是DPT 的layer, 其 minSpacing = 0.04u

4). 同一层的 metal 尽量不要出现拐弯,拐弯就意味着这条metal至少占用了两条 track,更容易出现 odd cycle

|---------------------------|