本博文以矩阵键盘实验为例,介绍了如何开启FPGA管脚的片上上拉电阻。

Cyclone IV E FPGA的通用输入输出管脚都支持内部弱上拉电阻,但是时钟输入脚不支持。所以,当需要上拉电阻的信号(如本例中的矩阵键盘Row信号和IIC协议中的SDA、SCL信号)连接到了FPGA的通用输入输出管脚上,在一些要求不高的场合,就可以使用片上上拉电阻来为这些信号设置上拉了。

分配引脚并设置row上拉电阻详细方式

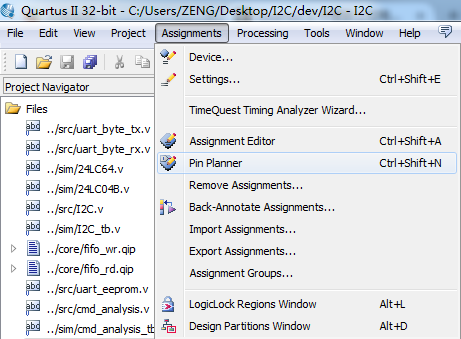

1. 如下图所示,在菜单 Assignments 中选择 Pin Planner,也可以直接点击面板上引脚分配的图标;

(温馨提醒:如图片看不清楚,可以选中图片点击右键,在新窗口中打开该图片以查看高清大图)

图 进入引脚分配界面选项

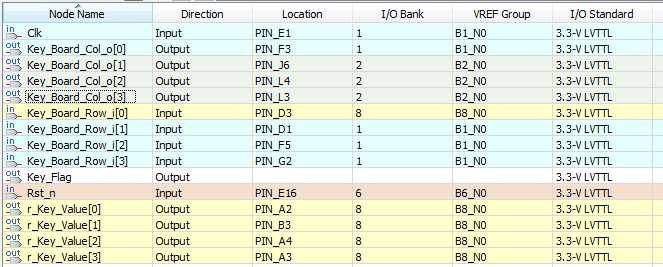

2.进入引脚分配的界面之后,按照上面给出的矩阵键盘与AC620板卡的连接关系以及引脚分配情况,完成引脚分配工作,Starter板卡用户请按照Starter板引脚分配关系分配,并将Key_Value的4位信号分别连接到4位LED上,以方便通过LED的亮灭值确定按键的值。

(温馨提醒:如图片看不清楚,可以选中图片点击右键,在新窗口中打开该图片以查看高清大图)

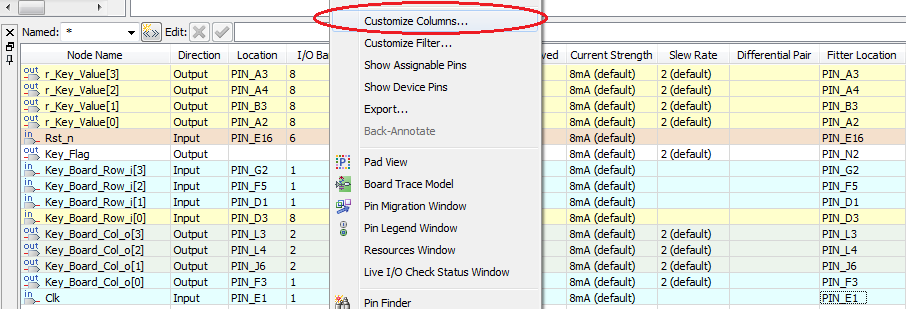

3.在弹出的Pin Planner界面的All Pins区域里任意位置点击鼠标右键,找到 Customize Columns并点击进入,如下图所示;

(温馨提醒:如图片看不清楚,可以选中图片点击右键,在新窗口中打开该图片以查看高清大图)

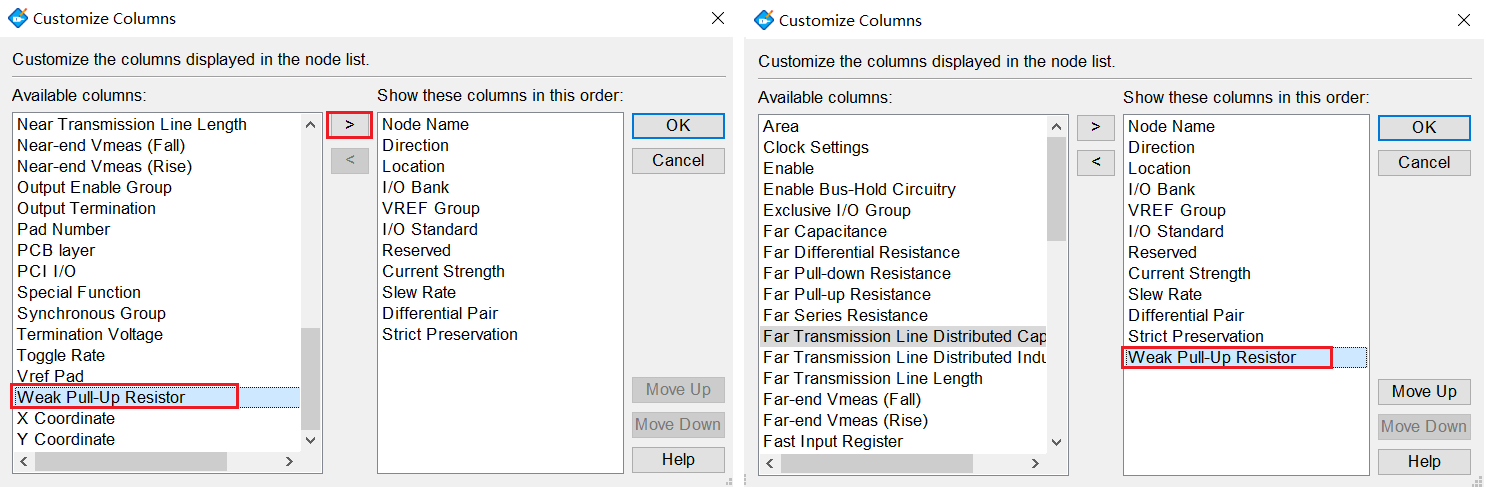

4. 在弹出的Customize Columns对话框的左列表框选择Weak Pull-Up Resistor,如图下图所示,再点击和大于号(>)一样的图标,这样把Weak Pull-Up Resistor添加到右列表框,最后点击OK。

(温馨提醒:如图片看不清楚,可以选中图片点击右键,在新窗口中打开该图片以查看高清大图)

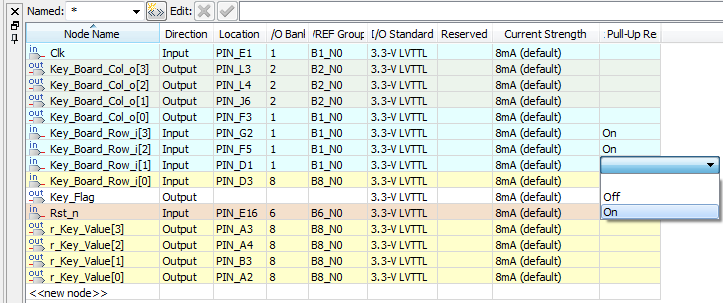

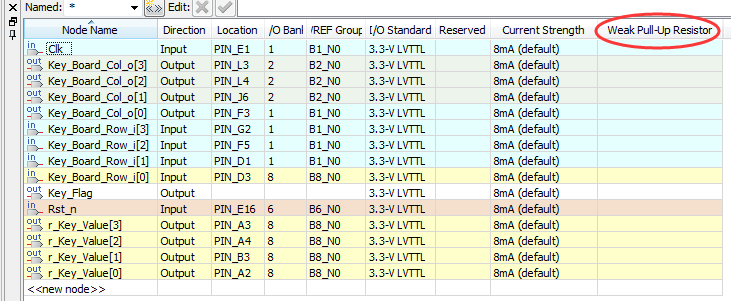

5. 经过步骤4后,在引脚分配界面就会多出一个Weak Pull-Up Resistor列,如下图所示:

(温馨提醒:如图片看不清楚,可以选中图片点击右键,在新窗口中打开该图片以查看高清大图)

6.再把需要上拉的Row0~Row3对应WeakPull-Up Resistor的位置双击鼠标左键,就会弹出一个Off/On的选项,选上On就可以了。

(温馨提醒:如图片看不清楚,可以选中图片点击右键,在新窗口中打开该图片以查看高清大图)