芯航线——普利斯队长精心奉献

实验目的:以计数器为例学会简单的时序逻辑电路设计

实验平台:芯航线FPGA核心板

实验原理:

时序逻辑电路是指电路任何时刻的稳态输出不仅取决于当前的输入,还与前一时刻输入形成的状态有关。这跟组合逻辑电路相反,组合逻辑的输出只会跟目前的输入成一种函数关系。换句话说,时序逻辑拥有储存元件(内存)来存储信息,而组合逻辑则没有。

计数器的核心元件是触发器,基本功能是对脉冲进行计数,其所能记忆脉冲最大的数目称为该计数器的模/值,常用在分频、定时等处。计数器的种类很多,按照计数方式的不同可以分为二进制计数器、十进制计数器以及任意进制计数器,按照触发器的时钟脉冲信号来源可分为同步计数器与异步计数器。按照计数增减可分为加法计数器、减法计数器以及可逆计数器。

此处设计一个计数器,使其使能板载LED每500ms,状态翻转一次。核心板晶振为50MHz,也就是说时钟周期为20ns,这样可以计算得出500ms = 500_000_000ns/20 = 25_000_000;即需要计数器计数25_000_000次,也就是需要一个至少25位的计数器。且每当计数次数达到需要清零并重新计数。

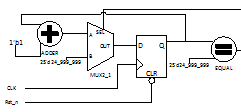

VerilogHDL之所以被称为硬件电路描述语言,就是因为我们不是在类似C一样进行普通的编程,我们是在编写一个实际的硬件电路,例如02中设计的一个二选一选择器最后就是被综合称为一个真正的选择器。上面提到计数器即为加法器、比较器、寄存器以及选择器构成,如图4-1所示。

图4-1 计数器逻辑电路图

实验内容:

按照02章所讲,建立工程子文件夹后,新建一个以名为counter的工程保存在prj下,并在本工程目录的rtl文件夹下新建verilog file文件在此文件下输入以下内容并以counter.v保存。这里之所以在计数值计数到25'd24_999_999而不是25'd25_000_000是因为计数器是从0开始计数而不是1。这里每当计数器计数到预设的值后就让led取反一次。

|

module counter(Clk50M,Rst_n,led);

input Clk50M; //系统时钟,50M input Rst_n; //全局复位,低电平复位

output reg led; //led输出

reg [24:0]cnt; //定义计数器寄存器

//计数器计数进程 always@(posedge Clk50M or negedge Rst_n) if(Rst_n == 1'b0) cnt <= 25'd0; else if(cnt == 25'd24_999_999) cnt <= 25'd0; else cnt <= cnt + 1'b1;

//led输出控制进程 always@(posedge Clk50M or negedge Rst_n) if(Rst_n == 1'b0) led <= 1'b1; else if(cnt == 25'd24_999_999) led <= ~led; else led <= led;

endmodule |

进行分析和综合直至没有错误以及警告。

为了测试仿真编写测试激励文件,新建counter_tb.v文件并输入以下内容再次进行分析和综合直至没有错误以及警告,保存到testbench文件夹下。这里生成了一个周期为20ns的时钟clk,并且例化了需要测试的counter.v。

|

`timescale 1ns/1ns `define clock_period 20 module counter_tb; reg clk; reg rst_n;

wire led;

counter counter0( .Clk50M(clk), .Rst_n(rst_n), .led(led) );

initial clk = 1; always #(`clock_period/2) clk = ~clk;

initial begin rst_n = 1'b0; #(`clock_period *200); rst_n = 1'b1; #2000000000; $stop; end

endmodule |

设置好仿真脚本后进行功能仿真,可以看到如图3-2所示的波形文件,可以看出高低电平变化的时间均是0.5s也就是500ms,得出符合既定的设计要求,至此功能仿真结束。

图3-2 功能仿真波形文件

在进行上述的功能仿真时可以发现需要仿真时间较长,这是由于将计数器的计数值太大,因此可以将counter.v的cnt计数值修改为24_999来减少仿真时间,这时会发现仿真时间大幅度缩短,且图3-3中高低电平变化时间变为500_000ns,相比500ms缩短了1000倍,也可以说明功能仿真正确。

图3-3 缩小计数值后的功能仿真波形

进行全编译后进行门级仿真,可以看到如图3-4所示波形图,在这可以看出由于门电路的延迟高低电平变化时间并不严格等于0.5s。

图3-4 时序仿真波形

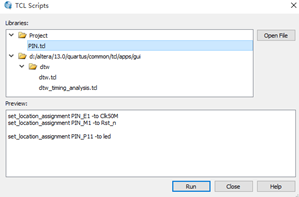

现进行分配引脚,此处介绍另一种分配引脚的方式,采用tcl文件。首先在File—New中选中Tcl Script File,新建一个tcl文件。并输入以下内容后以PIN.tcl名称保存到prj文件夹下。此处由于不同批次可能会引脚分配略有不同,请根据对应的引脚表来编写。

图3-5 新建tcl文件

|

set_location_assignment PIN_E1 -to Clk50M set_location_assignment PIN_M1 -to Rst_n

set_location_assignment PIN_P11 -to led |

然后单击Tools--Tcl Script,弹出图3-7对话框后选中编写好的PIN.tcl文件,点击Open Files编写的内容就会出现在下面的框图中,此时再点击Run会弹出图3-8对话框,提示已经运行完毕。我们这时可以打开Pin planer查看分配好的引脚。

图3-7 设置Tcl脚本

图3-8运行Tcl脚本

图3-9 脚本运行成功

全编译后可以在RTL viewer中可以看到图3-10所示的硬件逻辑电路,也存在前面讲到的加法器、比较器、寄存器以及选择器构成的计数器。下载到开发板中可以看到图3-11现象,LED0以500ms的时间进行闪烁,如果有示波器也可以测量这时候的引脚波形进行观察。

图3-10 RTL viewer

图3-11 实验现象

至此,就完成了一个基本的时序逻辑,计数器的设计。请以此为基础自行设计使得每个灯以不同的频率闪烁,并进行仿真以及板级验证。