基本概念

1、名词解释

锁存器(latch)是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,尽当锁存器处于使能状态时,输出才会随着数据输入发生变化。

触发器(flipflop)是边沿敏感的存储单元,数据存储的动作由某一信号的上升或者下降沿行同步的。(钟控D触发器其实就是D锁存器,边沿D触发器才是真正的D触发器)

寄存器(register)是用来暂时存放参与运算的数据和运算结果。在实际的数字系统中,通常把能够用来存储一组二进制代码的同步时序逻辑电路称为寄存器。

2、锁存器和触发器的区别

锁存器同其所有的输入信号相关,是电平触发,当输入信号变化时锁存器就变化,没有时钟端,属于异步电路设计,时序分析困难且浪费大量芯片资源。

触发器受时钟控制的边沿触发,只有在时钟触发时才采样当前的输入产生输出,当然因为锁存器和触发器二者都是时序逻辑,所以输出不但同当前的输入相关,还同上一时间的输出相关。

3、触发器、锁存器、寄存器的区别?

由于触发器内有记忆功能,因此利用触发器可以方便地构成寄存器。由于一个触发器能够存储一位二进制码,所以把n个触发器的时钟端口连接起来就能构成一个存储n位二进制码的寄存器。从寄存数据的角度来讲,寄存器和锁存器的功能是相同的;它们的区别在于寄存器是同步时钟控制,而锁存器是电位信号控制。

4、锁存器有哪些缺点?

锁存器在不锁存数据时,输出端的信号随输入信号变化,就像信号通过一个缓存器一样;一旦锁存信号起锁存作用,则数据被锁住,输入信号不起作用。因此锁存器也称为透明锁存器,指的是不锁存时输出对输入是透明的。此外锁存器还有以下一些缺点:

(1)对毛刺敏感,不能异步复位,所以上电后处于不确定的状态。

(2)锁存器会使静态时序分析变得非常复杂。

(3)在 FPGA 中,基本的单元时由查找表和触发器组成的,若生成锁存器反而需要更 多的资源。

5、触发器有哪些类型?

根据逻辑功能不同:RS触发器、D触发器、JK触发器、T触发器和T'触发器等。

根据触发方式不同:电平触发器、边沿触发器和主从触发器等。

根据电路结构不同:基本RS触发器,同步触发器、维持阻塞触发器、主从触发器和边沿触发器等。

D锁存器和D触发器专题

1、D锁存器

所谓的 D 锁存器,就是能够将输入的单路数据D存入到锁存器中的电路,D锁存器的电路图如下图所示:

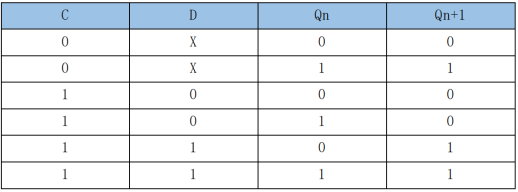

D锁存器的特性表如下所示,Qn指触发前的状态,Qn+1指触发后的状态。

当CLk为0时,Qn+1=Qn,即保持之前的状态;

当CLK为1时,Qn+1=D,即状态由D来决定;

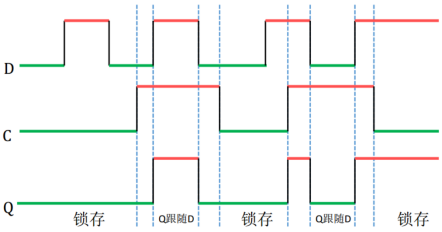

现在来看一下波形,在以后的设计中的Q实际上是Qn+1,不要搞错了!这里要多说一点,很多书介绍D锁存器时喜欢将C写成CLK,实际上大多时候这个地方不是CLK。

从 D 锁存器的波形图图中我们可以看出,D 是锁存器的输入信号,C 是锁存器的控制信号,Q 是锁存器的输出信号,当控制信号 C 为高电平时,输出信号 Q 将跟随输入信号 D 的变化而变化,大家看虚线内,Q 的波形等于 D 的波形。当控制信号 C 从高电平变为低电平时,输入信号 D 的状态将会决定锁存器将要锁存的状态。大家可以看到,C 由高变低的那两条虚线内,所对应的输入信号 D 为低电平,那么输出信号 Q 也将会锁存低电平。最后面的那两条虚线也同理,D 为高电平,Q 锁存高电平。

2、锁存器坏处

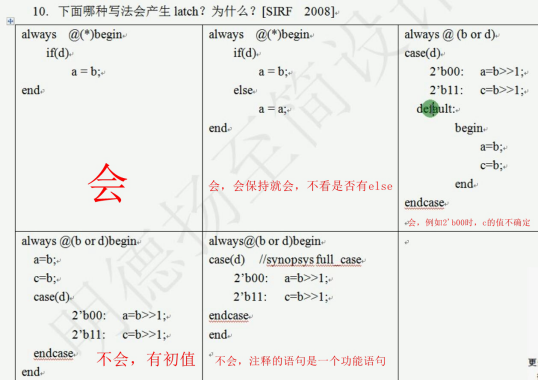

上面已经说了锁存器的缺点,但只是文字,可能比较难懂。归根结底都是书上喜欢在介绍D锁存器时就写上CLk的字眼。我们再回顾一下锁存器和触发器概念,锁存器是电平触发,触发器是边沿触发,所以很多人看到CLK就不会分析了,殊不知,这里的CLK是看电平高低判别的,不是看边沿的,看边沿就属于D触发器了,数电书上区别如下所示:

D锁存器

D触发器

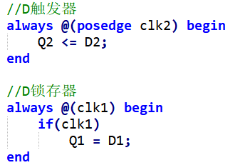

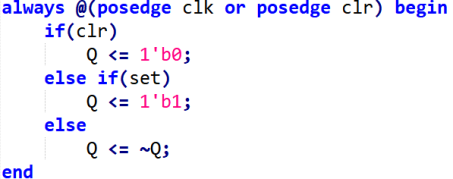

我们再来看看代码层面,他们的区别:

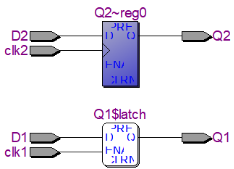

现在再来看一下经典题型:

可以看出,只要一般来说组合逻辑里else、case不全、未写default、else后保持,这些情况大多会生成latch。

3、D触发器

D触发器的分析和D锁存器几乎一致,唯一区别是触发方式是边沿触发。

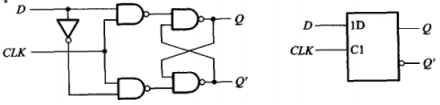

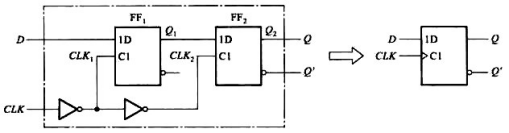

4、D触发器电路图

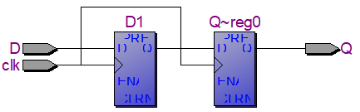

(1)电路结构1

(2)电路结构2

可以看出第一种和第二种是一样的效果,以后遇到题目就不要再懵逼了!

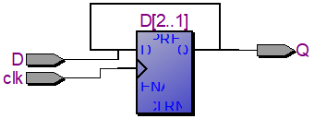

5、

6、边沿触发器D输入端对于毛刺不敏感,只需要满足 setup/hold,不需要专门加滤波器?

对。

7、D 触发器哪些端口毛刺对它没有影响(A)

A、D 触发端

B、时钟端

C、置位端

D、清 0 端

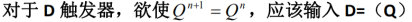

8、用门电路(D触发器)实现边沿检测?

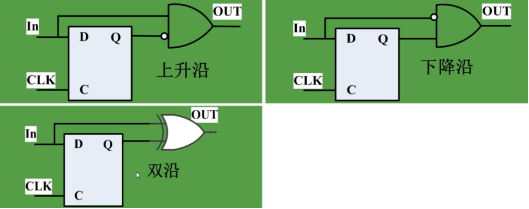

9、用波形表示D触发器的功能?

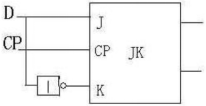

10、用JK触发器和必须的门电路,实现D触发器的功能?

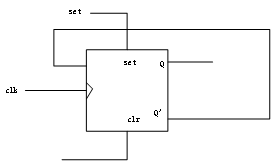

11、用D触发器带同步高置数和异步高复位端的2分频的电路,画出逻辑电路Verilog描述。

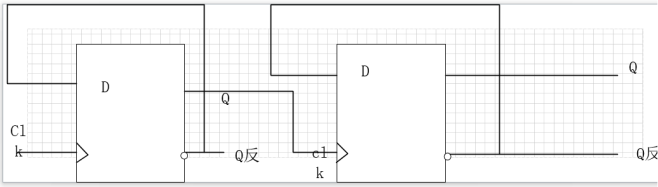

12、画出4分频电路

解析:两个二分频电路相连,就是4分频

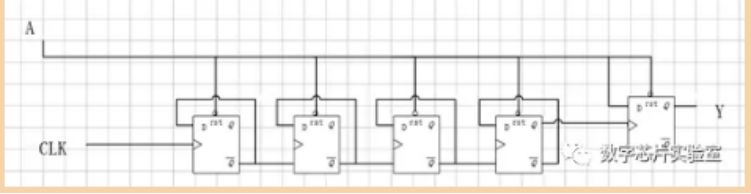

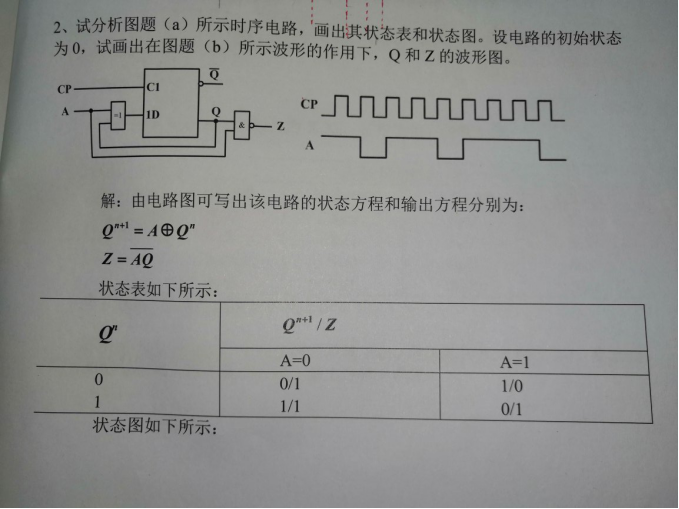

13、分析一下电路功能

前4个D触发器构成一个16分频的电路;

当A为低电平时,5个D触发器全部复位,Y输出低电平;当A为高电平时,左边4个触发器开始分频计数,计数到第4个触发器输出高电平时,Y输出高电平。

(个人觉得功能是检测输入A高电平脉冲宽度)

14、移位寄存器

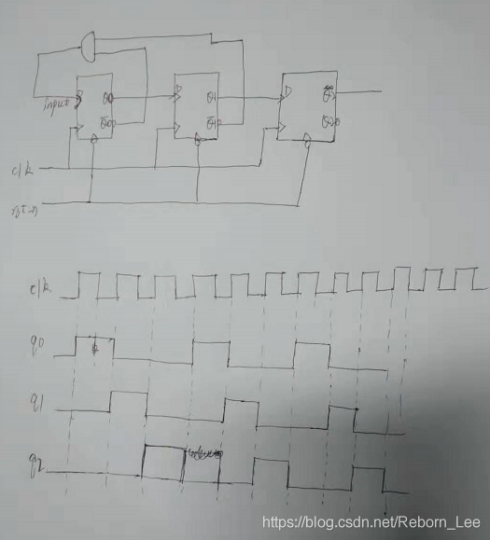

15、画出Q0、Q1、Q2的波形,并描述电路功能。

分析:Q0的输入是什么?题目没有给初值,因此我们就取寄存器初值0,那么Q0 = Q0’& Q1’=1,这个值传给Q1,维持1个节拍后传到Q2,Q2拉高。Q2拉高的这个时钟沿,Q0=1,Q0’=0,因此Q0的输入变为0了,Q0就拉低。后面Q1和Q2的波形和Q0类似。在Q2拉高的那个沿,Q0=Q0’& Q1’=1,Q0又拉高了,后面循环反复。最后电路功能可以描述为:占空比为1:2的三分频电路。

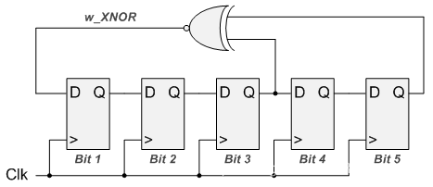

16、线性反馈移位寄存器(LSFR)

17、一个线性反馈移位寄存器(LSFR)的特征多项式为F(x)=x4+x+1,初始态全为1,以下哪些描述是正确的?(BCD)

A. 输出的m-序列为11100101

B. 该LFSR包含四个寄存器

C. 寄存器的状态不会出现全零

D. 该LFSR能够产生的不重复序列最长为15位

下图是多项式对应的电路图:

输入初始为:1111

4个寄存器序列依次为:

1111 -> 0111 -> 1011 -> 0101 -> 1010 ->

1101 -> 0110 -> 0011 -> 1001 -> 0100->

0010 -> 0001 ->1000 -> 1100 -> 1110 ->1111

OUT 序列依次为:111101011001000

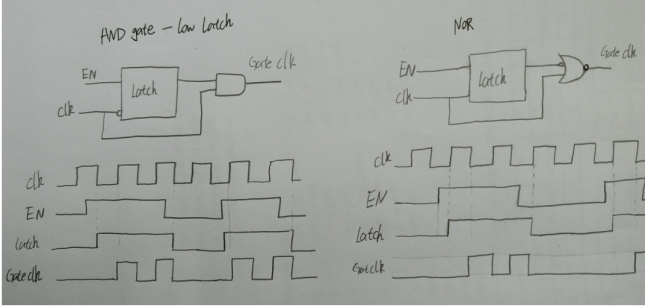

18、画出clock gating cell的原理图

19、下图中的触发器的初态均为0,试画出对应A、B的X、Y的波形。

AB互相缠绕,这就有点难分析了。分析X时,B看成时钟,分析Y时A看成时钟,带D触发器真值表即可。用状态方程会不会快一些?

20、

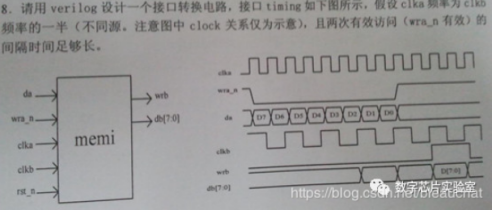

21、用verilog设计一个接口转换电路,接口timing如下图所示,假设clka频率为clkb频率的一半(不同源。注意图中clock关系仅为示意),且两次有效时间(wra_n有效)的间隔时间足够长。

module interface_change ( input clka , input wra_n, input da , input clkb, output [7:0] db , output wrb ); reg [7:0] data = 0 ; always@(posedge clka) begin if(!wra_n)begin data<= {data[6:0],da} ; end end reg wra_n_reg1 ,wra_n_reg2 ; always@(posedge clkb ) begin wra_n_reg1<= wra_n ; wra_n_reg2<= wra_n_reg1 ; end wire wra_n_check ; assign wra_n_check = wra_n_reg1&&(!wra_n_reg2) ; assign wrb = wra_n_check; assign db = (wra_n_check == 1'b1) ? data :0 ; endmodule

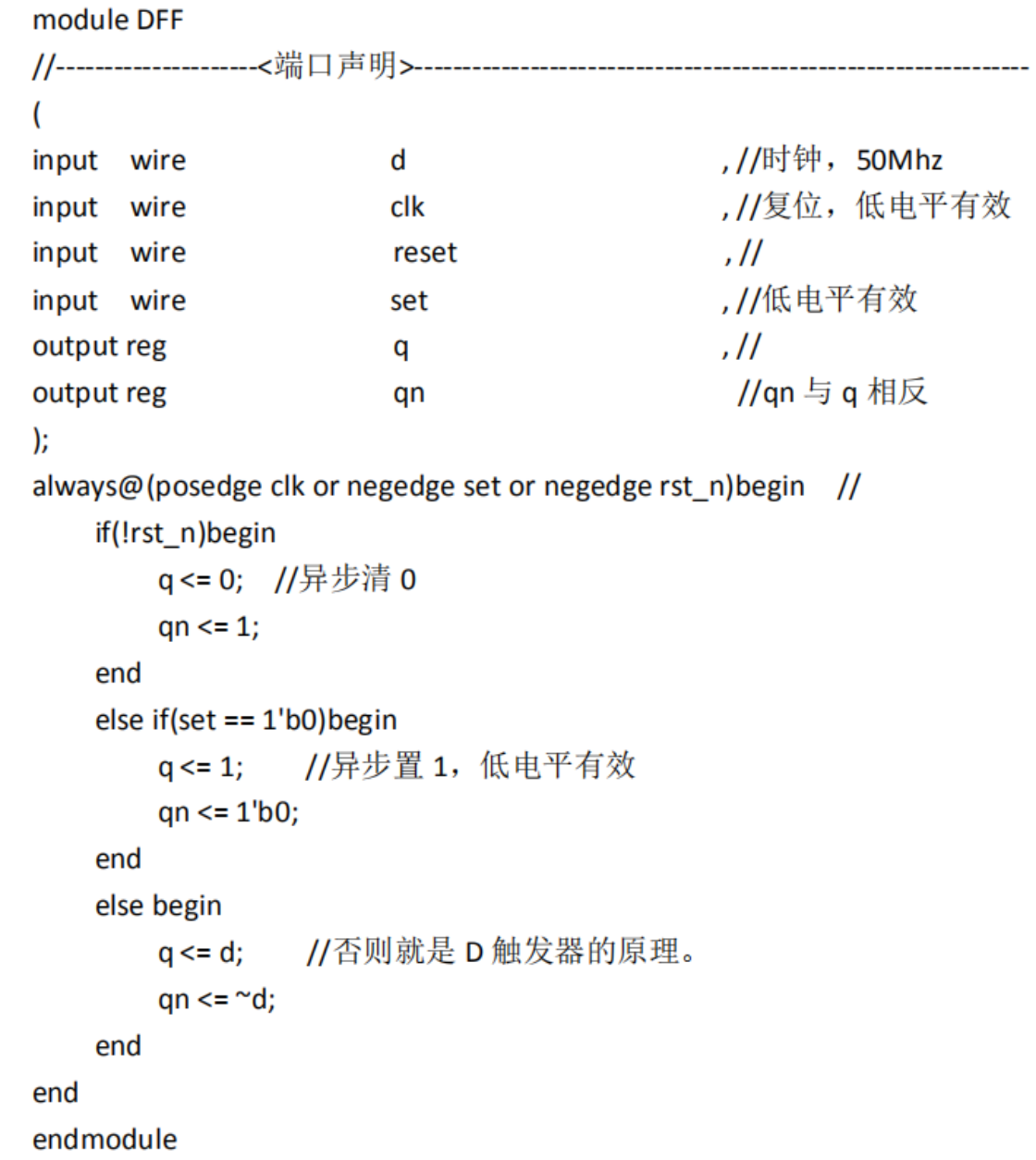

22、编写代码,完成带异步清 0,同步置 1(低电平有效)的 D 触发器

23、关于时序逻辑编码,下列描述正确的是(C)

A、设计中所有寄存器必须带复位;

B、设计中不能使用latch;

C、一个功能模块通常只使用一个时钟沿;

D、异步复位信号可以插入组合逻辑,不影响功能;

24、下面关于时序部件描述错误的为(D)

A、触发器的setup+hold通常大于0

B、锁存器在时钟为窄脉中的驱动下可以作为触发器使用

C、逻辑路径插入触发器可以提高电路运行速度

D、触发器的setup不能为负数