一、概述

1、存储概念

- 存储单元:只能存储一位数据的存储电路。

- 寄存器:用于存储一组数据的存储电路。由一组触发器组成。

- 存储器:用于存储大量数据的存储电路。

2、存储单元分类

(1)静态存储单元

由门电路连接而成,其中包括各种电路结构形式的锁存器和触发器。

- 只要不断电,其状态会一直保持下去。

(2)动态存储单元

利用电容的电荷存储效应来存储数据。

- 充放电需要时间,因而速度低于静态存储单元。

- 电荷随时间而泄露,因而必须定期“刷新”才能保证数据不丢失。

3、存储器分类

(1)随机存储器(Random Access Memory,RAM)

- ①静态随机存储器(Static Random Access Memory,SRAM),用的是静态存储单元。

- ②动态随机存储器(Dynamic Random Access Memory,DRAM),用的是动态存储单元。

(2)只读存储器(Read Only Memory,ROM)

不能写,只能读,掉电后数据不丢失。

- ①掩模ROM(Mask Read Only Memory),数据在制作芯片时写入,之后无法更改。

- ②可编程ROM(Programmable Read Only Memory,PROM),数据由用户写入,之后无法更改。

- ③可擦除的可编程ROM(Erasable Programmable Read Only Memory,EPROM),数据由用户写入,用紫外线擦除重写。

- ④带电可擦可编程ROM(Electrically Erasable Programmable Read Only Memory,E2PROM),数据由用户写入,用电信号擦除重写。

二、SR锁存器

SR锁存器(Set-Reset Latch)是静态存储单元中最基本、最简单的一种。

- 通常由两个或非门或者与非门组成。

- 不具备记忆功能。

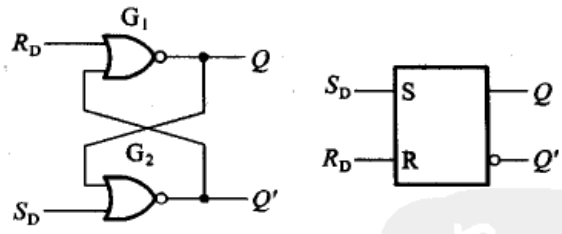

(1)或非门 SR 锁存器

----------------------

RD:复位端,置0输入端。

SD:置位端,置1输入端

----------------------

1状态 0状态

Q :输出端 1 0

Q‘:输出端 0 1

----------------------

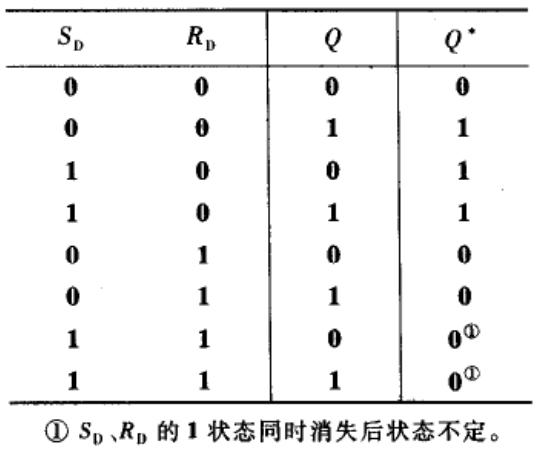

Q为初态,Q*为次态,约束条件:SDRD = 0,不允许 SD = RD = 1 状态同时消失。

真值表怎么看:

- ① 两个输入端,1 看成有效,0看成无效。

- ② SD = 1,即置位端为 1 有效,则 Q* = 1。

- ③ RD = 1,即复位端为 1 有效,则 Q* = 0。

- ④ SD = RD = 0 时,即输入都无效,则 Q* = Q。

- ⑤ SD = RD = 1 时,即输入都有效,则 Q* = 0,且 Q' = Q。

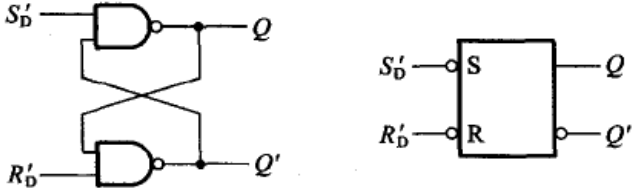

(2)与非门 SR 锁存器

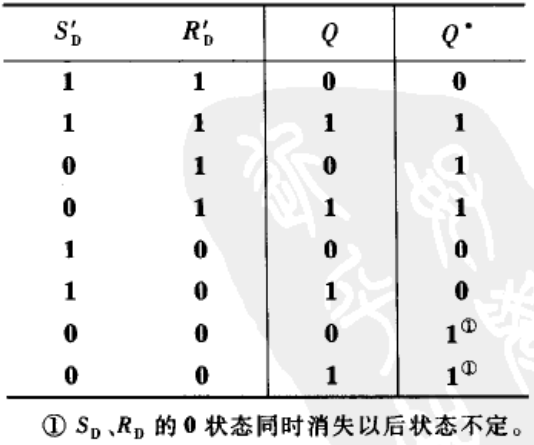

Q为初态,Q*为次态,约束条件:SD'RD' = 0,不允许 SD' = RD' = 0 状态同时消失。

真值表怎么看:

- ① 两个输入端,1 看成无效,0看成有效。

- ② SD = 0,即置位端为 0 有效,则 Q* = 1。

- ③ RD = 0,即复位端为 0 有效,则 Q* = 0。

- ④ SD = RD = 1 时,输入都无效,则 Q* = Q。

- ⑤ SD = RD = 0 时,输入都有效,则 Q* = 1,且 Q' = Q。

三、触发器

在锁存器的基础上加了一个触发信号输入端 CLK,触发信号有效时,锁存功能才有效,即该触发器才有效。

1、电平触发器

啊

2、边沿触发器

啊

3、脉冲触发器

啊

四、寄存器

五、存储器