PL端使用过后,来到了ZYNQ核心的部分:PS端,现在用Vivado软件对ZYNQ-7000开发板的PS端进行第一个程序设计:Hello World。

一、新建Vivado工程

1.打开Vivado,新建一个工程,Next

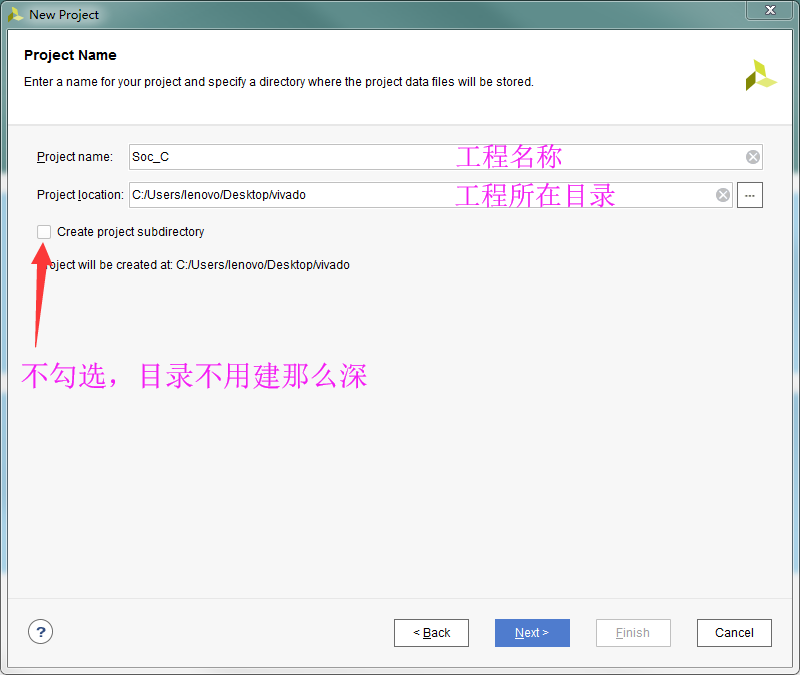

2.设置工程名称和工程所在目录,Next

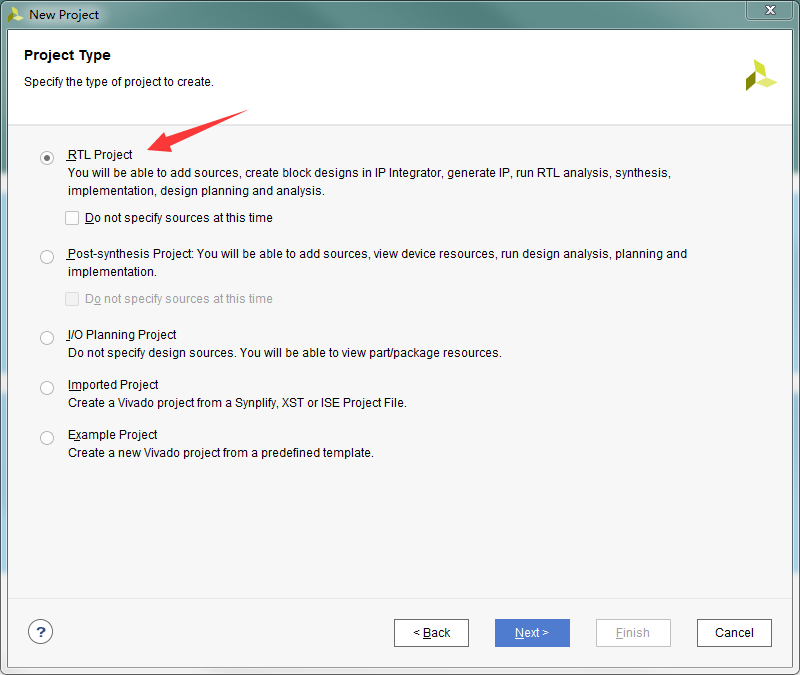

3.选择第一项:RTL Project,Next

4.添加资源,可以直接Next

5.添加约束,可以直接Next

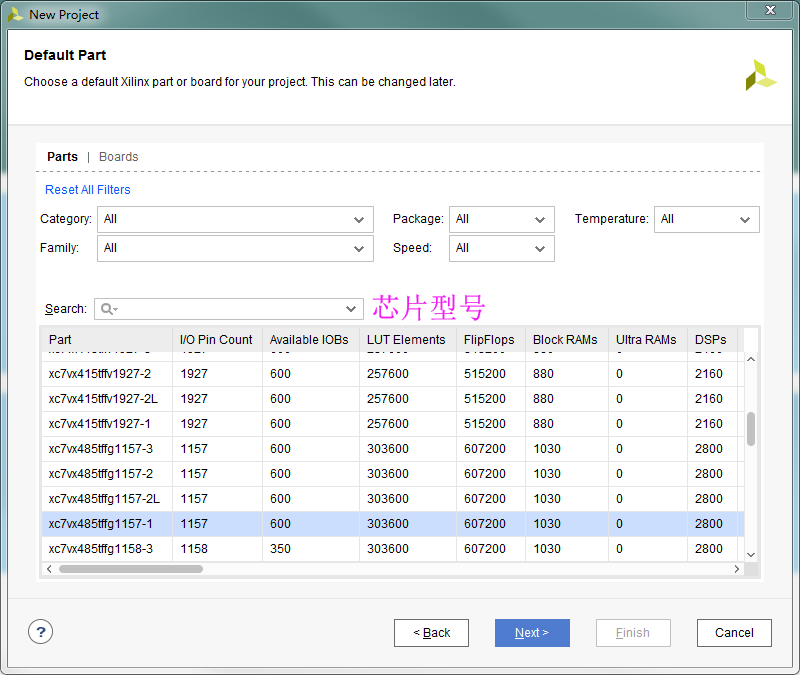

6.芯片型号选择xc7z020clg400-1,Next

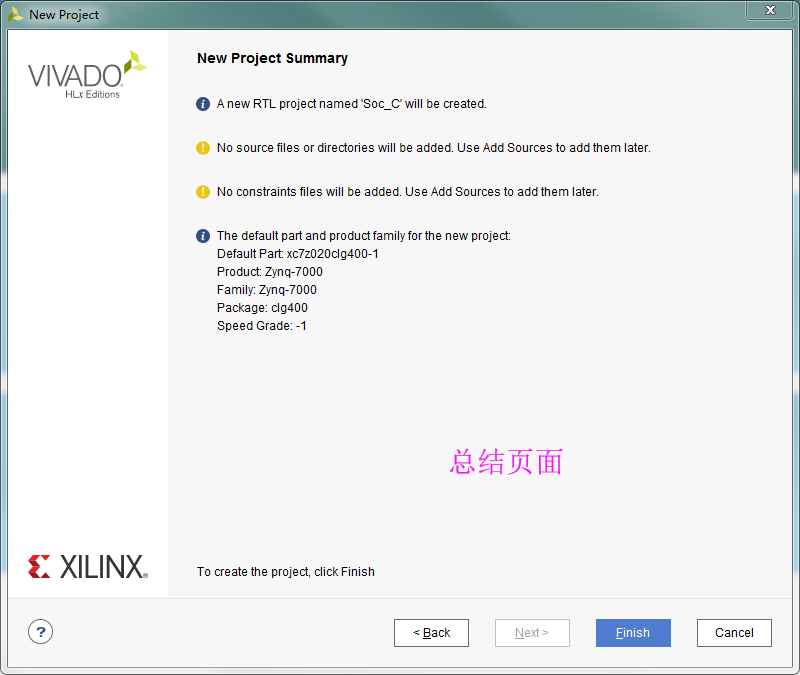

7.总结页面,Finish

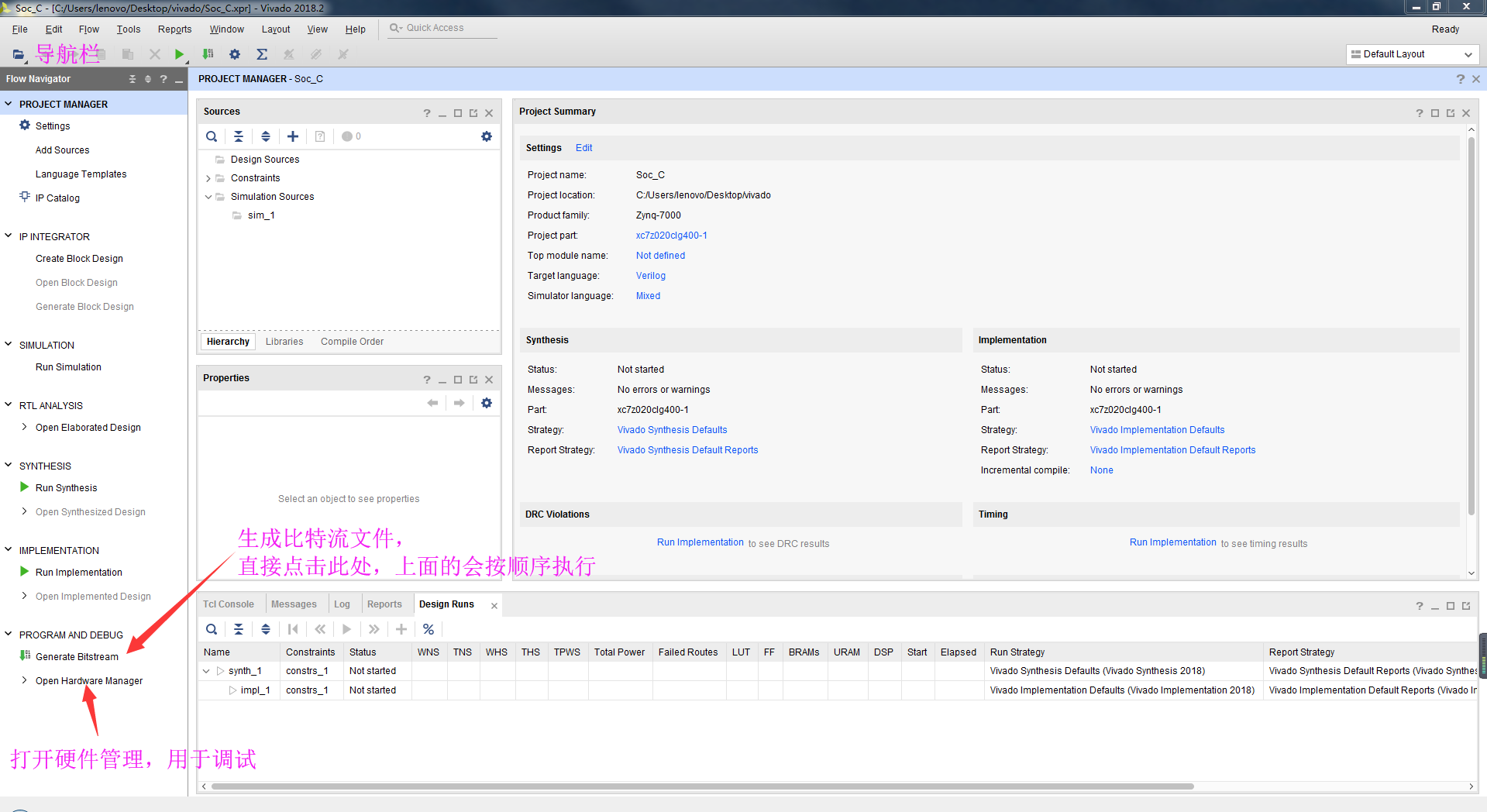

8.进入Vivado工程页面,左边是导航栏,可以直接点击Generate Bitstream,上面的选项也会按顺序被执行。Open Hardware Manager则是硬件管理,用于下载、调试等。

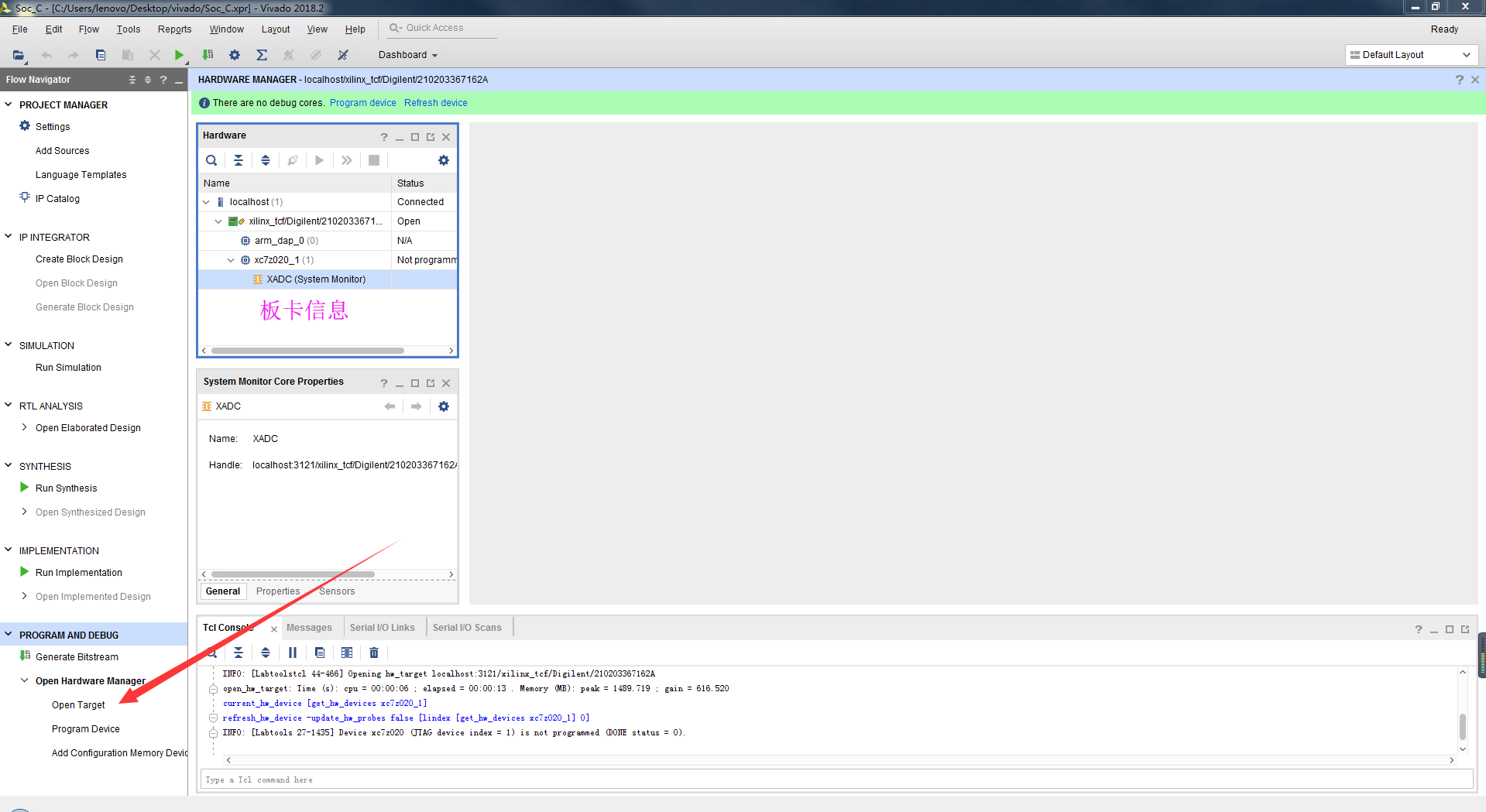

9.如果连接好了板卡,那么点击Open Hardware Manager --- Open Target则可以看到板卡信息。

二、ZYNQ IP核设置

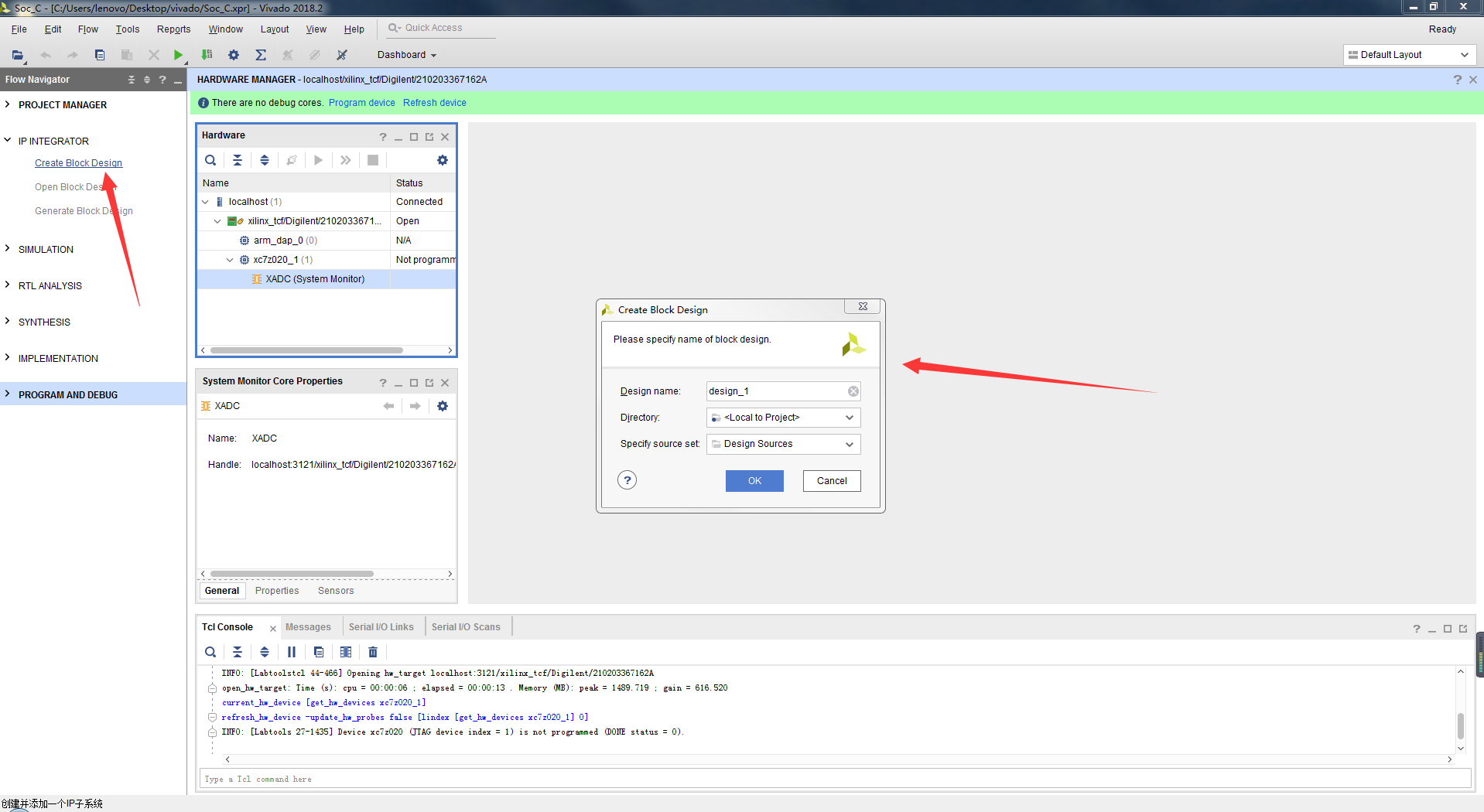

1.点击导航栏的 IP INTEGRATOR --- Create Block Design,弹出工程名称和工程位置,填写后点OK

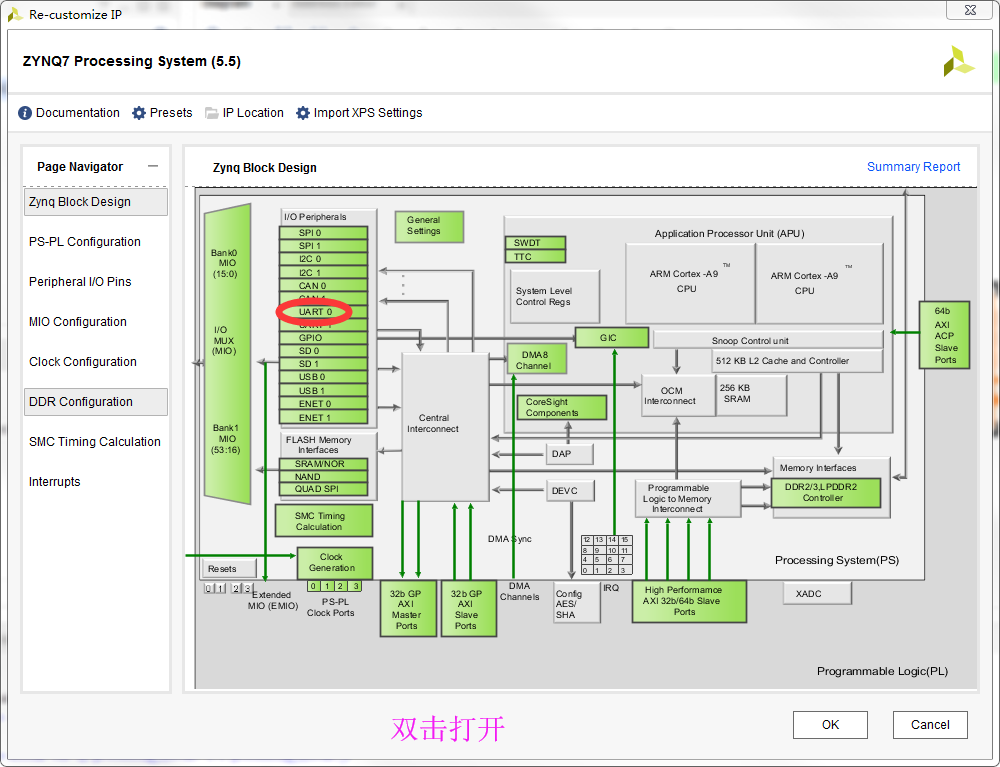

2.点击中间的 + 号添加IP,然后在弹出的小窗口中选择ZYNQ,双击该IP核

3.此时看到ZYNQ的接口界面,有几个引脚,我们只需要最简单的系统,双击ZYNQ进行参数设置

4.进入到ZYNQ内部资源区域,此处可以看到内部有哪些资源可以使用。

Zynq Block Design 主页面 PS-PL Configuration PS到PL的相关接口配置信息以及PS部分的一些配置信息 Peripheral I/O Pins 通用外设接口的配置 MIO Configruation 对MIO以及EMIO的分配控制 Clock Configruation PS端时钟资源的配置和管理 DDR Configration DDR控制器的一些参数配置 Interrupts 中断的配置管理

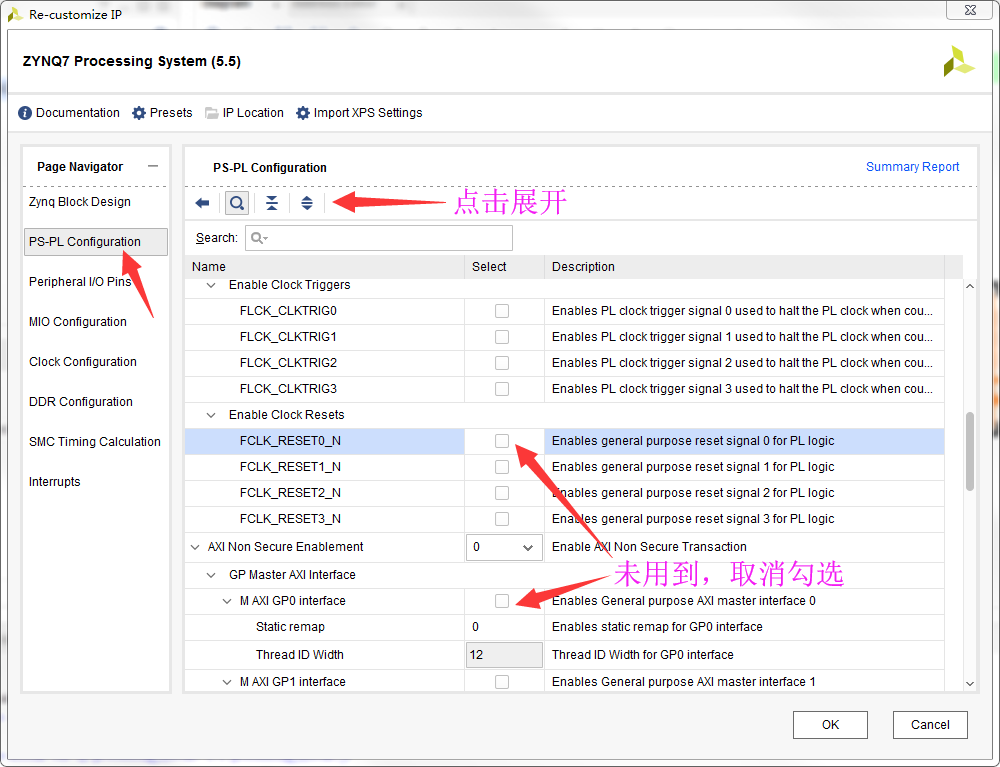

5.点击左侧的PS-PL Configuration, 取消勾选这两项。

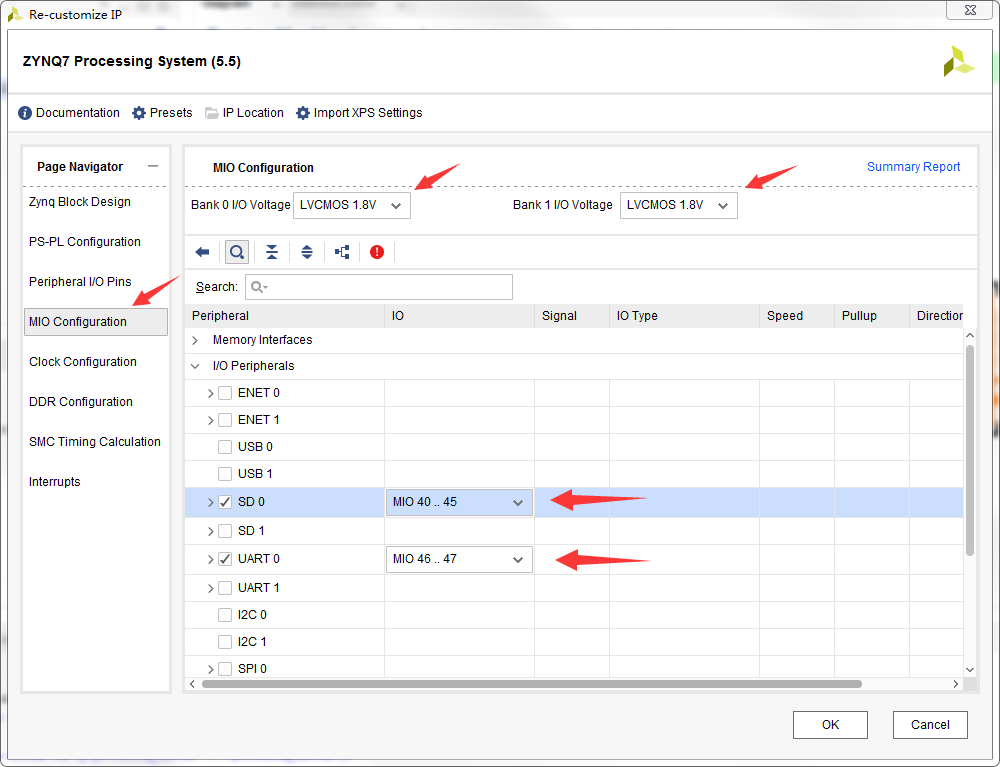

6.点击左侧的MIO Configuration,电压设置成LVCMOS 1.8V,用到了SD和UART,因此勾选它们并且设置引脚编号。

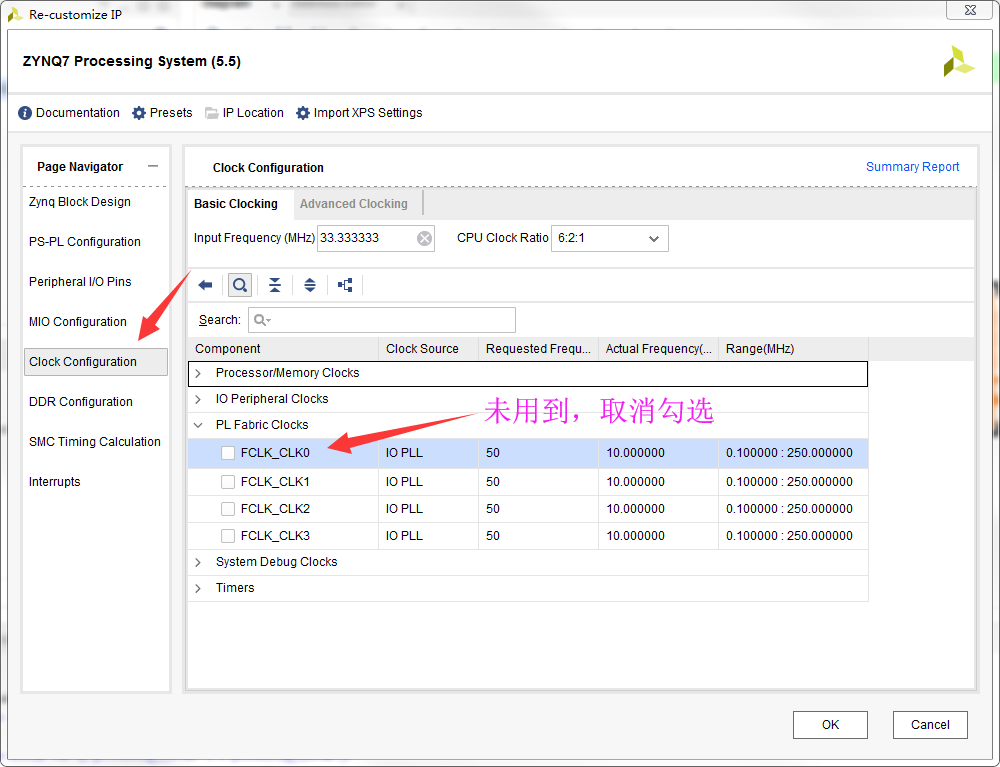

7.选择Clock Configuration,本实验没有用到FPGA板卡时钟,因此取消勾选。

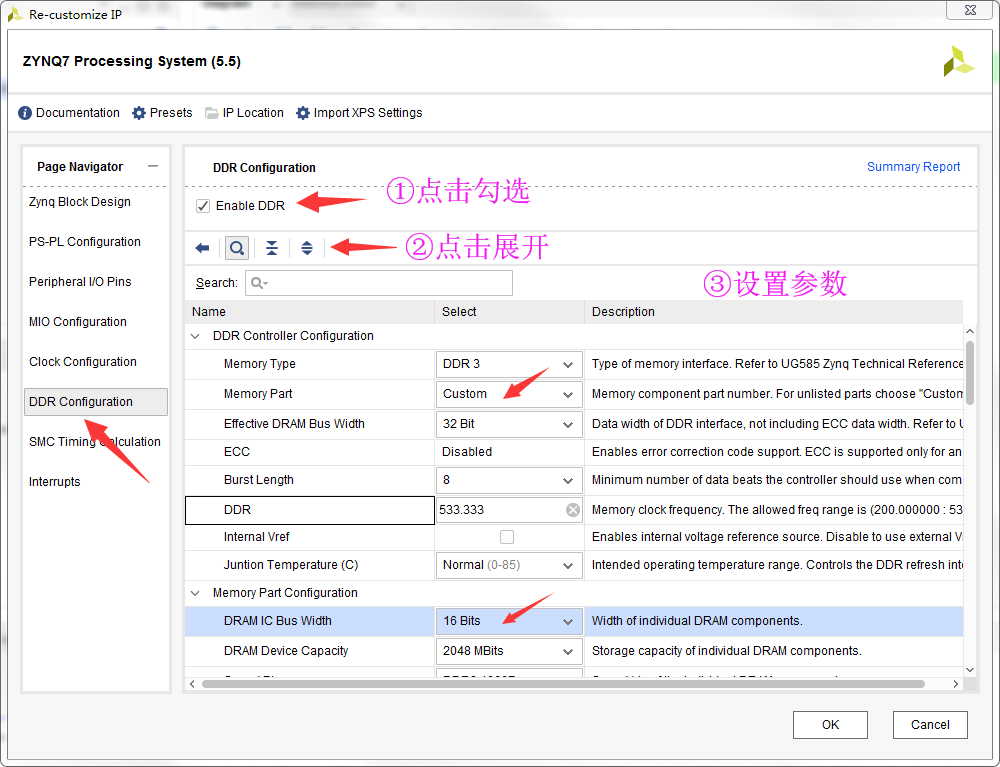

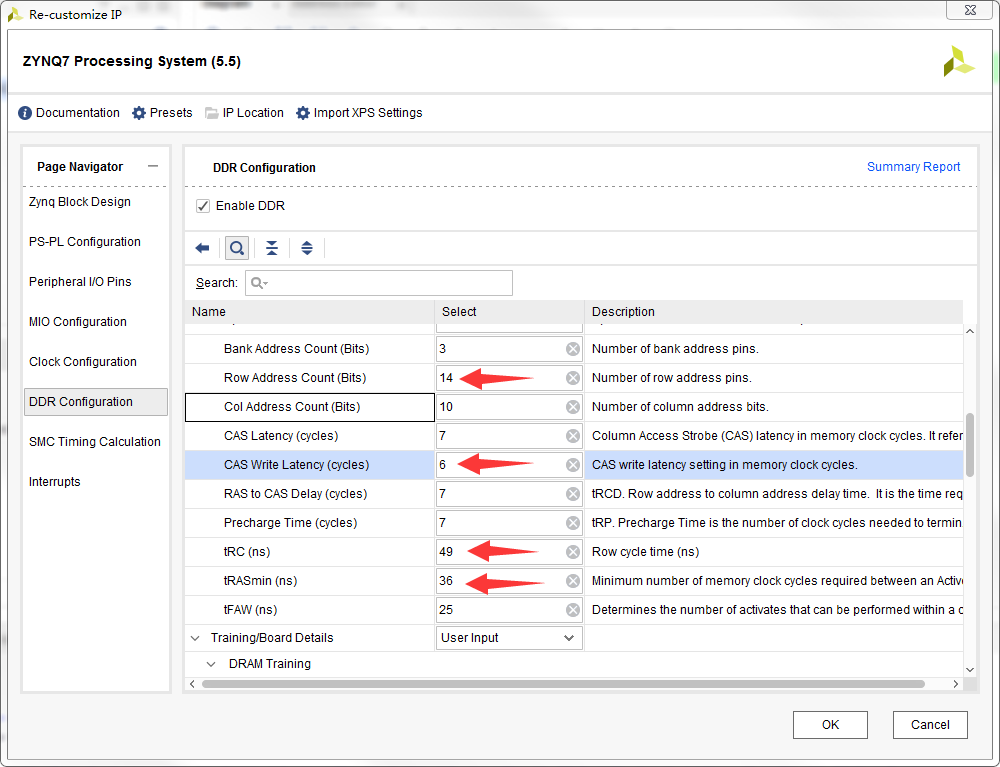

8.点击左侧DDR Configuration,勾选Enable DDR,点击展开,对DDR进行一些参数设置,之后点击OK

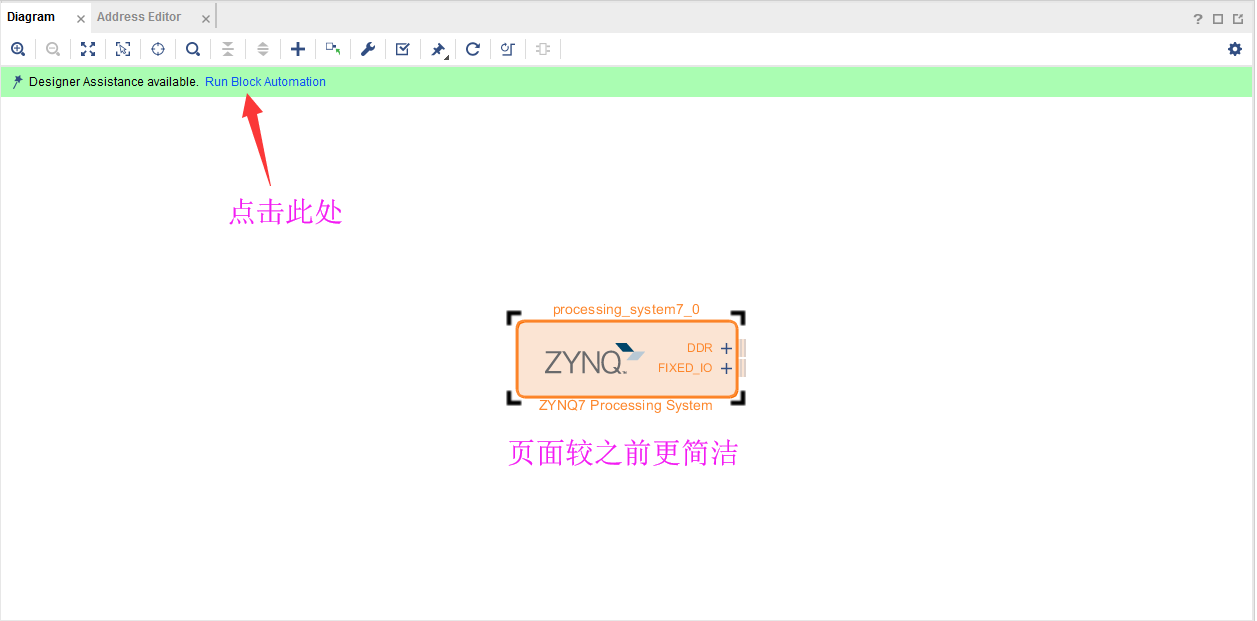

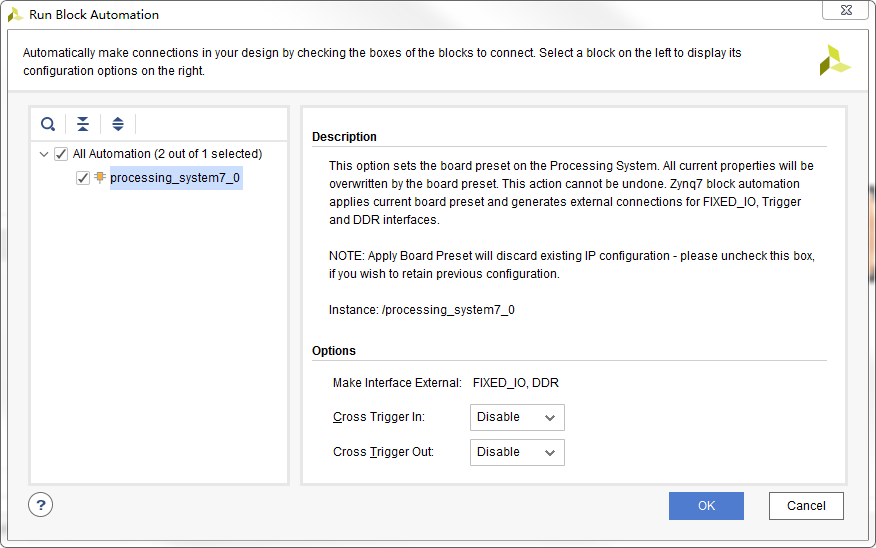

9.回归到ZYNQ主页面,可以看到比之前更简洁了。上面绿色横条处点击Run Block Automation

10.点击OK

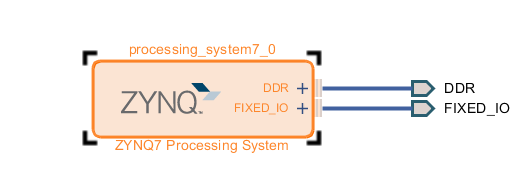

11.ZYNQ变成了如下的结构图。

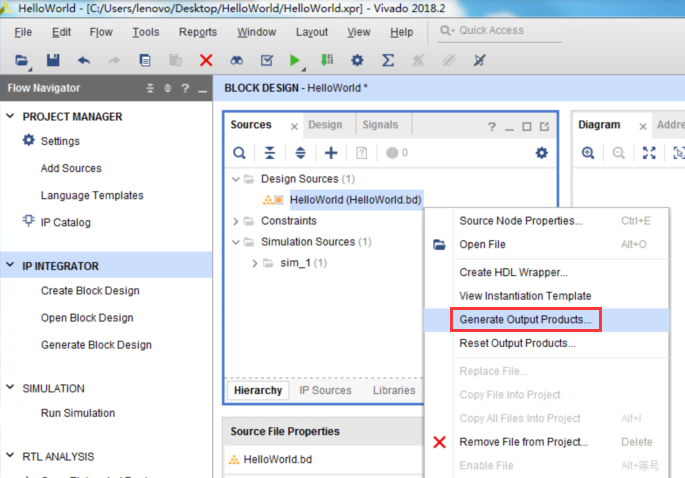

12.点击 Source 栏的工程,鼠标右键选择 Generae Output Products

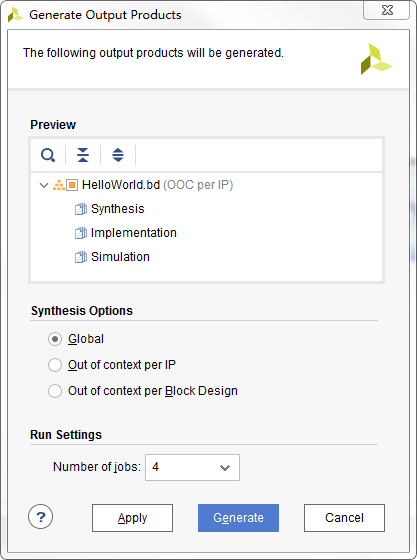

13.弹出一个小窗口,第一项为全局模式,更慢但保险,第二项为OOC模式,更快但有逻辑问题时会编译不通过,我们选第一项,下面线程根据自己电脑配置选择最大的即可。

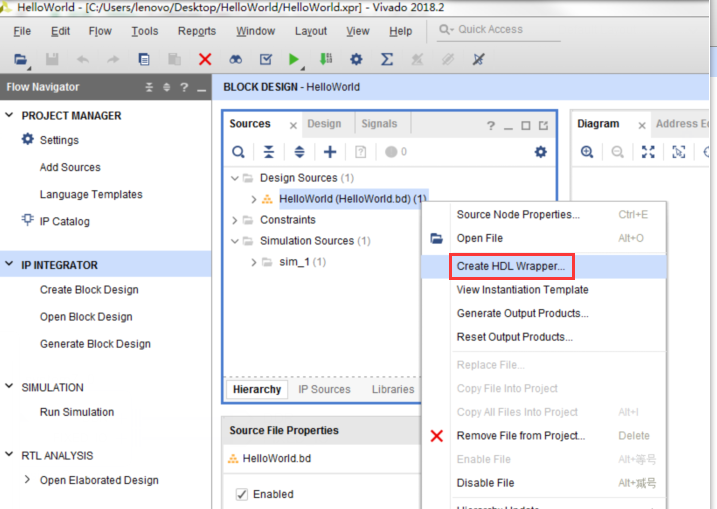

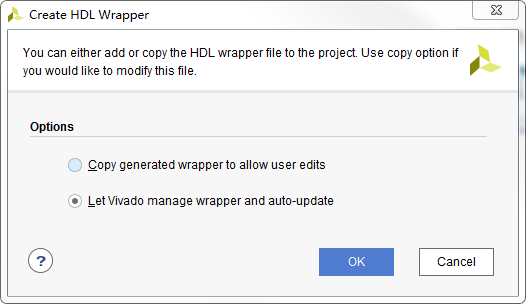

14.设置让Vivado管理我们的文件,点击Sources,右键选择Create HDL Wrapper,弹出的小页面点击OK

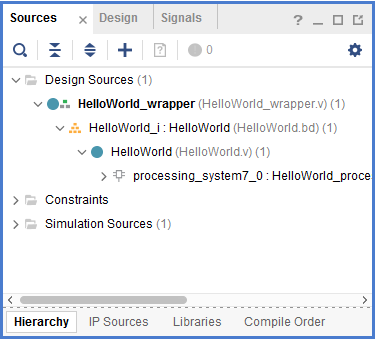

15.完成后的界面如图所示

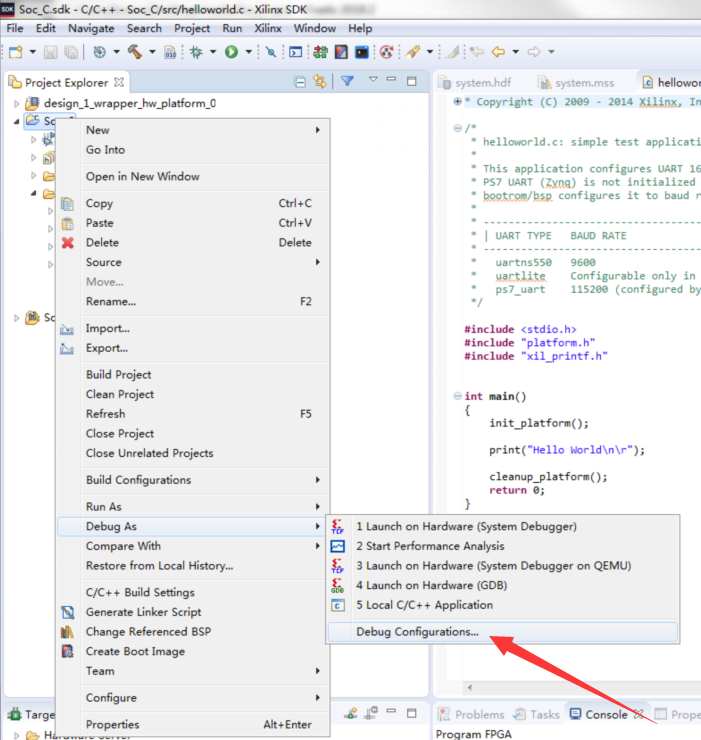

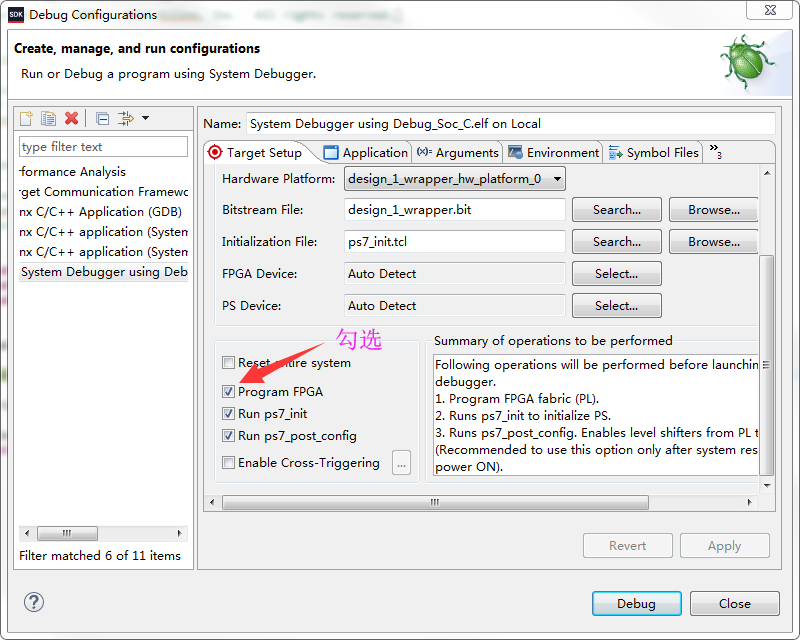

三、使用SDK进行软件开发

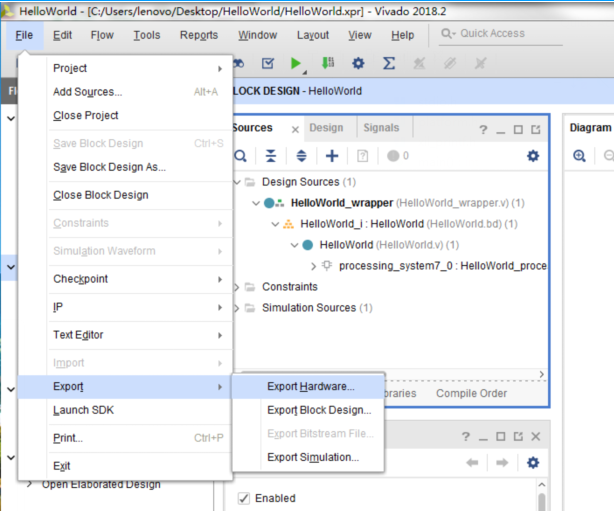

1.本次实验只有 PS 部分的管脚,没有 PL 部分的管脚,而且 PS 部分的管脚都是固定的,所以我们不需要添加管脚约束文件。另外因为没有使用 PL 部分的资源,我们也不需要在 Vivado 下编译和生成 bit 文件了。直接将文件导出到SDK开发目录,点击 File --- Export --- Export Hardware

2.未用到bit流文件,不用勾选 Include bitstream ,直接点 OK

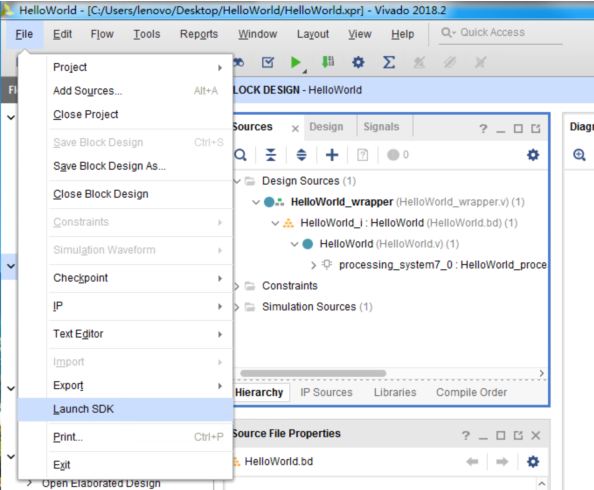

3.启动SDK,点击File Launch SDK,弹出的小窗口直接点OK就行

4.直接点 OK

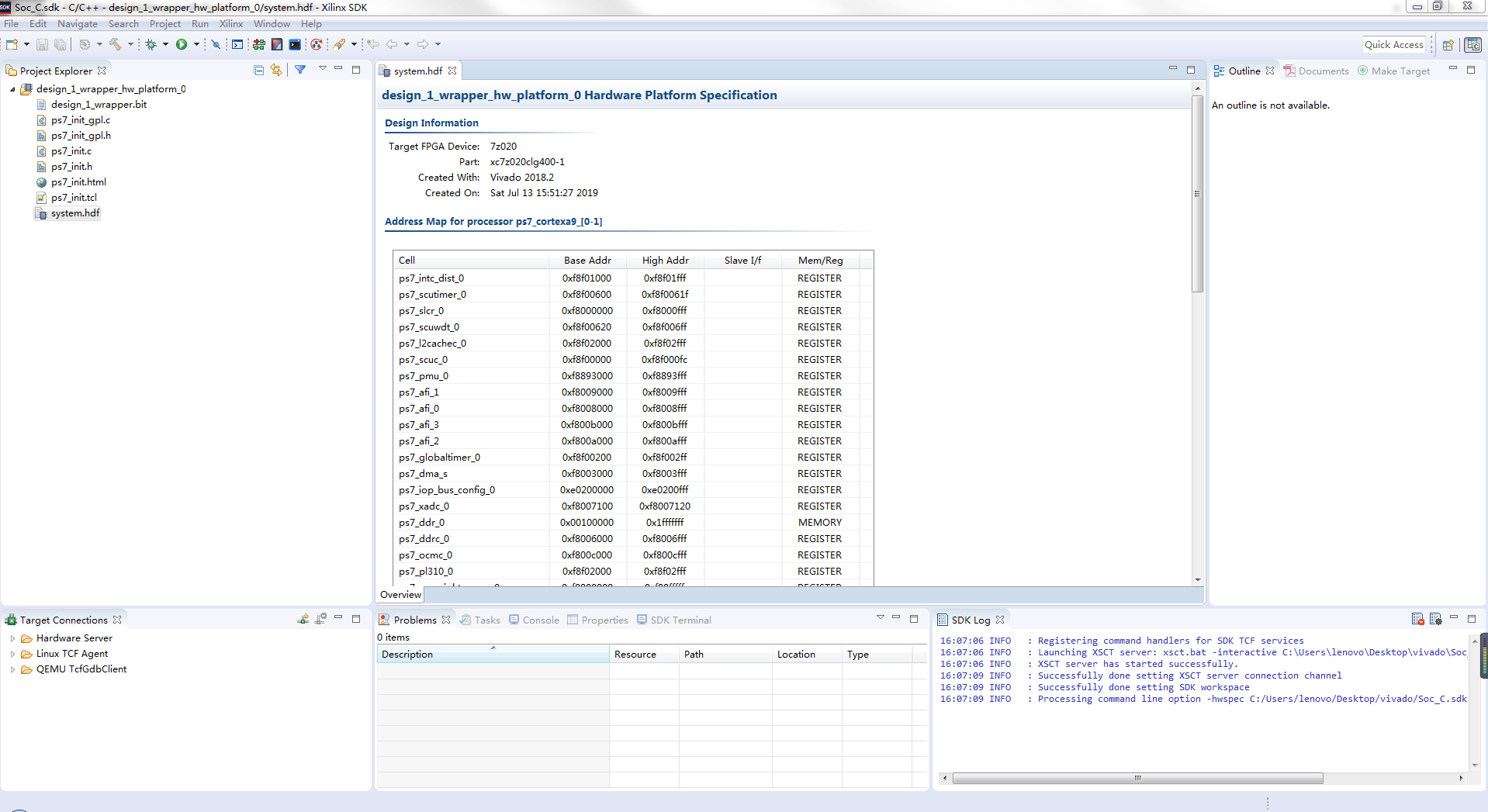

5.如图所示便是SDK软件开发界面了。

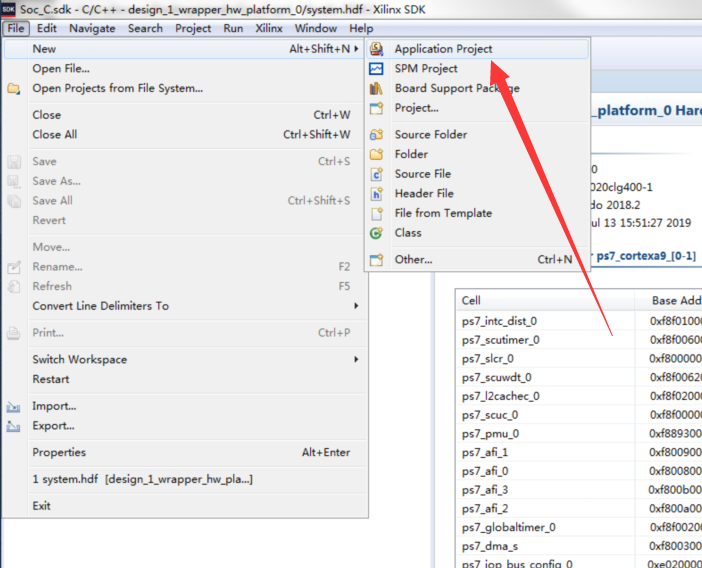

6.新建一个软件的APP,用于后面的C语言编程。点击File --- New --- Application Project

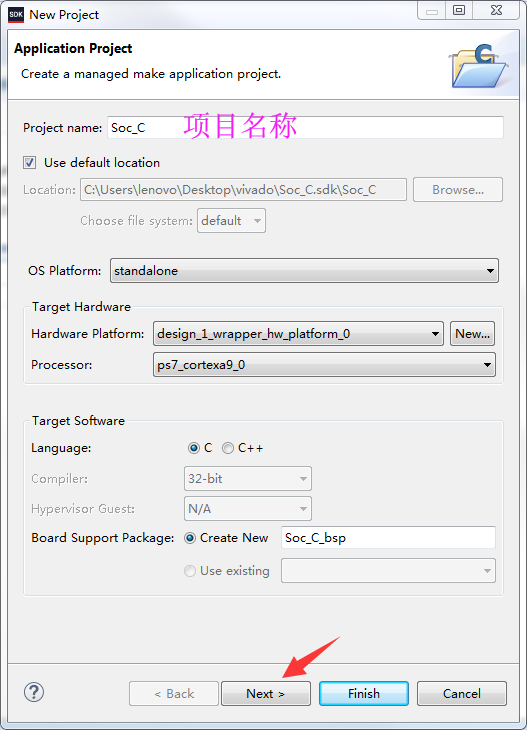

7.填写项目名称,点击Next

8.选择Hello World,点击Finish

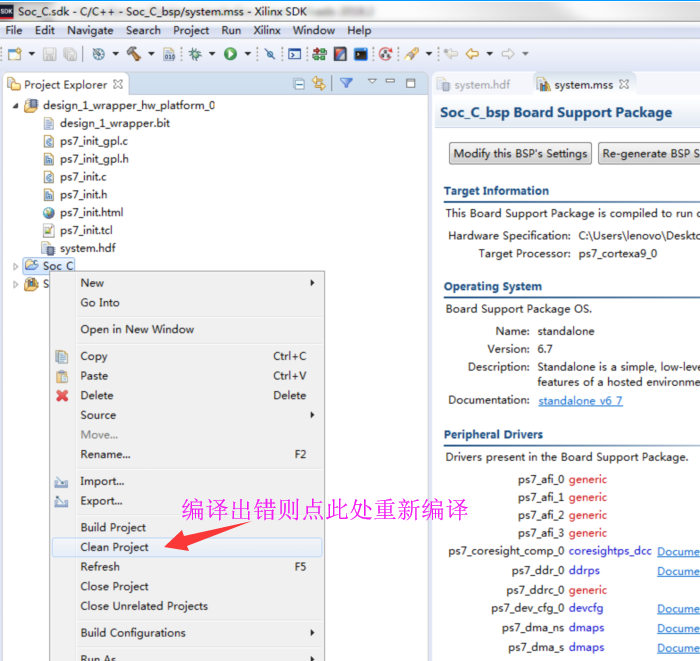

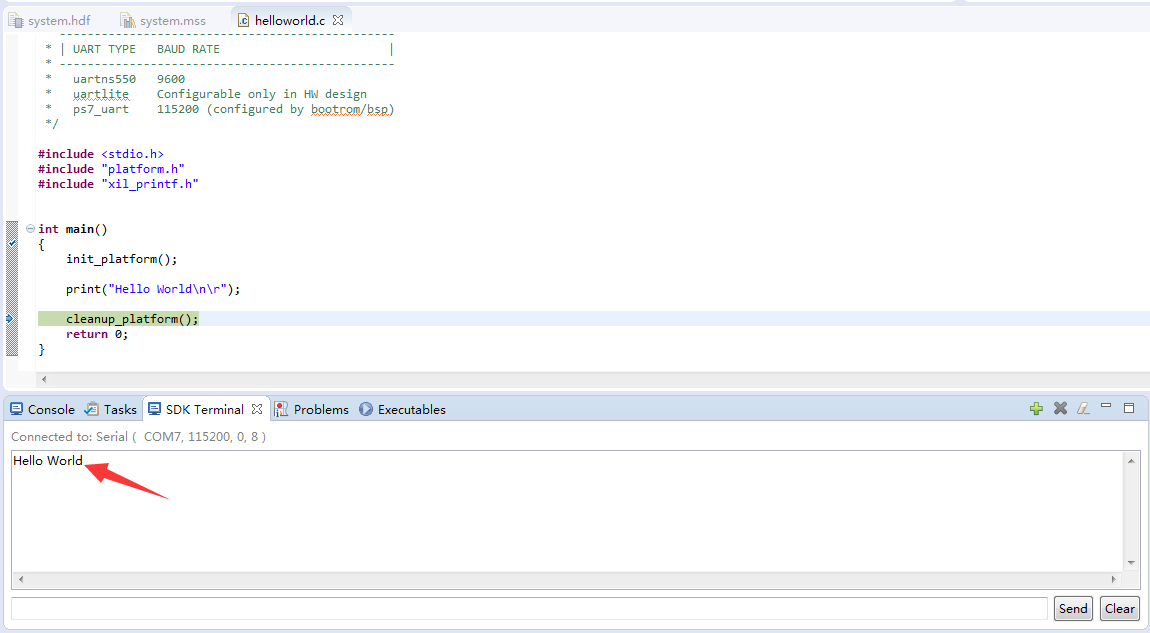

9.此时软件自动开始编译,也可点击 Build Project手动编译,编译完成后出现Hello World 的程序,如果编译出错,可以点击 Clean Project 重新编译。

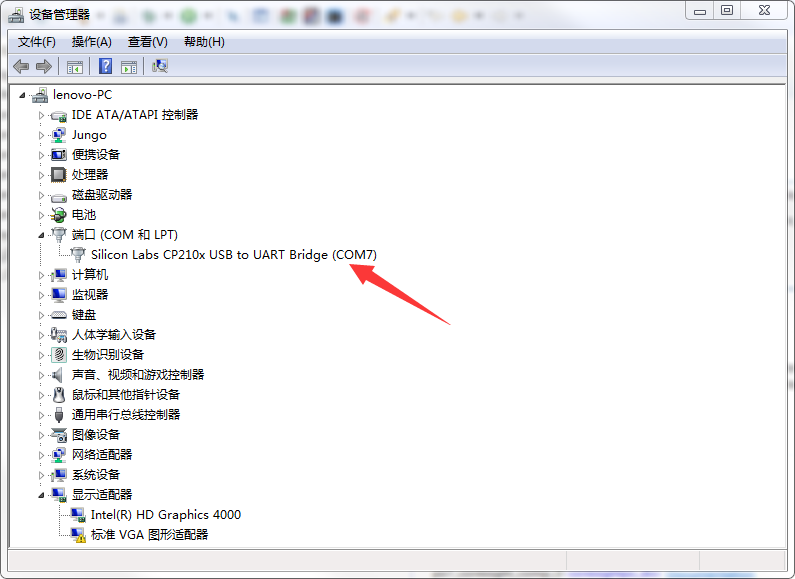

10.本实验需要用到Uart串口,我们打开我的电脑 --- 设备管理器 --- 端口,检查是否已经连接好串口

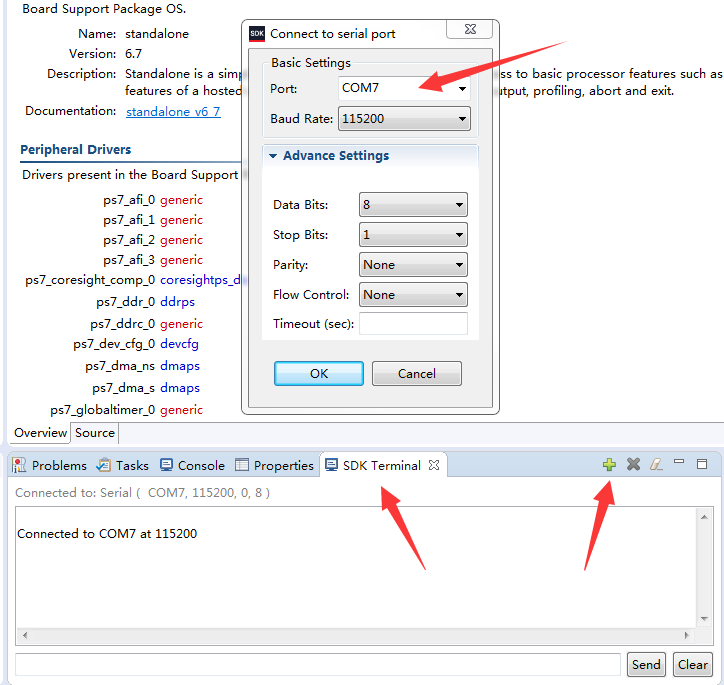

11.回到SDK界面,看到界面下方有一个SDK Terminal,点击该选项,并且点击那个+号,设置其自带的串口工具的参数。

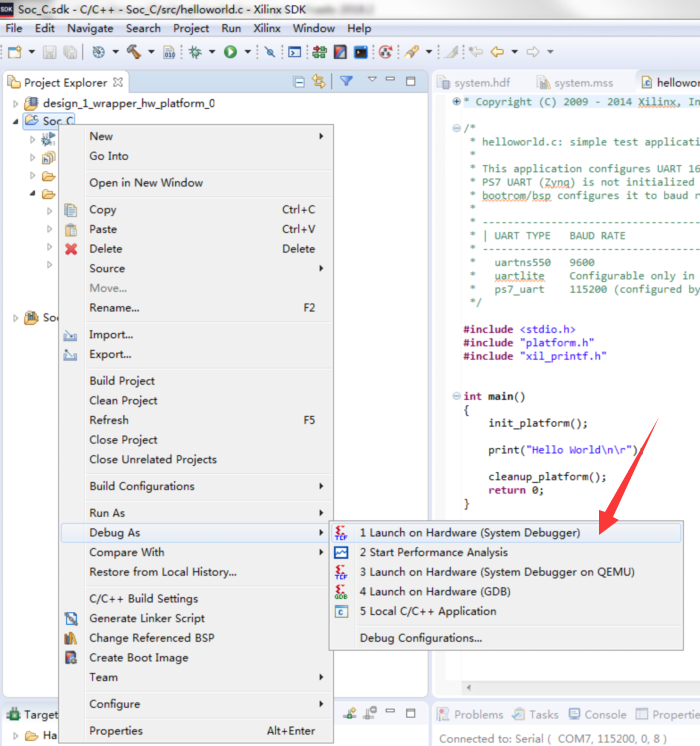

12.点击如下选项

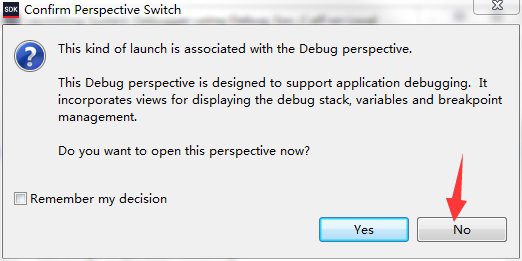

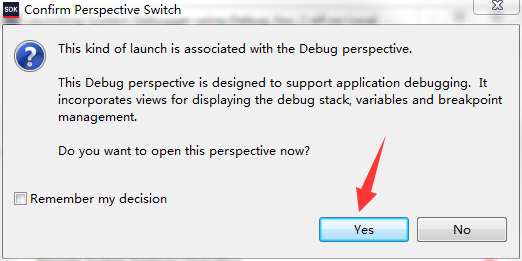

13.如果跳出如下界面,点击No

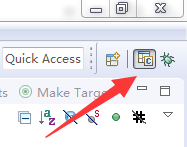

14.点击右上角的按钮可以进行界面切换

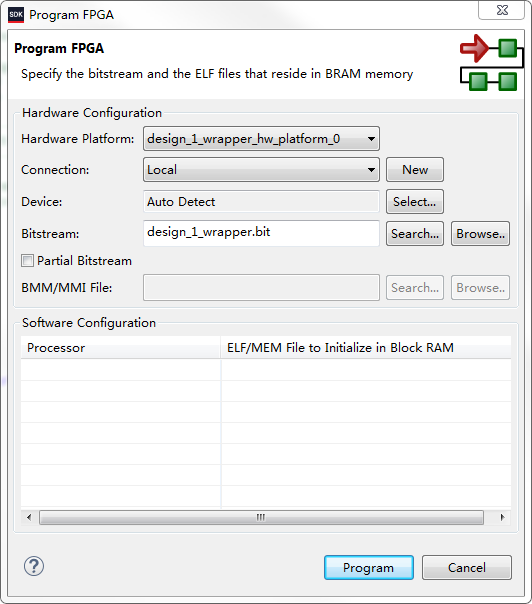

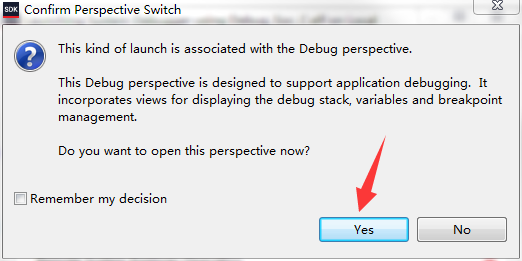

15.点击如下图标可以进行FPGA配置,点击Program将程序烧录进板卡,这时跳出小窗口就要选择yes了。

16.当然,你也可以点击这个选项进行FPGA配置,这时跳出小窗口就要选择yes了。

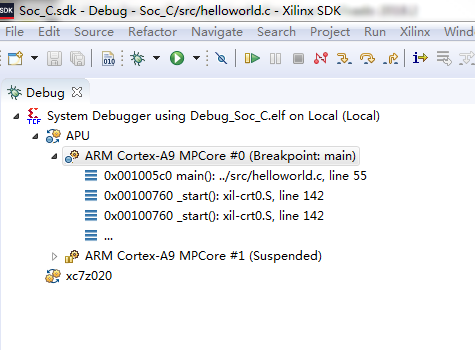

17.页面出现如下的文件目录,表示成功。

18.界面上方有几个调试选项:

Resume:运行到断点为止

Step into:进到函数内部

Step over:单步调试

Step return:跳出函数内部

这里选择单步调试即可,可以看到界面下方的SDK Terminal中显示出:Hello World

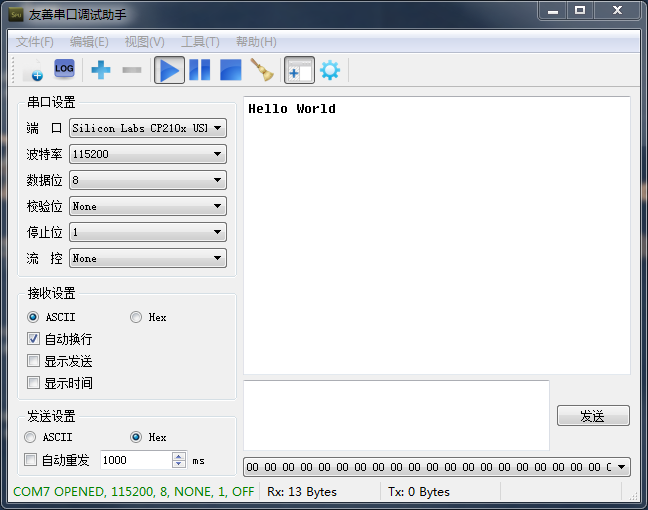

19.当然,也可以使用电脑里的窗口助手软件进行接收,先在SDK Terminal界面中点击X关闭该功能,然后打开电脑里的串口助手,助手需要打开处于可以工作状态,接收设置成ASCII模式。重新回到SDK界面运行程序,可以看到串口助手同样显示出:Hello World

四、补充:C语言界面设置

默认的C语言界面没有行号,而且字体非常小,下面说下怎么调整。

1.点击顶层导航栏的Window---Preferences,点击General---Editors---Text Editors,将下面的Show line numbers勾选上即可显示行号了。

2.然后点击右侧的蓝字'Colors and Fonts',右侧页面变换后选择C/C++---Editor---C/C++ Editor Text Font,点击右侧Edit...即可调整字体和字号,建议字号为14。

参考资料:

[1]V3学院FPGA教程

[2]何宾, 张艳辉. Xilinx Zynq-7000嵌入式系统设计与实现[M]. 电子工业出版社, 2016.