主要内容:4-state,2-state,固定数组

一:基本数据类型

1:sv的位扩展

2:4-state

sv里面使用logic来代替verilog里面的reg,有4值:0,1,x,z

reg不可用于连续赋值语句,但logic可用于连续赋值语句;但logic不能用于多驱动,比如线与,双向驱动。

例子:logic [31:0] r; //4-states,32位

3:2-state

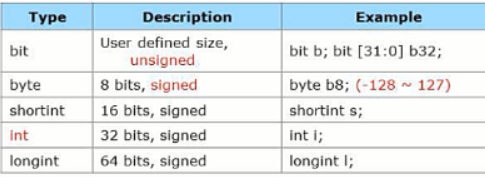

有bit,byte,shortint,int,longint;

只有两种状态0,1;所以x,z直接转化为0或者1;可以提高仿真性能,减少内存,但是不可用于设计中。

除了bit是无符号的,其他都是有符号的;

logic[7:0] x与 byte x 虽然都是8位,但它们是不同的,前者是无符号(0-255),后者是有符号(-128-127)

4:其它

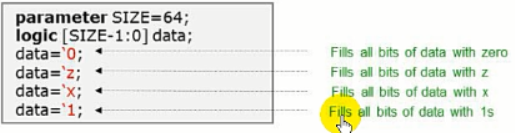

**4-state默认值为x,2-state默认值为0;

**4-state可以赋值给2-state;(2-state可以赋值给我4-state吗)

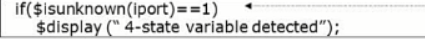

**使用$isunknown操作符来检查是否变量是否为x/z,有则返回1

二:固定数组

支持多维数组,数组不要越界;

1:表达

type name[constant];

一维:int a[16];

多维:int array[0:7][0:3]; int array[8][4];

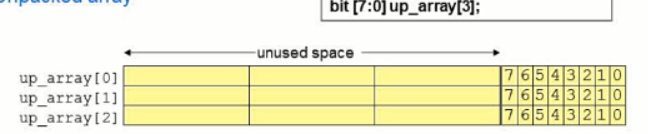

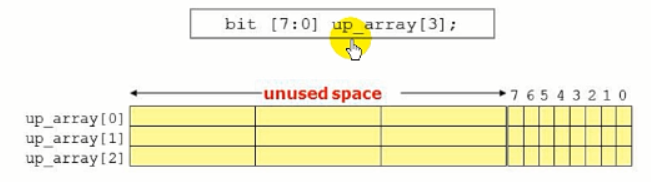

2:unpacked arrays

byte,shortint与int都存储在32位里,longint存储在64位;unpacked数组中,如果数据没有占用32位/64位,仍占用32/64,浪费空间。

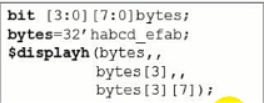

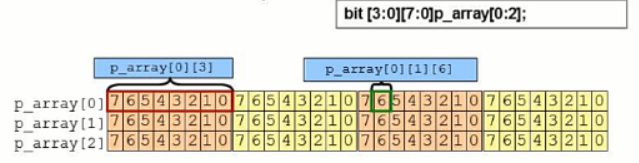

3::packed arrays

说明:bytes是32位的,通过bit[3:0][7:0]将存储空间打包成四份,每一份为8位

4:数组赋值,使用 `{}

例如:int array1[4] = `{3,2,4,2};

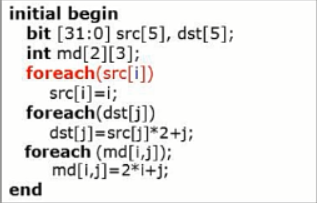

5:数组遍历

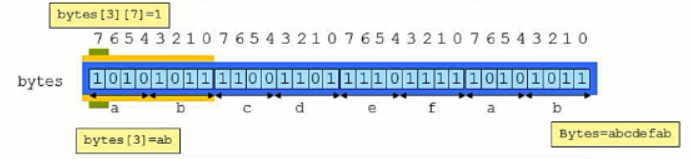

**for

i 需要声明;

$size返回数组个数;

**foreach

索引 i,j自动声明,不需显式声明

6:比较与copy

== !=

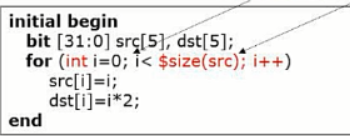

7:Mxied 数组

packed array(不推荐这种unpacked的复杂数组形式)

unpacked array