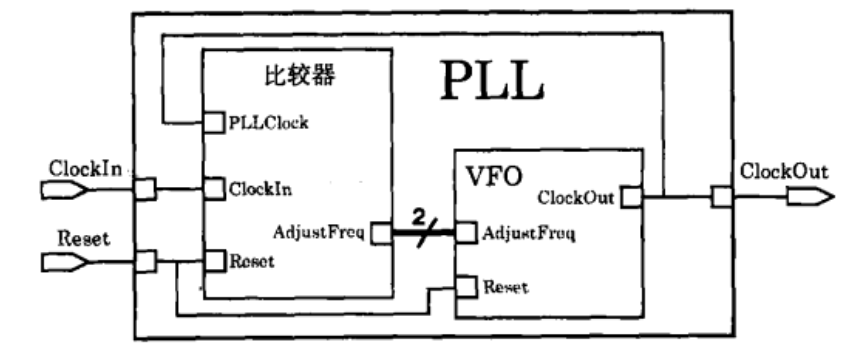

一:PLL

1:组成

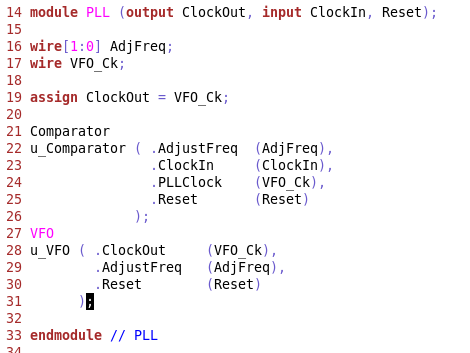

输出时钟产生器,相位比较器,可变频率振荡器(VFO),PLL会比较输入时钟相位与VFO产生的输出时钟之间的差别,并且通过这个差别来调整VFO产生的时钟频率。

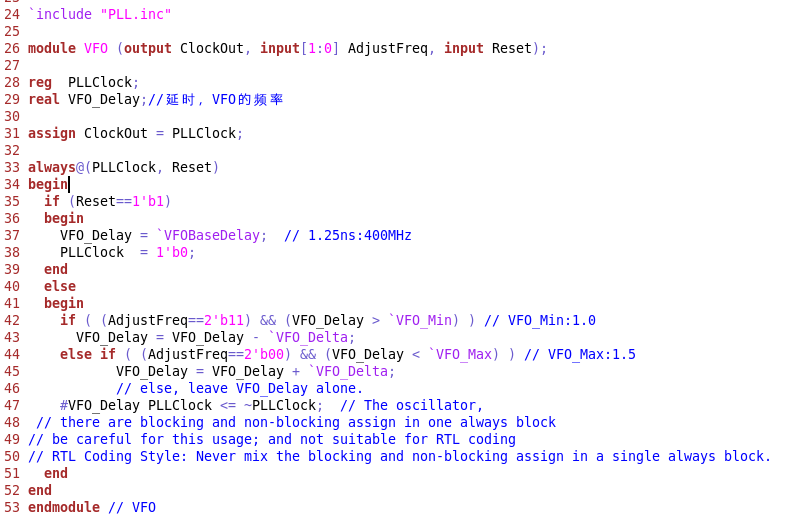

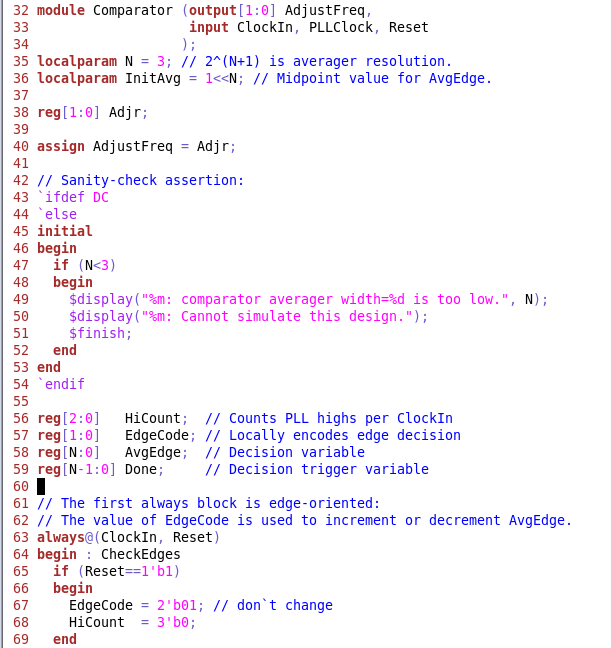

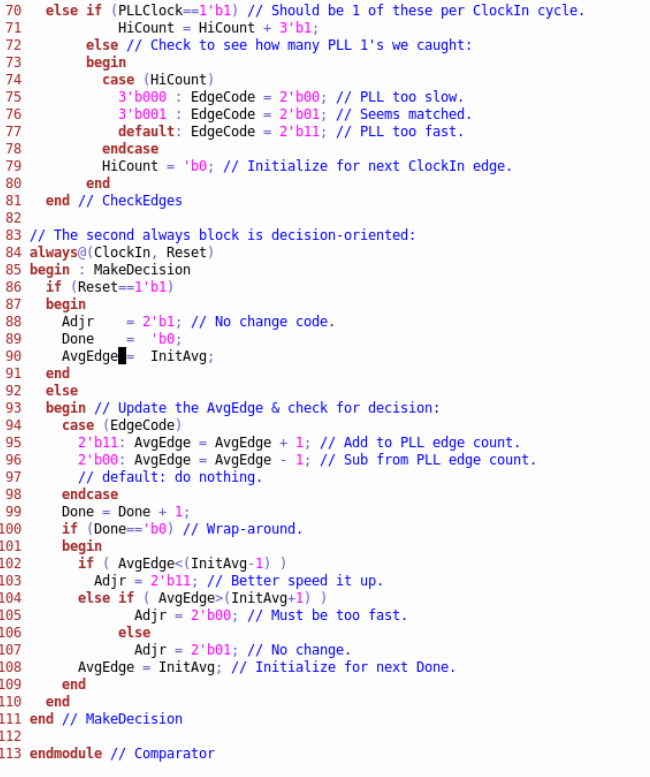

2:VFO代码

我们定义比较器给VFO加快频率的指令是2‘b11,减慢频率的指令是2’b00.

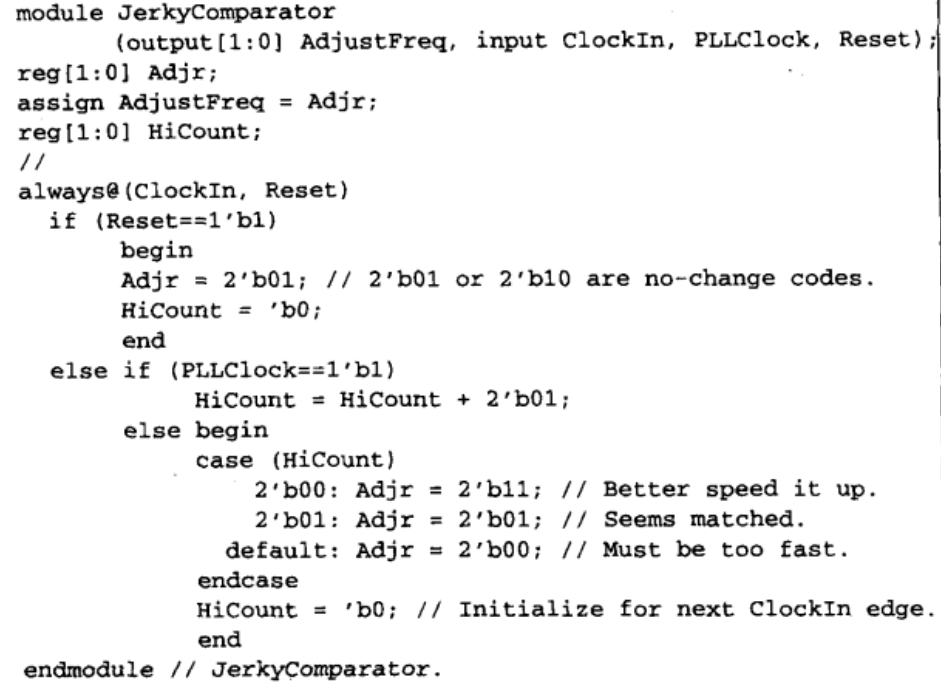

3:比较器设计

(A)方法一:用一个时钟来对另一个时钟的高电平宽度进行计数。如果每次PLLClock高电平时计数都为1,那么说明两个时钟是吻合的。

(B)对A改进

首先HiCount计数可能会溢出,技术值重新翻转到2‘b00。2’b00的作用是加快产生时钟频率,这使得频率的调整方向与真实情况正好相反。如果我们把HiCount的位宽由两比特扩展至3比特,可以解决这个问题。

接着,来解决调整精度的问题,这可以通过把高电平的计数值在多个时钟里求平均的办法来解决;当两个时钟同步时,这个计数值应该一直为1。(这点不明白)

4:顶层设计

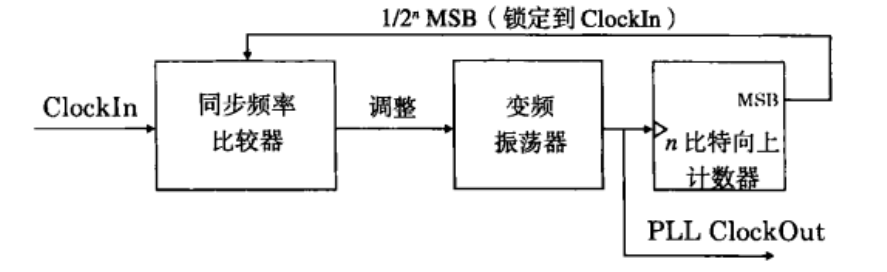

二:倍频PLL(以32倍频为例)

1:电路图

即在原1倍频的输出端加n比特向上计数器,如,32倍频时,每16个时钟,输出端输出一个时钟用于与输入时钟进行比较,从而起到倍频PLL。 32=2^5,因此计数器为5.

三:SerDes与PCI Express简介

1:基本概念

PCI是32比特的并行总线协议;

PCI Express用来取代PCI总线的新的串行总线协议

SerDes:串行/解串器

下面将完成一个符合PCI Express规范的串行/解串器(SerDes)的设计

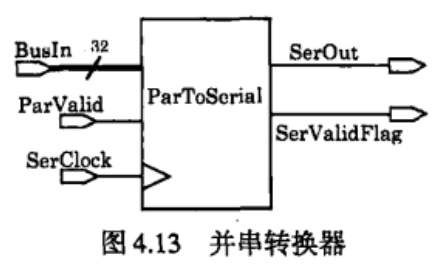

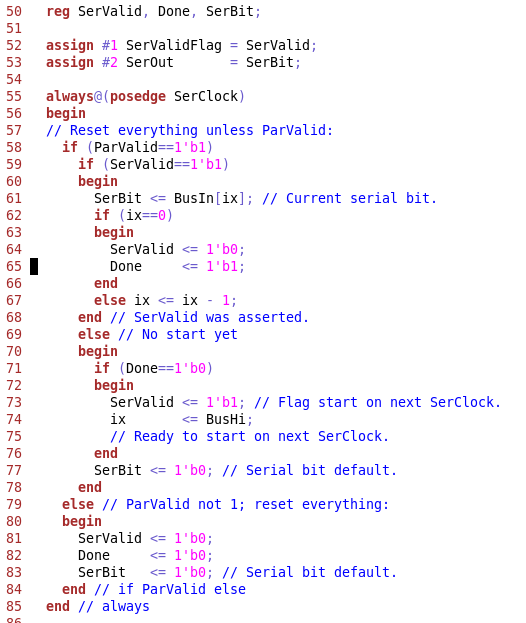

2:并串转换器模型

串行协议:每一个时钟发送一个比特,先发送MSB,同时把信号SerValidFlag拉高;当发送了LSB后,再把SerValidFlag拉低。

主要代码:ParValid=1,SarValid=1,然后将BusIn[ix]的值循环输出,最后SarValid拉低。(ParValid是仿真给的值)

3:串行帧编码器

数据串行输出之前有一定的帧格式,例如一个并行包32bit,串行输出,要在每个字节后加一个字节。如下:x代表数据,数据后面为一个字节的帧边界。