从今天开始终于要学习verilog语法啦~~学完我就得去整毕业设计了,,虽然verilog一直也学了点,但总觉得没什么系统性。打算用4月份把verilog学完,做点小实践,把毕业设计verilog部分大致过一遍。

一:数据类型,变量和基本运算符号

1:命名规则

大小写敏感,X代表未知状态,Z代表高阻态

2:数字的表达

<size>'<radix><value>,默认十进制

3:模块的新写法

module Andor(

output X,Y;

input A,B,C

)

.......

endmodule

4:数据类型

(1)register变量,存储数据,reg不是真正的flipflop,而是变量。

(2)vector变量,例如:wire[3:0] busA。

(3)integer/real,整型实型变量。

(4)time,my_time=$time ;//存放当前仿真时间

(5)数组array

reg var[-15:16];//32bit的regs,与reg [-15:16] var不同

reg [7:0] mem[0:1023] ;//1024 8-bit regs,看上去是二维的,但真正不是二维数组

mem[10] = 8'b10101010

不可一次取多个元素,如var[2:9]是不可以的,但reg [-15:16] var可以取var[2:9]。原因是数组的索引相当于地址,硬件无法一次读取多个地址。而vector索引相当于取位宽。不支持多维数组,如reg var[1:10] [1:100]是错误的。数组不能是real类型,如real r[1:10]是错误的。

(6) string

reg [8*13:1] string_val; //可存放13个字符,每个字符8位

string_val = "hello,verilog";//假如超过13个字符,则前面字符会被截断,采取低位先存。

5:操作符

(1)逻辑操作符 x&&0 = 0

(2)位操作符 ^(异或) ~^(同或)

(3)一目操作符

a = 4'b1001;

c = |a = 1|0|0|1 = 1

(4)移位操作符

(5)拼接操作符{}

但必须指定size,b = 3'b010; catz = {b,1};这是错误的,1必须指定size

(6)等号操作符

==/!==/===/!==

===/!==包括对xz的判断,若用==/!=对含有xz的进行判断,则返回x。

6:算术运算符

负数:reg [15:0] regA; regA = -4'd12;//存储的是2的16次方-12。

integer intA; intA = -12/3; //存储的是-4

二:赋值语句

(1)连续赋值语句

assign #del <id> = <expr>;//assign与wire配对

放在module里面,不能在过程块里(always,initial);多个assign语句是并发的,执行顺序不相关;

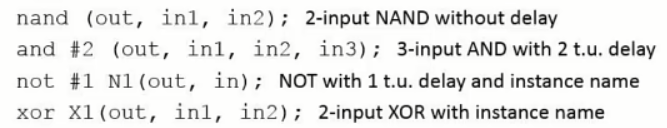

(2)门级建模

这些例化在module里,不能在procedure里面。

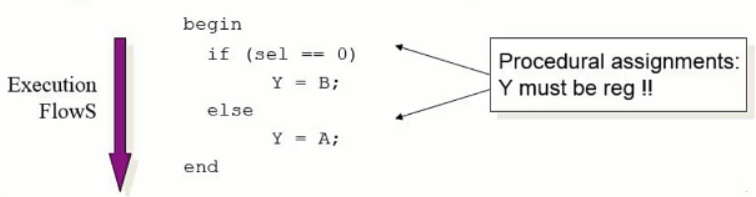

(3)行为级模块-过程块

过程块里的code是顺序执行的,begin..end;

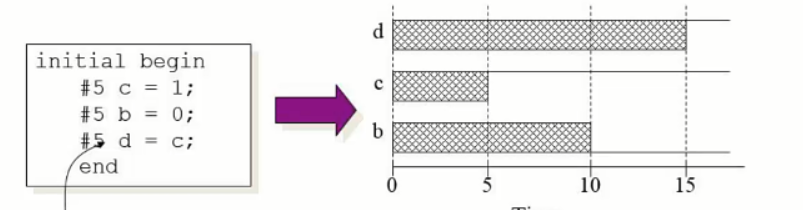

包括initial与always块,initial只在仿真为0时执行一遍,不可综合,不可构建电路;always块在仿真为0时执行,执行多次,可综合,可构建电路。

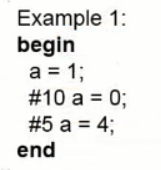

(4)块语句block

sequential:begin...end 顺序执行

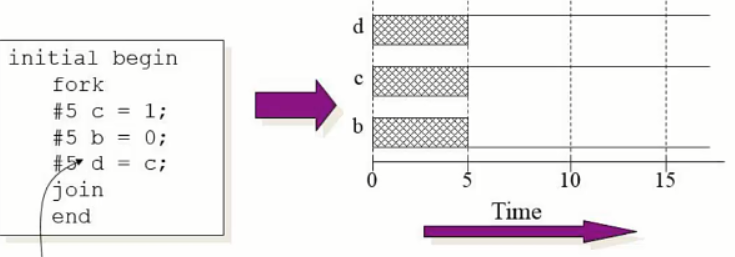

parallel: fork...join 并行执行,不可综合,不可构建电路。

begin...end与fork...join可相互嵌套。

(5)always块

assign不可放在always语句里,always左侧变量必须是reg型。

always @(敏感信号) ,敏感信号可以是电平信号也可以是触发沿信号。

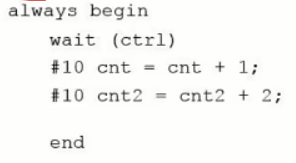

(6)wait(expr)

wait不可综合,用于仿真。

三:条件语句循环语句

(1)if语句,else语句要充分考虑多个情况,不然会形成latch。可综合

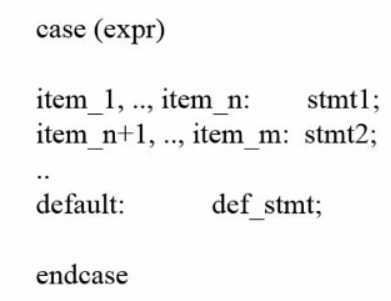

(2)case,可综合

(3)for循环,是否可综合取决于变量的循环是不是固定的

(4)while() begin ...end 不可综合

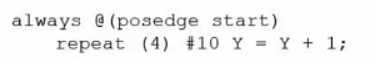

(5)repeat(times) stmt;不可综合

(6)forever 不可综合

forever #10 clk = ~clk; //对时钟建模,生成clock,always也可产生时钟,但不专业。我们推荐用forever产生时钟。