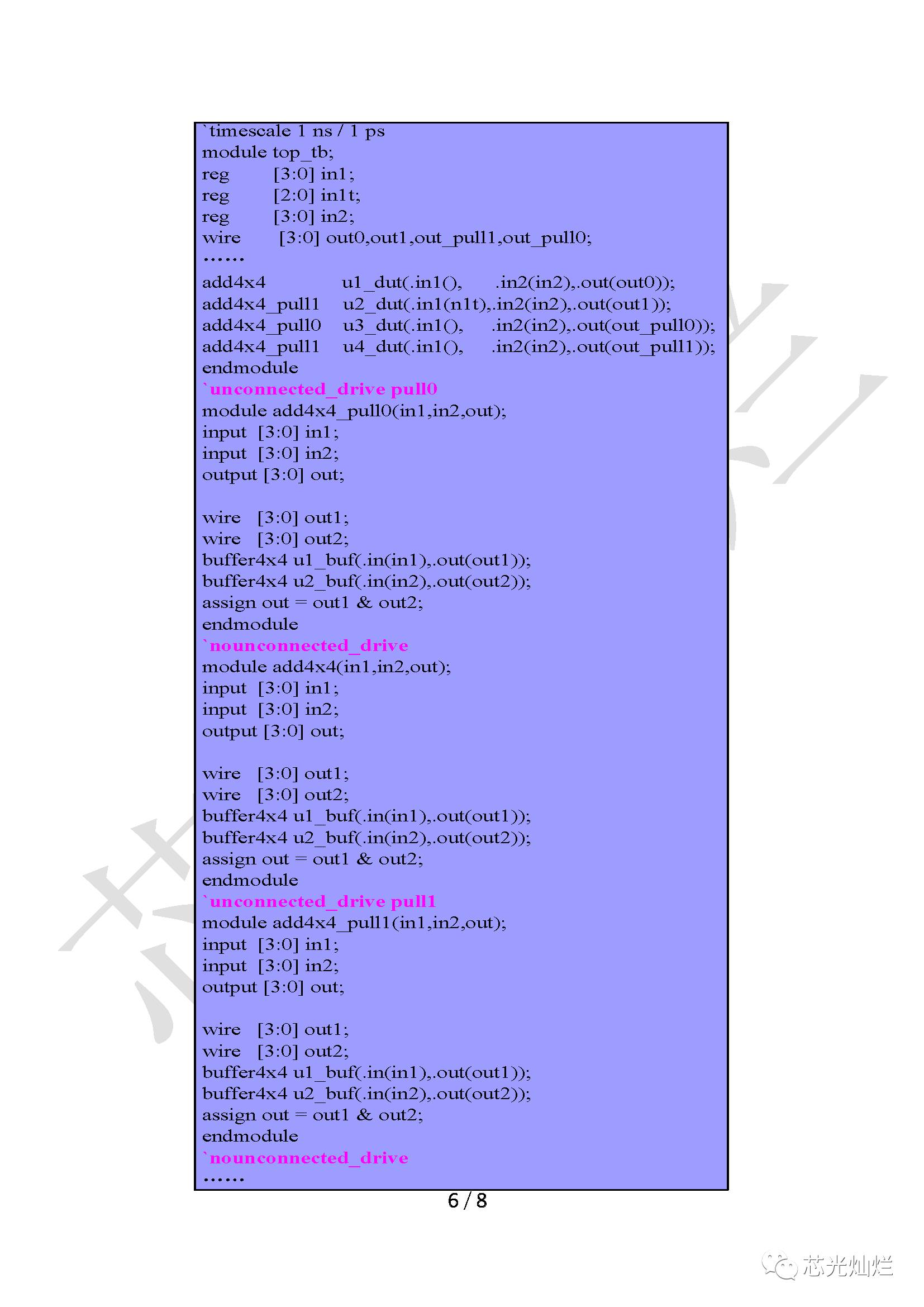

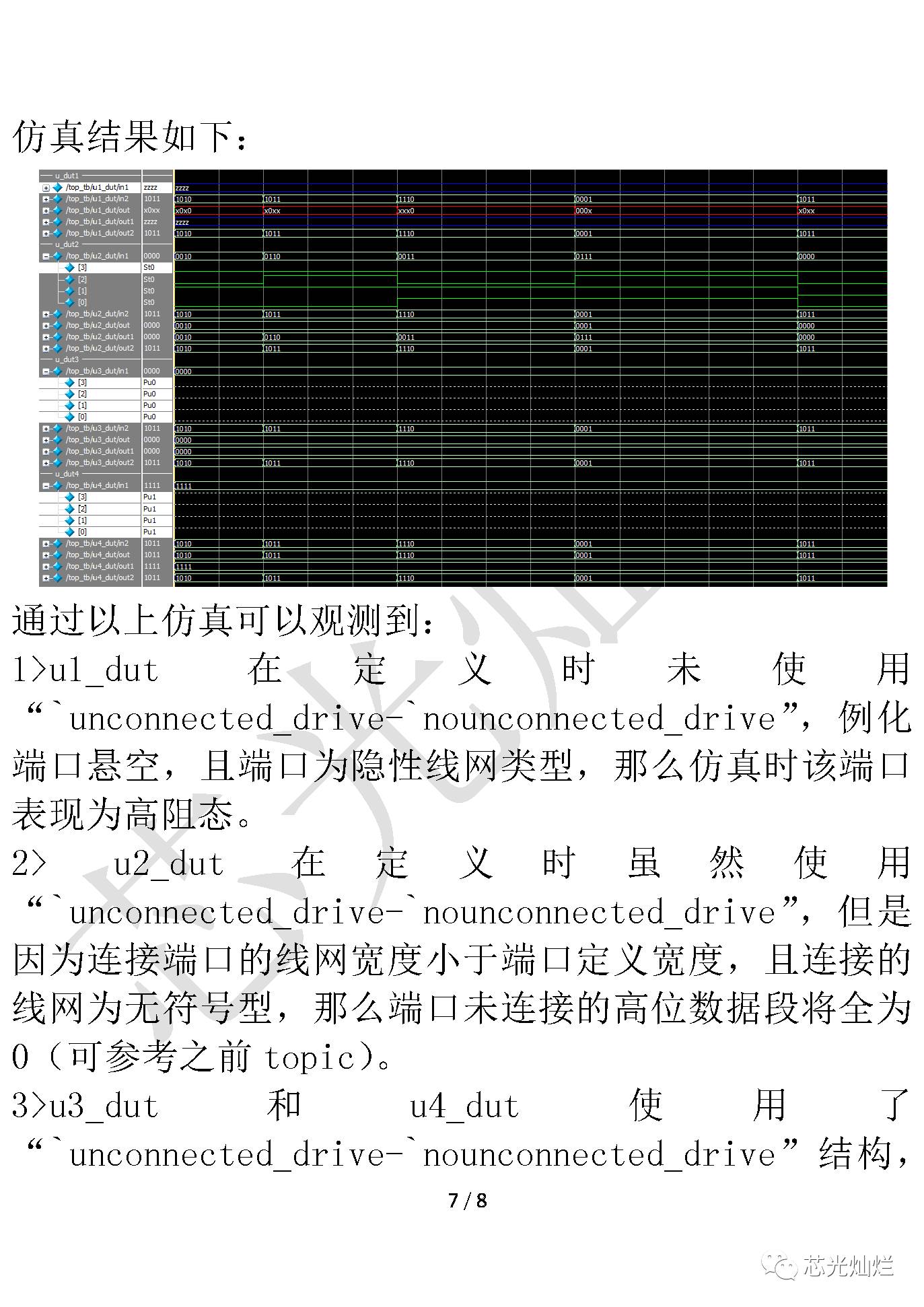

在Verilog中,对于未指定线网类型的隐性线网默认的类型为wire,如果没有对线网进行上拉或者下拉操作,那么其状态为高阻态,即“Z”。对于特定设计在后端实现时会对相应的端口进行上下拉操作,为了保持这种特性,除了显示声明线网类型为tri0或者tri1等外,还可以通过编译命令实现端口上下拉。本文将对通过编译命令实现线网类型的设置进行示例。

1.`default_nettype

格式:`default_nettypenet_type

其中net_type可以是:wire、tri1、tri0、wand、triand、wor、trior、trireg、none等。

该命令用于隐性线网指定默认线网类型。特别是在端口定义中,如果没有显示指定线网类型,那么线网的类型为wire(默认值)或者`default_nettype指定的线网类型。

例如:

`default_nettype tri1

该例说明缺省的线网为三态上拉型。

在使用该命令时需要注意以下几点:

- 该命令用于指定模块定义之外,即“module-endmodule”外;

- 同时指定多条该命令,生效命令采取就近原则,即最后一条该命令将对后续的设计起作用;

- 当`default_nettype指定的net_type为none,那么所有线网必须显示声明;

- `resetalll命令后的隐性线网类型为wire,不受`default_nettype指定的影响,除非`resetall之后再次使用`default_nettype指定类型;

【示例】

更多资讯,请关注个人公众号:芯光灿烂