Coverage Overview

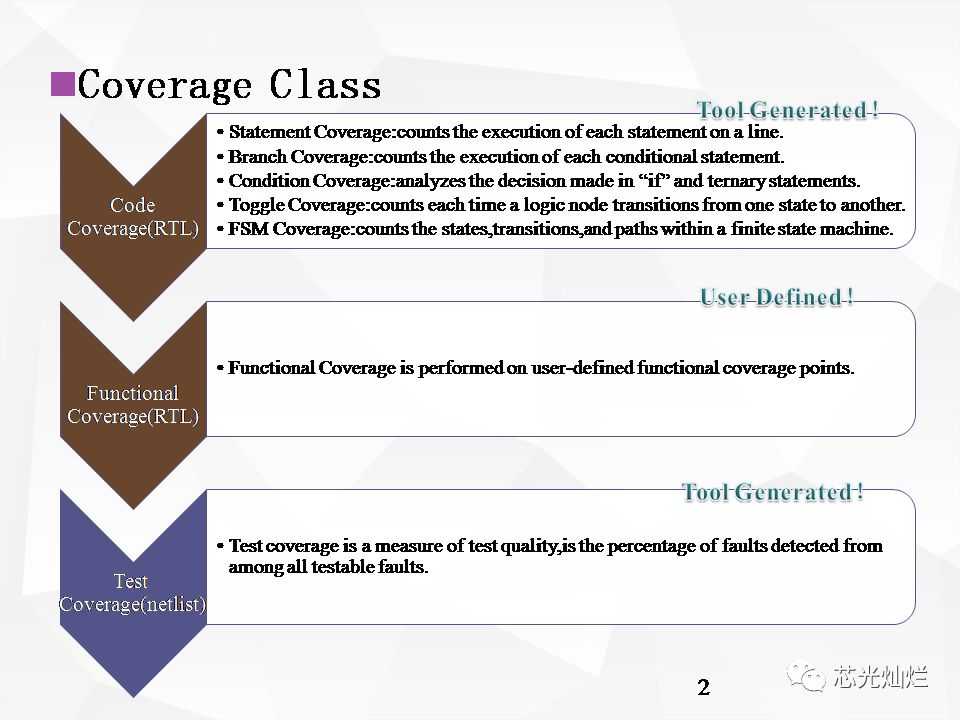

- 随着芯片规模越来越大,集成的功能越来越多,一次性流片费用的增加,市场竞争的日益激烈,如何在验证和测试中解决判断验证充分性和完备性的问题逐步成为业界验证工作的热门话题。

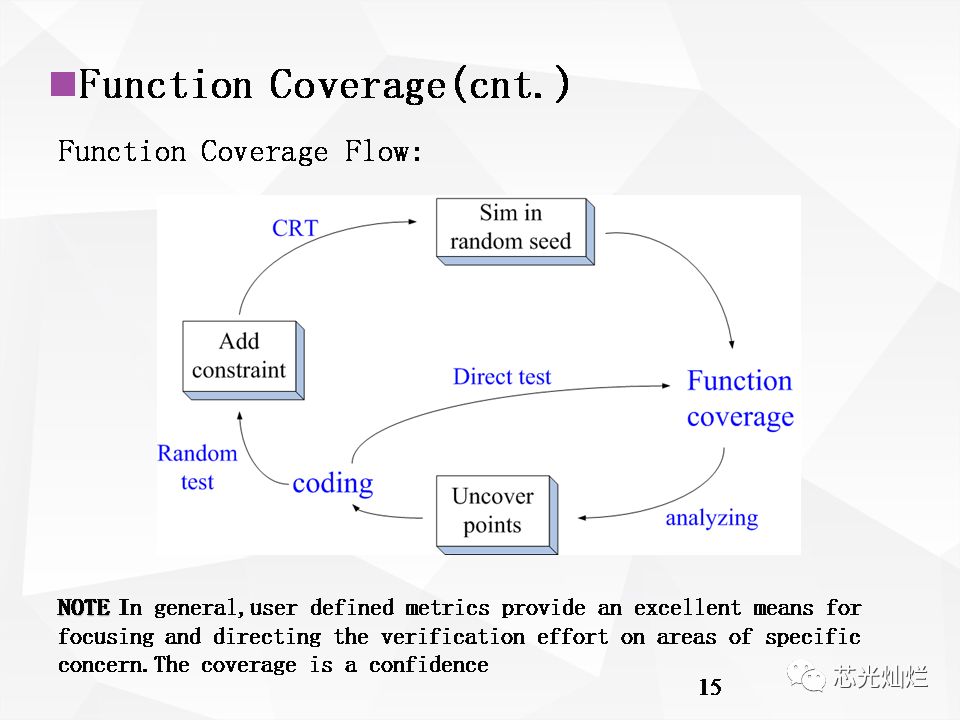

- 并且伴随验证技术的进一步发展,验证技术也发生了巨大的变化,覆盖率作为其中一种判断验证充分性的手段已经被广泛的应用在集成电路的设计验证工作中。

- 本文将主要介绍设计验证工作中经常遇到的覆盖率的基本概念,希望对需要的朋友有所帮助。

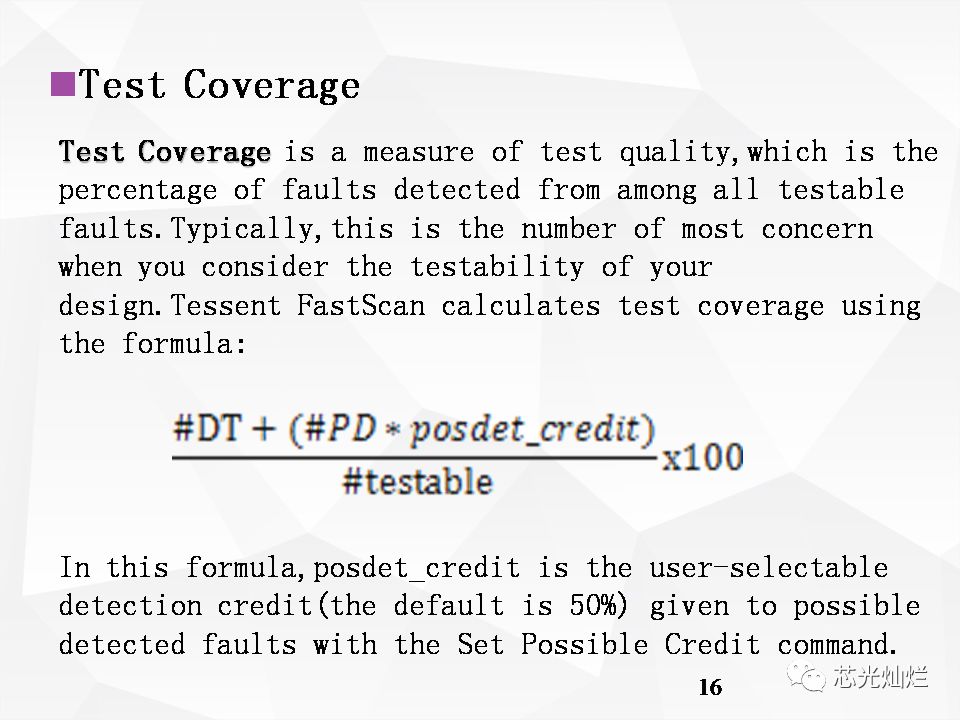

Test Coverage

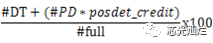

- Fault Coverage consists of thepercentage of fault detected from among all faults that the test pattern settests-treating untestable faults the same as undetected faults.Tessent FastScancalculates test coverage using the formula:

NOTE

- DT(detected):all faults that the ATPGprocess identifies as detected.

- PD(possible-detected):all faults thatfault simulation identifies as possible-detected but not hard detected.

- TE(Testable):all those faults thatcannot be proven untestable.

- full:testable and un-testable

Conclusion

The 100% coverage does not necessarily indicate design correctness,or even that all bugs have been observed.The 100% coverage is a high degree of confidence that all important bugs have been found.On the other hand,different EDA tools may have different coverage sets,so you could get more information and examples from the tools’ help doc.Atlast,hope it can lend you a hand and pls scan the next page QR for moreinformation and materials.