关于path and path group

- 本文针对常见的path和pathgroup 问题,做深入的分析和总结

- path 和path group 属于时序设计中的基本问题,属于必须掌握的知识点

- 希望对大家的面试和工作有帮助,如有兴趣,可以添加微信号“xgcl_wei”进行更进一步的交流沟通学习

Design and library objects

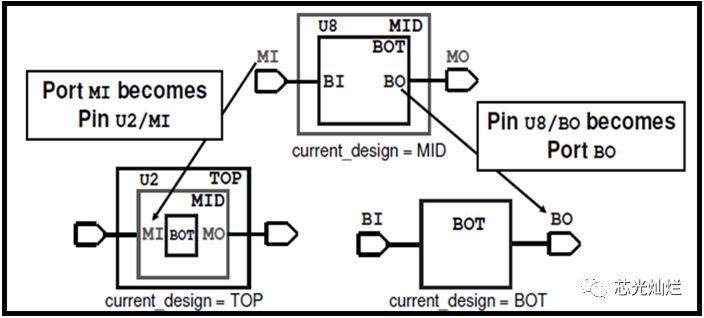

- Ports Versus Pins

- ‘Ports’ are the inputs and outputs of the current design

- ‘Pins’ are the inputs and outputs of any cell that isinstantiated in the current design

PathDelay

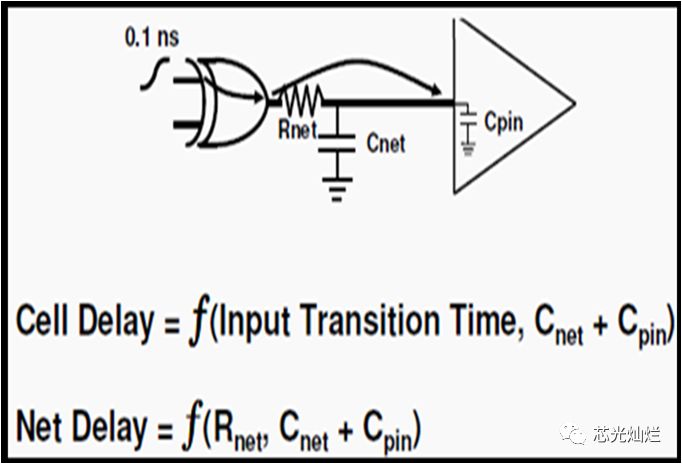

- Path Delays are Based on Cell + Net Delays

- PathDelay

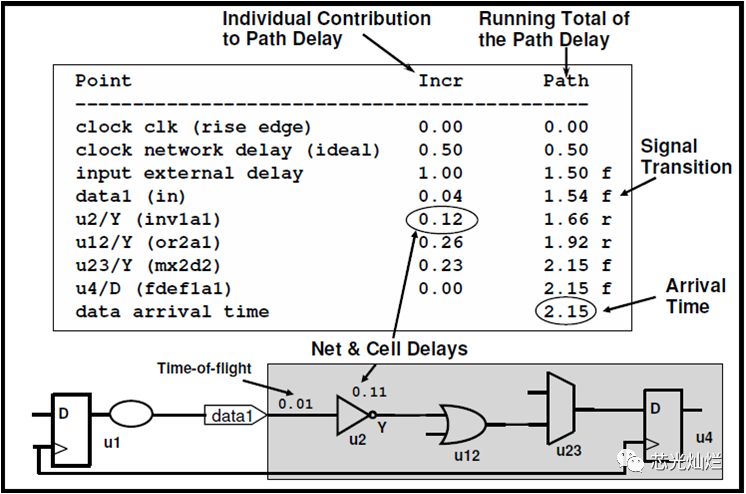

- Path delay section

PathDelay

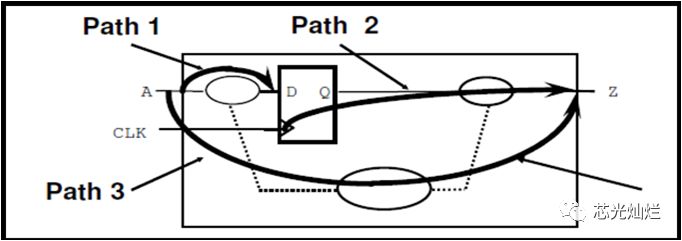

- Define setup timing constraints for all paths within asequential design

- All input logic paths (startingat input ports)

- The internal (register to register) paths

- All output paths (ending at output ports)

- Starting at input ports and ending at output ports

-

Static timing analysis Fundamentals

- Static Timing Analysis can determine if a circuit meetstiming constraints without dynamic simulation

- This involves three main steps:

- design is broken down into timingpaths

- The delay of each path is calculated

- All path delays are checked against timing constraints

Static timing analysis Fundamentals

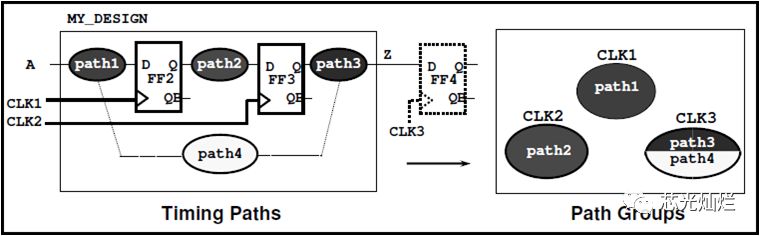

- Grouping of Timing Paths into Path Groups

- report_path_group

- Paths are grouped by the clocks controlling their endpoints

Static timing analysis Fundamentals

- Timing Paths and Group Paths

- How many timing paths are there?

- How many path groups are there?

Path and path group总结

- Path and path group 属于时序中的基础问题

- Path group 要尽量做到最简化

- 一定要学会画波形图和时序图,正确区分path和pathgroup,做到全覆盖