目录

FloorPlan 基础知识

1、FloorPlan的内容?

规划芯片的面积和形状,

创建Physical-only cell,摆放IO

摆放Macro

做Power plan,包括创建电压域、创建power ring和power mesh,进行一些电源预布线,包括标准单元的Power Rail及IO

BNN项目的一些问题

1、Power ring使用哪几层金属?

使用M8(H)和M7(V),线宽4.5um,间距1.1um

还使用了M6(H)和M5(V),线宽4.5um,间距1.1um

2、Power mesh怎么做的?

TOP_PG 区域,TOP_MESH_HIGH: 使用M8和M7,线宽4.5um,间距1.1um,VDD_top_net、VSS_top_net、VDD_core_net

TOP_PG 区域,TOP_MESH_LOW:使用M6和M5,线宽0.28um,间距2.52um, VDD_top_net、VSS_top_net,在做这一个power mesh时需要指定VDD_top_net的blockage,避免其延伸到CORE_PG区域,但是VSS_top_net不需要

CORE_PG区域,CORE_MESH_LOW:使用M6和M5,线宽0.28um,间距2.52um, VDD_core_net,这一个power mesh只需要布VDD_core_net,因为在上一个TOP_MESH_LOW中已经布了VSS_top_net

Memory Block

1、指定block的宽和高,创建floorplan

create_floorplan -control_type width_and_height -core_width 120 -core_height 60

2、在block四周创建placement blockage

create_placement_blockage -bbox {0.00 0.00 5.00 60.00} -type hard -name placeblock_left

hard placement blockage: 不允许摆放任何std cell,inv,buffer,用来解决congestion

soft placement blockage: 在coarse placement阶段不允许摆放任何标准单元或者hard macros,但是在optimization或legalization阶段允许摆放。

partial placement blockage:可以控制某些模块中std cell的摆放,解决cell density问题

routing blockage:指导某些金属层的走线

HALO(keepout margin):跟随在macro周围,不允许std cell的摆放,只允许inv和buffer摆放

3、添加一些physical only单元

http://www.360doc.com/content/18/0807/22/26654031_776466562.shtml

add_end_cap

add_tap_cell_array

endcap cell: 主要加在std row的两端,以及memory或者其他block的包边,作用是确保每个nwell都是nwell enclosed

tap cell:将衬底接到电源和地网络,避免衬底悬空,防止latch up

decap cell:去耦单元,作用是在瞬态电流增大,电压下降时为电路补充电流以保持电源和地线之间的电压稳定,防止电源线的电压降和地线电压的升高

filler cells:来填充I/O单元和I/O单元之间的间隙,作用主要是把扩散层连接起来满足DRC

4、derive_pg

create_net VDD_net -power

derive_pg_connection -power_net VDD_net -power_pin VDD -cells [get_cells -all] -reconnect

5、创建scenario

用于setup:

create_scenario func_wcl_ud_cworst

set_scenario_options -setup true -hold false

set_tlu_plus_files ……

set_operating_conditions …… 设置最坏工作条件

set_timing_derate -early -cell_delay -clock 0.99

set_timing_derate -early -net_delay -clock 0.99

set_timing_derate -late -cell_delay -clock 1.01

set_timing_derate -late -net_delay -clock 1.01

set_timing_derate -late -cell_delay -data 1.01

set_timing_derate -late -net_delay -data 1.01

时钟路径会有-early和-late两种,捕获时钟路径用-early,发射时钟路径用-late

数据路径只有-late

用于hold的scenario创建与此类似

之后再激活某个scenario:set_active_scenarios ……

6、创建power plan,进行电源布线

创建power ring

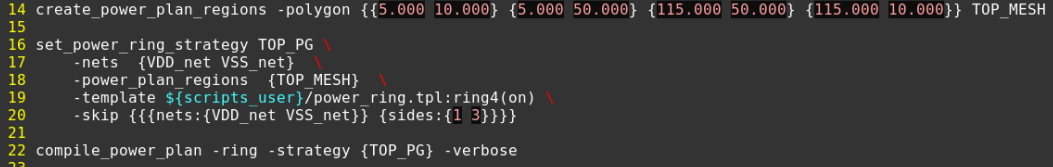

先指定power plan的区域:create_power_plan_regions -polygon {{坐标点1} {2} {3} {4}} region_name

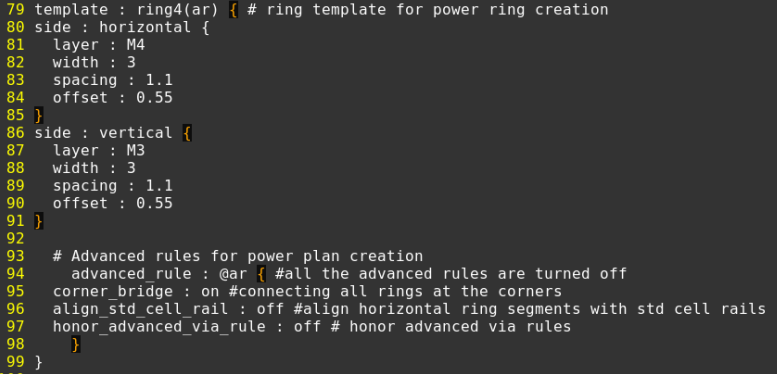

再设置strategy:set_power_ring_strategy your_strategy …… ,这一步会指定一个power_ring的template,在template里会指定水平和垂直方向的布线金属层、线宽、线间距和offset等

对strategy进行编译:compile_power_plan -ring -strategy {your_strategy} -verbose

左-上-右-下:side1-side2-side3-side4,引脚顺序为从下至上,从左至右, 上面脚本-skip选项表示不在左右2边打ring

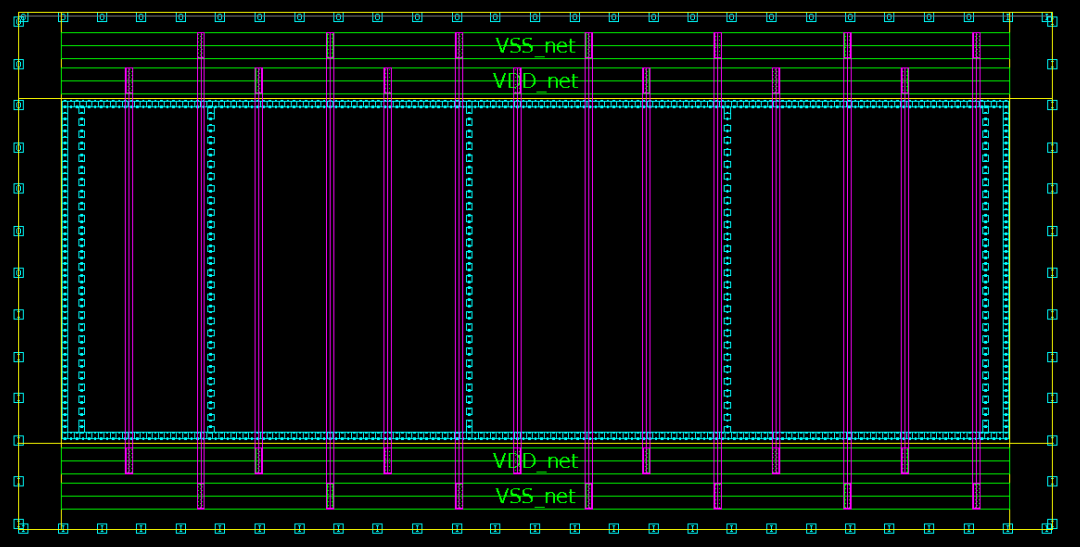

创建power strap

在以上例子中,power ring使用了金属层M4,上下VDD_net和VSS_net各1条,Power strap使用了金属层M5,VDD_net和VSS_net交错排布,端头与power ring相连

7、设置通孔规则

set_preroute_advanced_via_rule

8、插入filler,置预布线的金属层,并对标准单元进行预布线,再移除插入的filler

insert_stdcell_filler ……

set_preroute_drc_strategy -min_layer M2 -max_layer M5

preroute_standard_cells -nets {VSS_net} ……

preroute_standard_cells -nets {VDD_net} ……

remove_stdcell_filler -stdcell

以上几步的作用是将标准单元的power rail连接到power strap上