目录

基本步骤

1、指定逻辑库(.db)

target_library

link_library

包含所有std cell的时序和功能信息,提供hard macro的时序信息,定义DRC规则

2、创建设计库(.mdb)

create_mw_lib design_library -open -technology *.tf -mw_reference_library "./libs/sc ./libs/macros ./libs/io"

tf文件:包含每层的序号和名字,每层的物理和电气特性,每层的设计规则,电气单位等

物理参考库:包含std,macro和pad cell的物理信息,比如pin的位置、方向、层和形状等

之所以称为reference库,是因为ICC只是创建pointer指向它们,而不load它们

3、读入网表创建CEL

read_verilog ./netlist/design.v

current_design

uniquify

save_mw_cel -as design

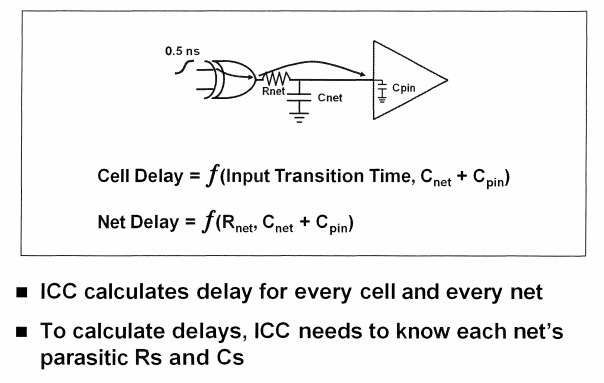

4、指定TLU+ 寄生RC模型文件

set_tlu_plus_files

-max_tluplus ./libs/abc_max.tlup

-min_tluplus ./libs/abc_min.tlup

-tech2itf_map ./libs/abc.map

5、检查库

set_check_library_options -all

check_library

check_tlu_plus_files

检查逻辑库和物理库之间的一致性:missing和mismatch

在物理库内检查:Missing CEL(layout)和FRAM(abstract),多个参考库间的重复cell name

6、验证逻辑库已经导入

list_libs

7、定义逻辑的Power和Ground连接

derive_pg_connection -power_net PWR -power_pin VDD

-ground_net GND -ground_pin VSS

derive_pg_connection -power_net PWR -power -ground_net GND

-tie

check_mv_design -power_nets

8、应用和检查时序约束

read_sdc ./cons/orca.sdc

check_timing

report_timing_requirements

report_disable_timing

report_case_analysis

9、确保合适的时钟树建模

report_clock

report_clock -skew

包括:clock_uncertainty, clock_latency, clock_transition