https://blog.csdn.net/vivid117/article/details/102171881 用? : 语法写状态转移更加简洁

1、检测数字序列11011

2、代码

`timescale 1ns / 1ps module digit_sequence_detect( input clk, input rstn, input data_in, output detect ); localparam S0=3'd0,S1=3'd1,S2=3'd2,S3=3'd3,S4=3'd4,S5=3'd5; reg [2:0] state,next_state; reg detect_reg; always @(posedge clk or negedge rstn) begin if(!rstn) state <= 3'd0; else state <= next_state; end always @(*) begin case(state) S0:if(data_in==1'b1) next_state = S1; else next_state = S0; S1:if(data_in==1'b1) next_state = S2; else next_state = S0; S2:if(data_in==1'b0) next_state = S3; else next_state=S2; S3:if(data_in==1'b1) next_state = S4; else next_state = S0; S4:if(data_in==1'b1) next_state = S5; else next_state = S0; S5:if(data_in==1'b1) next_state = S1; else next_state = S0; default:next_state = S0; endcase end always @(*) begin if(state==S5) detect_reg = 1'b1; else detect_reg = 1'b0; end assign detect = detect_reg; endmodule

3、测试激励

`timescale 1ns / 1ps module digit_sequence_detect_tb; // Inputs reg clk; reg rstn; reg data_in; // Outputs wire detect; reg [15:0] digit_sequence; integer i; // Instantiate the Unit Under Test (UUT) digit_sequence_detect uut ( .clk(clk), .rstn(rstn), .data_in(data_in), .detect(detect) ); initial begin // Initialize Inputs clk = 0; rstn = 0; data_in = 0; digit_sequence = 16'b11011011_00111011; // Wait 100 ns for global reset to finish #100; rstn = 1; for(i=15;i>=0;i=i-1) begin @(negedge clk) begin data_in = digit_sequence[i]; end end // Add stimulus here end always #20 clk = ~clk; endmodule

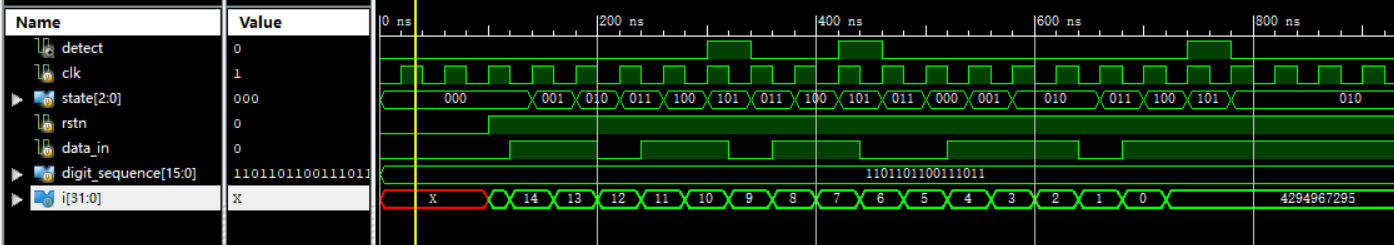

4、波形

5、连续检测代码只需更改S5状态的跳转逻辑

S5:if(data_in==1'b1) next_state = S2; //连续检测 else next_state = S3;

波形: