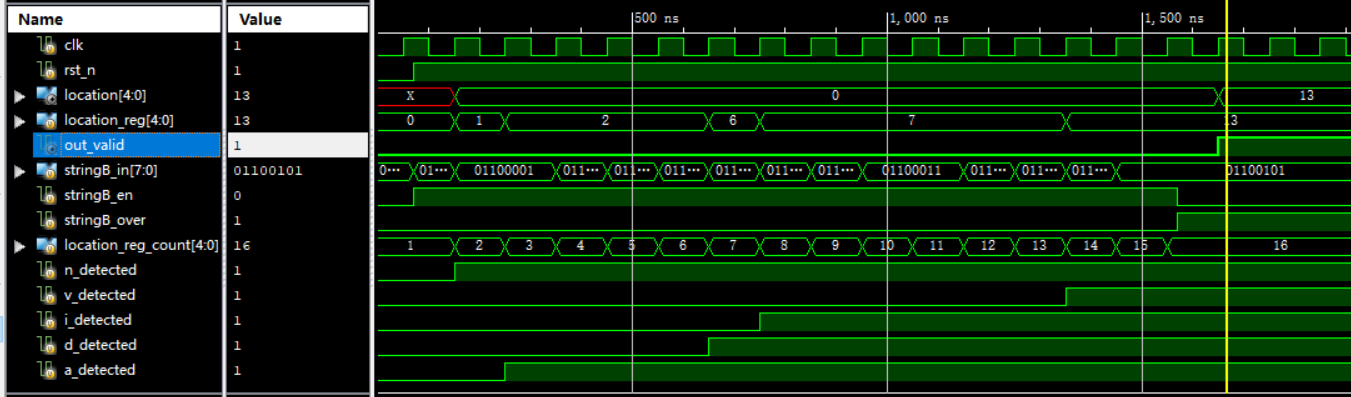

1、原题

2、代码

module sequence_detect( input clk, input rst_n, input [7:0] stringB_in, input stringB_en , input stringB_over , output reg [4:0] location, output reg out_valid ); // 输入字符串计数 reg [4:0] location_reg_count; always @ (posedge clk or negedge rst_n) begin if(!rst_n) location_reg_count <= 5'd1; // 根据示例索引从1开始 else if(stringB_en == 1'b1 && stringB_over == 1'b0) begin location_reg_count <= location_reg_count+1; end end // 检测标志位 reg n_detected,v_detected,i_detected,d_detected,a_detected; // 标记字母是否已经被检测到了,若是,后面不再检测 always @(posedge clk or negedge rst_n) begin if(!rst_n) begin n_detected <= 1'b0; v_detected <= 1'b0; i_detected <= 1'b0; d_detected <= 1'b0; a_detected <= 1'b0; end else if(stringB_en == 1'b1 && stringB_over == 1'b0) begin case(stringB_in) "n": n_detected <= 1'b1; "v": v_detected <= 1'b1; "i": i_detected <= 1'b1; "d": d_detected <= 1'b1; "a": a_detected <= 1'b1; endcase end else begin n_detected <= n_detected; v_detected <= v_detected; i_detected <= i_detected; d_detected <= d_detected; a_detected <= a_detected; end end // 检测 reg [4:0] location_reg; always @ (posedge clk or negedge rst_n) begin if(!rst_n) location_reg <= 0; else if (stringB_en == 1'b1 && stringB_over == 1'b0 ) begin if((stringB_in == "n" && (!n_detected)) || (stringB_in == "v" && (!v_detected)) || (stringB_in == "i"&& (!i_detected)) ||(stringB_in == "d"&& (!d_detected)) || (stringB_in == "a"&& (!a_detected))) begin location_reg <= location_reg_count; end else begin location_reg <= location_reg; end end end // 输出 always @ (posedge clk or negedge rst_n) begin if(!rst_n) out_valid <= 0; else if (stringB_over == 1'b1 ) begin location <= location_reg ; out_valid <= 1'b1; end else begin location <= 0 ; out_valid <= 1'b0; end end endmodule

3、测试激励

`timescale 1ns / 1ps //////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date: 21:26:54 03/04/2020 // Design Name: sequence_detect // Module Name: D:/MyFiles/code_and_projects/ISE/projects/for_work/sequence_detect_tb.v // Project Name: for_work // Target Device: // Tool versions: // Description: // // Verilog Test Fixture created by ISE for module: sequence_detect // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // //////////////////////////////////////////////////////////////////////////////// module sequence_detect_tb; // Inputs reg clk; reg rst_n; reg [7:0] stringB_in; reg stringB_en; reg stringB_over; // Outputs wire [4:0] location; wire out_valid; // Instantiate the Unit Under Test (UUT) sequence_detect uut ( .clk(clk), .rst_n(rst_n), .stringB_in(stringB_in), .stringB_en(stringB_en), .stringB_over(stringB_over), .location(location), .out_valid(out_valid) ); initial begin // Initialize Inputs clk = 0; rst_n = 0; stringB_in = 0; stringB_en = 0; stringB_over = 0; // Wait 100 ns for global reset to finish #70; rst_n = 1; stringB_en = 1; stringB_in = "n"; @(posedge clk); stringB_in = "a"; @(posedge clk); stringB_in = "a"; @(posedge clk); stringB_in = "b"; @(posedge clk); stringB_in = "c"; @(posedge clk); stringB_in = "d"; @(posedge clk); stringB_in = "i"; @(posedge clk); stringB_in = "a"; @(posedge clk); stringB_in = "i"; @(posedge clk); stringB_in = "c"; @(posedge clk); stringB_in = "c"; @(posedge clk); stringB_in = "b"; @(posedge clk); stringB_in = "v"; @(posedge clk); stringB_in = "d"; @(posedge clk); stringB_in = "e"; @(posedge clk); #20; stringB_en = 0; stringB_over = 1; // Add stimulus here end always #50 clk = !clk; endmodule

4、输出波形